Фазовый различитель

Иллюстрации

Показать всеРеферат

ЕМтт}}Л-, н

ОписАние

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (} 1}798620

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к авт, свид-ву— (22)Заявлено 06.04.79(2!) 2747596/18-21 с присоединением заявки,% (23) Приоритет

Опубликовано 23.01.81. Бюллетень J% 3

Дата Опубликования описания 26.01.81 (51) М. Кл.

G 01 R 25/00//

Н 03 )3 3/06

Гввударстввнный квмнтвт

СССР ао делам нзобретеннй н открытнй (53) УД К 62 1.31 7.. 77(088.8) (72) Автор изобретения!

3. !3. Бессонов (71);Заявитель! !олтавский инженерно-строительный институт (54) ФЛЗО!ЗЫЙ РАЗХ!ИЧИТЕЛЬ

Изобретение относится к фазоизмерительной технике и может быгь использовано при создании фазомегров с расширенным угловым диапазоном и систем фазовой автопоцстройки частоты с боль}пой. полосой схватывания.

Известен фазовый различитель, содержащий фазовые детекторы (1).

Нецостатком его является ограниченный диапазон однозначности амплитуднофазовой характеристики.

Известен также фазовый различитель, содержащий последовательно соединенные схему дифференцирования, логический элеIS мент с инвертором и коммутатор, а также запоминающее устройство с умножитепем на, два, первый вход которого одновременно подключен ко входам схемы дифференцирования, сумматора и к выходу фазового детектора, второй вход подключен клогическому элементу с инвертором, а выход через второй вход коммутатора — ко входу сумматора, выход которого через схему сравнения соецинен с третьим входом запоми}наюшего устройства с умножителем на "два" (21.

Однако известный фазовый различитель не позволяет значительно увеличить полосу схватывания из-за того, что амплитудно-фазовая характеристика формируется из разнополярных участков амплитудно-фазовой характеристики входящего в него фазового детектора, А это }}риводит к гому, что прирост постоянной составляющей напряжения на выходе фазового различителя замедлен из-за того, что, например, положительная полуволна напряжения на выходе фазового различигеля формируется как из положительных, так и из отрицательных полуволн напряжения фазового детектора, первая из них (например, положительная полуволна) увеличивает постоянную .составляющую, а вторая (отрицательная), наоборот, уменьшает постоянную составляющую.

Ддя эффективного прироста постоянной составляющей напряжения фазового

3 различителя необходимо, чтобы положительная полуволна напряжения на его выходе была сформирована только из положительных полуволн напряжения фазового детектора, а отрицательная полуволна напряжения — только из отрицательных полуволн фазового детектора.

Цель изобретения — увеличение полосы схватывания при использовании в системах автоподстройки частоты.

Укаэанная цель достигается за счет того, что в фазовый различитель, содержащий фазовый детектор, который через блок дифференцирования соецинен с логическим элементом с инвертором, первый выход которого соединен с коммутатором, а второй выход — с первым входом запо- минающего элемента, выходы которого соецинены с коммутатором второй вход запоминающего элемента через сумматор и -блой сравнения соединен со своим третьим входом, введены дополнительные блок дифференцирования, коммутатор и фазовый детектор, вход которого соецинен со входом основного фазового детектора, а выход через дополнительный блок дифференцирования соединен со входом логического элемента с инвертором, выход которого соединен с одним входом дополнительного, коммутатора, другие входы которого соединены с выходами фазовых детекторов, а выход соецинен со вторым входом запоминающего элемента.

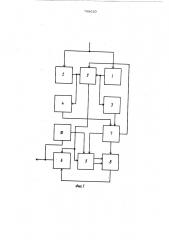

На фиг. 1 представлена функциональная схема фазового разпичителя; на фиг. 2графики, поясняюшие его работу.

Фазовый различитель состоит иэ фазовых детекторов 1 и 2, двух блоков 3 и 4 дифференцирования, запоминаюшего элемента 5, сумматора 6, логичес кого элемента 7 с инвертором, двух коммутаторов 8 и 9 и блока 10 сравнения. .Фазовые детекторы 1 и 2, должны иметь однозначные в интервале + амплитудно-фазовые характеристики, сдвинутые на E и, в частном случае, линейные.

Пусть при включении устройства раз. ность фаз на входе первого фазового детектора положительна l 0«® I и возрастает (фиг. 2а).

При превышении выходным напряжением фазового детектора 1 заданного уровня логический элемент 7 подключает знпоминаюший элемент 5 на выход второго коммутатора 9, ко входам которого подключены выходы Фазовых детей up-

1 и 2. Логический элемент 7 при отсутствии управляюших импульсов с выходов блоков дифференцирования 3 и 4, т.е. цо начала работы, всегда подключает к

cyMMaropy 6 и запоминающему элементу

5 выход фазового детектора 1. При происходит скачок выходного напряжения фазового детектора 1 в область отрицательных значений, на выхо-10 де блока 3 появляется импульс отрицательной полярности. Этот импульс с помощью логического элемента 7 подключает через коммутатор 9 к первому входу сумматора 6 выход фазового детектора 2, а

1s ко второму входу сумматора 6 через коммутатор 8 выход запоминаюшего элемента 5, напряжение которого равно максимальному значению напряжения при

Ч = Я на выходе фазового детектора 1 рр (на фиг. 2в это пунктирная линия,на интервале й: < Ч < 27 )

При дальнейшем увеличении разности фаз до Ч = 21 выходное напряжение различителя фазы на выходе сумматора 6

25 изменяется от максимального значения напряжения на выходе фазового детектора 1 до удвоенного его значения.

При 4 = 2 Г происходит скачок выходного напряжения фазового детектора

3р 2, на выходе блока 4 появляется импульс отрицательной полярности, который с помощью логического элемента 7 подключает через коммутатор 9 к первому входу сумматора 6 выход фазового детектора 1, а ко второму входу сумматора 6 через коммутатор 8 выход запоминаюшего элемента 5, напряжение которого равно удвоенному максимальному значению напряжения первого фазового детек р тора при P = +C . Этот же импульс подключает к выходу блока 3 инвертор, который находится в логическом элементе 7, подготавливая тем самым переключение полярности напряжения с выхода элемента 5 на выход сумматора 6 через коммутатор 8.

Второй отрицательный импульс с блока 3, который формируется при разности фаэ Ч = 3, переключает полярность напряжения запоминаюшего элемента 5, которое подается на. сумматор 6 через коммутатор 8 (фиг. 2в).

Второй отрицательный импульс с блока 4 (при Ч = 4Г, фиг. 2б) с помощью

55 логического элемента 7 подключает через .коммутатор 9 к первому входу сумматора 6 выход фазового детектора 2, а ко второму входу сумматора 6 через коммутатор 8 выход запоминающего элемента 5, тЫвания. в системах фазовой автоподстройки частоты.

Фазовый различитель, содержащий фа зовый детектор, который через блок дифференцирования соединен с логическим элементом с инвертором, первый выход ,которого соединен с коммутатором, а вторьй выход — с первым входом запоми-. нающего элемента, выходы котооого соединены с коммутатором, второй вход за-поминающего элемента через сумматор и блок сравнения соединен со своим гретьимвходом, отличающийся тем, что, с целью увеличения полосы схватывания при использовании его в системах автоподстройки частоты, в него введены дополнительные блок дифференцирования, коммутатор и фазовый детектор, вход которого соединен со входом основного фазового детектора, а выход через дополнительный блок дифференцирования соединен со входом логического элемента с инвертором, выход которого соединен с одним входом. дополнительного коммутатора, другие входы которого.соединены с выходами фазовых детекторов, а выход соединен со вторым входом запоминающего элемента.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 391495, кл. Cj 01 R 25/04, 27.09.7 1.

2. Авторское свидетельство СССР

% 531096, кл. 6 01 R 25/00, 18.02.75 (прототип) .

5 798620 6

При Ч = 5Й третий отрицательный импульс с блока 3 с помощью логического элемента 7 подключает через коммутатор

9 к первому входу. сумматора 6 выход . джазового детектора 1, а от второго вхо-. > Ф о р м у л а и з о б р е r е н и я за сумматора 6 отключает запоминающий элемент 5.

Когда выходное напряжение сумматора

6 будет равно заданному значению вблизи нуля (фиг. 2в),блок 10 сравнения разряжает запоминающий элемент 5.

Если же при включении фазового раз- личителя разность фаз положительна, но лежит в пределах Ж (f(2Æ и увеличивается, то первый отрицательный импульс появится на вькоде блока 4. Но логический элемент 7 выполнен таким образом, что никаких переключений в схеме не произойдет, а весь цикл начнется только при разности фаз на входе фазового детектора 1, когда напряжение на его выходе скачком изменит положительное напряжение на отрицательное.

Если при включении устройства разность фаз отрицательна и возрастает по абсолютному значению, то на выходах блоков .дифференцирования будут импульсы положительной полярности, и все процессы будут следовать в обратном порядке. ЗО

Использование второго фазового дегектора, второго блока дифференцирования и второго коммутатора позволяет сформировать положительную полуволну сигнала фазового различителя в пределах разности

35 фаз .ЗЖ только из положительных,полуволн напряжения фазовых детекторов, а отрицательную полуволну — из отрицательных полуволн напряжения фазовых детекторов.

Предлагаемый фазовый различитель позволяет значительно увеличить полосу схва798МО Ц О

g) О

Мфр

Составитель Н Медведева

Редактор В. Данко Техред Т.Mamma Корректор С. Шекмар

Заказ 10018/55 Тираж 7 43 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент», г. Ужгород, ул. Проектная. 4