Частотно-импульсная следящаясистема

Иллюстрации

Показать всеРеферат

Сеюз Советских Социалистических

Ресвублнк

О П - ° Н.И (111798696

ИЗОБРЕТЕНИЯ

К АВТОИ:КОМУ. СВИ ВТЕЛЬСТВУ (63) Дополнительное к авт. сеид-ву (22)Заявлено 28.08.78 (21) 2666436/18-24 (51)M. КЛ.

G 05 В 11/26 с присоединением эаявки No

Государственный комитет

СССР ио делам изобретений н откры1нй (23) ПриоритетОпубликовано 230181. Бюллетень N9 3

Дата опубликования описания 25,0181 (53) УДК 62-50 (088 ..8) (72) Автор изобретения

Г О Паламарюк (7! ) Заявитель рязанский радиотехнический институт (54) ЧАСТОТНО-ИМПУЛЬСНАЯ СЛЕДЯЩАЯ СИСТЕМА

Изобретение относится к вычислительной .технике и может быть использовано в вычислительных и управЛяющих комплексах в качестве устройства, совершающего операции над сигналами представленными в частотно-импульсной форме.

Известна частотно-импульсная следящая система, содержащая реверсивный счетчик и двоичный умножитель Щ

Недостатками ее являются низкие динамические характеристики.

Наиболее близкой к предлагаемой является частотно-импульсная следящая система, состоящая из преобразователя частота-код, реверсивного счетчика и двоичного умножителя (21 .

Недостатком данной системы является невозможность регулирований коэффициента передачи.

Цель изобретения - расширение. функциональных возможностей системы.

Поставленная цель достигается тем, что в устройство введены блок регулирования коэффициента передачи, датчики опорных частот, последовательно соединенные первый триггер, первый элемент совпадения и делитель частоты, а также второй двоичный умножитель, второй триггер и последовательно соединенные второй элемент совпадения, первый счетчик импульсов и первый блок элементов совпадения, выход которого подключен к входу второго двоичного умножителя, первый выход второго триггера соединен с потенциальным входом второго элемента

О совпадения, входом второго блока элементов совпадения и входом обнуления второго счетчика импульсов, а второй выход второго триггера подключен к потенциальному входу первого элемента совпадения и к входу первого блока

1Э элементов совпадения, и к входу обнуления первого счетчика импульсОв, причем выход первого датчика опорной частоты соединен с импульсным входом первого и второго элемента совпаде2О ния, выход второго датчика опорной частоты соединен с входом второго двоичного умножителя,выход. третьего датчика опорной частоты соединен с входом первого двоичного.умиожителя, выход четвертого датчика опорной частоты соединен с импульсным входом первого элемента совпадения, выход блока регулирования коэффициента пе-. редачи соединен .с входами первого

30 и второго триггеров.

798696

N< — код, записанный н реверсивном счетчике.

Приравнивая соотношение для Fz и разрешая относительно Np,ïoëó÷àþò

М F1 2m 2л

$ «р " О

Код преобразователя 1 частота-код согласно принципа его работы равен

N F 1 1 1 аь-

О где F0>1- опорная частота преобразователя.

В установившемся режиме Np = Й8.

Разрешая относительно «ар,,получают

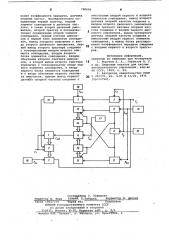

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит преобразователь 1 частота-код, реверсивный счетчик 2, первый 3 и второй 4 двоичные умножители, первый 5 и второй 6 триггеры, первый 7, второй 8 и третий 9 лементы совпадения, .делитель 10 частоты, первый 11 и второй 12 счет:чики импульсов, первый 13 и второй 14 блоки элементов совпадения, блок 15 регулирования коэффициента передачи, датчики 16-19 опорных частот.

Устройство работает следующим образом.

На входные шины первого и второго триггера поступают последовательности управляющих импульсов F с блока 15 на входы элементов совпадения и двоичных умножителей поступают последовательности импульсов Га.„ «02, ГО и

«04,эадaющиeся датчиками 16-19 опорных 20 частот.При этом на шину вычитания реверсивного счетчика 2.поступает с выхода делителя частоты импульсная последовательность с частотой

2 1

Ра F01

О&1 Ю 2 ОЬ О" 1 аь 1п1 F2

FOB F01

FO1 Fp2 ОЬ О4.

t ъ

S0 ОЪ

СОЬ и $$

Вид для.выражения ГО „получается из следующих соображений. Выразим последовательн. сть «2, формируемую двоичным умножителем 3, через параметры реверсивного счетчика 2 и двоичного

О2

«Ир

Ф где и "- емкость реверсивного счетчика, 6$ х О .с

0C F гд в — коэффициент деления делителя частоты, который равен

Fo

2маХ

Принимая во внимание, что система охвачена отрицательной обратной связью, для установившегося режима справедливо равенство

F F01

1 ОС F1 m откуда

F F = — т, «2

« <и

Для реализации этой зависимости необходимо, чтобы опорная частота «081 преобразователя 1, использующего принцип поразрядного взвешивания, подчинялась следующему соотношению

F01 FpZ

ОЬ1 F ! которое моделируется блоком, состоящим из триггера 6, элементов совпадения 8 и 9, счетчиков 11 и 12 импульсов, блоков 13 и 14 .элементов совпадений двоичного умножителя 4. Данный

l блок воспроизводит зависимость

Для получения выражения для F npo08 водим следующие преобразования. На выходе логических блоков совпадения имеем "пачечные" последовательности импульсов

n = N ;

Fa+ .

1 где и — число импульсов.

Частоты импульсных последовательностей выбираются равными и сдвинутыми относительно друг друга на 180 для исключения коЛебаний значения уп равляющего кода при переключении уп- . равления двоичного умножителя 4 с одного. счетчика импульсов на другой. .На выходе двоичного умножителя 4 имеем

FOa.

Од РОЬ аХ

2 2- емкость счетчиков 11 и 12. п2

2 1ъфх,F =Р— >

03 О2 F

2 оп

-Р

01 1wcl@

Р

2, сФ

О3 1Мс 2

В предлагаемой следящей системе коэффициент передачи является автоматически регулируемым, что позволяет применять ее в роли согласующего или множительно-делительного устройства в частотно импульсных вычислительных системах.

Формула изобретения

Частотно-импульсная следящая система, содержащая последовательно соединенные преобразователь частотакод, реверсивный счетчик и первый двоичный умножитель, о т л и ч а ю щ а я с я тем, что,- с целью расширения функциональных воэможностей системы в нее введены блок регулиро798696

Составитель Г. Нефедова

Редактор JI. Кеви Техред Н.Бабурка, Корректор М. Демчик

Заказ 10027/59 Тираж 951 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб. д. 4 5

Филиал.ППП "Патент", r. Ужгород, ул, Проектная, 4 вания коэффициента передачи, датчики опорных частот, последовательно соединенные первый триггер, первый элемент совпадения и делитель частоты, а также второй двоичный умножитель, второй триггер и последовательно соединенные второй элемент совпадения, первый счетчик импульсов и первый блок элементов совпадения, выход которого подключен к входу второго двоичного умножителя,.первый выход второго триггера соединен с потенциальным входом второго элемента совпадения, входом второго блока элементов совпадения, входом обнуления второго счетчика импульсов, а второй выход второго триггера подключен к потенциальному входу первого элемента совпадения, к входу первого блока элементов совпадения и к входу обнуления первого счетчика импульсов, причем выход первого датчика опорной частоты соединен с импульсным входом первого и второго элементов совпадения, выход второго датчика опорной частоты соединен с входом второго двоичного умножителя выход третьего датчика опорной частоты соединен с входом первого двоичного умножителя, выход четвертого датчика опорной. частоты соединен с импульсным входом первого элемента совпадения, а выход блока регулирования коэффициента передачи соединен с входами первого и второго триггеров.

Источники информации, принятые во внимание при экспертизе

1$ 1. Воронов A. A., Гарбузов А. Г. .и др. Цифровые аналоги ..для систем автоматического управления,.изд-во

AH СССР 1960, c. .62.

2. Авторское свидетельство СССР що Р 28277 О, кл. G 05 В 11/26, 1971 (прототип) .