Пропорционально-интегральный регулятор

Иллюстрации

Показать всеРеферат

с"т, ч и автеь «ц ъ» б,.б

ОП И 6Х

ИЗОБРЕТЕНИЯ

Сеюз Советскик

Социалистических

Распублик

<щ798707

К А1ТОРСИОМУ Св ЕТЕЛЬСМУ (61) Дополнительное к авт. свид-ву (22) Заявлено 010379 (21) 2730926/18-24 с присоединением заявки Йо— (23) Приоритет

Опубликовано 230181.6нзллетень М 3

Дата опубликования описания 2 30 181 (Я)м. кл.з

G 05 В 13/02

Государственный комитет

СССР по делан изобретений и открытий (53) УДК бг-SO (088.8) (72) Автор изобретения

A.È.Öûêóíîâ

Фрунзенский политехнический институт (71) Заявитель (54) ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР

Изобретение относится к самонастраивающимся регуляторам с непрерывным изменением параметров и может быть ис. использовано в металлургической, химической, нефтехимической и других отраслях промыаленности, где имеются нестационарные объекты с запаздыванием или с большой инерционностью.

Иэвестры регуляторы, содержащие настраиваемую часть, состоящую из параллельно соединенных пропорциональ ного блока и интегратора, и контур самонастройки, состоящий из второго н третьего интеграторов, блоков умножения, блоков сравнения, делителя и . 15 первого блока изменения масштаба, выход которого соединен с первым входом первого блока умножения, входы блока сравнения соединены соответственно через второй блок умножения с 20 выходами первого и второго интеграторов и через третий блок умножения с выходами сумматрра и третьего интегратора, а выход с первыми входами, четвертого и пятого блоков умноже - 25 ния, второй вход четвертого блока умножения соединен с выходом первого интегратора, а выход — co входом первого блока изменения масштаба и со вторым входом первого блока умно- 30! жения, выход которого через последовательно соединенные второй интегратор и шестой блок умножения соединен с управляющим входом второго усили- " теля, второй вход пятого блока умножения соединен с выходом сумматора, а его выход непосредственно и через второй блок изменения масштаба соединен соответствующими входами седьмо

ro блока умножения, выход которого через последовательно соединенные третий интегратор и делитель соединен со вторым входом шестого блока умножения и управляющим входом первого усилителя (11 и j 2).

Однако известные устройства позволяют управлять только инерционными объектами беэ запаздывания, но они неприменимы практически для инерционных объектов с запаздыванием, так как при этом резко ухудшается качество регулирования, а при некотором сочетании параметров устойчивого объекта вся замкнутая система автоматического регулирования оказывается неустойчивой.

Известны устройства с применением регуляторов, содержащие последовательно соединенные вычислительное устройство (например, блок умноме798707 ния), и исполнительный механизм (например, пропорциональный блок), и соединение входов вычислительного устройства со входом и выходом настраиваемой части регулятора, а выхода исполнительного механизма— 5 с управляющим входом настраиваемой части регулятора позволяет значительно повысить быстродействие и уменьшить перерегулирование укаэанных регуляторов, и применить их для управления инерционными объектами с запаз дыванием t3 g и (4).

Наиболее близким по технической сущности к предлагаемому является пропорционально-интегральный регулятор, содержащий измеритель рассогла-15 сования, выход которого соединен с первым входом первого вычислительного устройства, через первый усилитель с первым входом сумматора, а через интегратор — с первым входом второго Щ вычислительного устройства и входом второго усилителя, выход которого соединен со выходами первого и второго вычислительных устройств, выходы которых соединены с первыми входами,соот- р ветственно первого и второго исполнительных механизмов,выходы которых соединены с управляющими входами,соот ветственно,первого и второго усилителей 751.

Цель изобретения — повышение быстродействия и уменьшение перерегули.рования регулятора.

Поставленная цель достигается тем, что в регуляторе выход первого вычис- З лительного устройства соединен со вторым входом второго исполнительного механизма, а выход второго вычислительного устройства соединен со вторым входом первого исполнительного 4Q механизма.

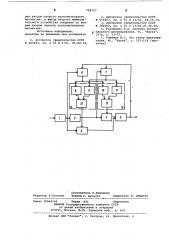

На чертеже изображена функциональная схема пропорционально-интегрального (ПИ) регулятора.

Схема содержит измеритель 1 ðàñсогласования, интегратор 2, первый и второй усилители .3 и 4, сумматор

5, первые и вторые вычислительные устройства 6 и 7, элементы 8-11 изменения масштабасуммирующие элементы

12 и 13, первый и второй исполнитель- о ные механизмы "4 и 15.

Регулятор работает следующим образом.

Измеритель 1 рассогласования имеряет отклонение регулируемого параметра от требуемого значения. Сигнал отклонения интегрируется интегратором 2 и одновременно усиливается первым усилителем 3. Проинтегрированный сигнал рассогласования усиливается 40 вторым усилителем и суммируется в сум-. маторе 5 с выходным сигналом первого усилителя 3.

На выходе сумматора 5 формируется сигнал управления, поступающий на вто. Я рые входы вычислительных устройств б и 7, в данном случае блоков умножения, где он перемножается с сигналом рассогласования в первом вычислительном устройстве б и с лооинтегрирован ным сигналом рассогласования во втором вычислительном устройстве 7

Сигнал с первого вычислительного устройства б поступает на первый вход первого исполнительного меха низма 14 и на второй вход второго исполнительного механизма 15.

Сигнал со второго вычислительного устройства 7 поступает на второй вход первого исполнительного механизма 14 и на первый вход второго исполнительного механизма 15.

В качестве исполнительных механизмов 14 и 15 с пропорциональными характеристиками применяют обычные операционные усилители.

B исполнительных механизмах 14 и 15 сигналы масштабируются с помощью масштабирующих элементов 8 — 11 и сумчируются с помощью суммирующих элементов 12 и 13. Исполнительные механизмы 14 и 15 формируют сигналы управления, под действием которых происходит изменение коэффи циентов усиления усилителей 3 и 4 в пропорциональной и интегральной частях регулятора. Коэффициенты передачи масштабирующих элементов 8-11 выбираются из условия минимума интегрального показателя качества переходного процесса.

Предлагаемые отличительные особенности регулятора позволяют повысить быстродействие приблизительно на 25% и уменьшить перерегулирование приблизительно на 15% по сравнению с известными регуляторами.

Формула изобретения

Пропорционально-интегральный регулятор, содержащий измеритель рассогласования, выход которого соединен с первым входом первого вычислительного устройства, через первый усилитель с первым входом сумматора, а через интегратор — с первым входом второго вычислительного устройства и входом второго усилителя, выход которого соединен со вторым входом сумматора, выход которого соединен со вторыми входами первого и второго вычислительных .устройств, выходы которых соединены с первыми входами, соответственно, первого и второго исполнительных механизмов, выходы которых соедйнены с управляющими входами, соответственно, первого и второго усилителей, отличающийся тем, что, с целью повышения быстродействия и уменьшения перерегулирования регулятора, в нем выход первого вычислительного устройства соединен со вто-.

798707

Составитель Н.Нефедова

Техред Г. Маточка Корректор Н. Швыдкая

Лъ

Редактор Н.Рогулич

Заказ 10044/60 Тираж 951 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 рым входом второго исполнительного механизма, а выход второго вычислительного устройства соединен со вторым входом первого исполнительного механизма.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 495641, кл. G 05 В 5/01. 05.02.74.

2. Авторское свидетельство СССР

9 551607, кл. G 05 В 13/02, 04.10.74.

3.. Авторское свидетельство СССР

9 381062, кл. G 05 С 13/00,21.10.69.

4. Растрыгин Л.A. Система экстремального регулирования. M "Наука", 1974, с. 73-77.

5. Раибман Н.С. Что такое идентификация, М., "Наука", с. 101-114 (прототип).