Устройство для синхронизацииввода информации из канала связи

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических т>еспубник

<н>798774.Ж.

/ (б3) Дополнительное к авт, саид-ву (22) Заявлено 1501,79 (21) 2750253/18-24

С ПРИСОЕДИНЕНИЕМ Заланн Йо (23) Приоритет

Опубликовано 23.01.81. Бюллетень ИЗ 3

Дата опубликования описания 30. 01. 81.р („З

G 06 F 1/04

G F 3/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. .325(088.8) (72) Авторы изобретения

С.Г.Андросенко, M.B.Äèíoâè÷, А.A.Ìoðîçîâ и А.Б.Тимофеев (71) Заявитель

Ордена Ленина институт кибернетики AEI Украинской CCP (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВВОДА

ИН4>ОРМАЦИИ ИЗ КАНАЛА СВЯЗИ Ю

Изобретение относится к вычислительнои технике и может быть использовано в устройствах сопряжения каналов передачи данных с ЭВМ.

Известны устройства сопряжения каналов передачи дискретной информации с ЭВМ, содержащие регистры, счетчики стробирования, тактовый генератор, логические элементы И и ИЛИ (11.

Однако в этих устройствах при передаче информации в канал связи аппаратурой передачи данных абонентского пульта или коммуникационного процессора информационный байт (блок) 15 ограничивается стартовой и стоповой посылкой. Каждому каналу по приему информации соответствует .регистр, в который в начале приема записывается значение кода старто- 20 вой посылки, кроме этого, каждому каналу соответствует счетчик стробирования, на который поступают синхронизирующие импульсы тактового генератора устройства. При сравнении значений регистра и счетчика стробирования (в этот момент определяется стартовая посылка) в регистр заносится новая константа, соответствующая частоте стробирова- 30 ния последующих информационных битов байта. Знак бита определяется по середине бита, так как в этот момент он наименее подвержен помехам. Таким образом, все характеристические моменты восстановления (или середины информационных битов) отсчитываются от заднего фронта стартовой посылки.

При расхождении частот передающего и приемного генераторов характеристические моменты восстановления (или середины информационных битов) сдвигаются в приемнике информации по отношению к информации, передаваемой передатчиком. Такой сдвиг накапливается, что ограничивает длину передаваемых блоков информации и снижает эффективную скорость передачи данных по каналу связи.

Наиболее близким по технической сущности к предлагаемому является устройство преобразования Временных интервалов в двоичном коде, содержащее регистр адреса массива двоичных кодов, регистр адреса обработки, регистр конечного адреса обработки, схему сравнения, буферный регистр, счетчик и дешифратор, при798774 чем входы регистра адреса обработки, регистра адреса массива двоичных кодов и регистра конечного адреса обработки соединены с шиной чтения и шиной импульсов записи процессора, а выход регистра ардеса обработки соединен с первым входом схемы сравнения и входом процессора, выход регистра адреса массива двоичных кодов подключен к процессору, выход регистра конечного адреса обработки соединен со вторым входом схемы сравнения, выход которой соединен со входом процессора, первый вход буферного регистра подключен к шине импульсов записи, а его выход соединен со входом процессора, шина импульсов записи через счетчик и. дешифратор соединена со входом процессора, а также регистр скорости канала, регистр дополнения до бита, регистр остатка преобразования и регистр временного интервала, первые входы которых соединены с шиной чтения, а вторые — с широй импульсов процессора, выход регистра. скорости соединен с третьим входом регистра дополнения до бита, выход которого подключен ко входу процессора и третьему входу регистра временного интервала, выход Которого соединен со вторым входом буферного регистра и входом процессора, выход регистра остатка соединен со входом процессора (2j .

Недостатком этого устройства является низкая эффективная скорость передачи данных в канале связи.

Цель изобретения — повышение эффективной скорости передачи данных в канале связи.

Поставленная цель достигается тем, что в устройство, содержащее два регистра времени, регистр константы скорости и регистр признаков,. первые входы которых соединены с выходом узла управления, а вторые входы — со входом устройства и первым входом узла управления, выход которого является первым выходом устройства, схему сравнения рассогласования, сумматор, первый вход которого подключен к выходу первого регистра времени и третьему входу второго регистра времени, выходом соединенного со вторым входом сумматора и вторым выходом устройства, а четвертым входом — с третьим входом первого регистра времени и выходом дешифратора времени, вход которого подключен к выходу регистра константы скорости, третьему входу сумматора и третьему выходу устройства, введены-регистр рассогласогания частот и регистр константы рассогласования, причем первые входы регистра рассогласования константы соединены с.выходом узла управления, четветрым входом сумматора и первым входом схемы сравнения рассогласования, а вторые входы — со входом устройства, выход схемы сравнения рассогласования подключен к пятому входу сумматора и второму входу узла управления, второй вход — к выходу регистра признака и четвертому выходу устройства; третий вход — к выходу регистра константы рассогласования и пятому выходу устройства, а четвертый вход — к шестому входу сумматора, пятому входу второго регистра времени и выходу регистра рассогласования частот, третьим входом соединенного с выходом сумматора. Кроме того, узел управления содержит распределитель и счетчик состояний, причем вход распределителя соединен с первым входом счетчика состояний и первым входом узла, а вы2О ход — с выходом узла и вторым входом счетчика состояний, третий вход которого является вторым входом узла.

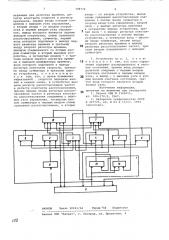

На чертеже представлена блок-схема устройства.

Устройство содержит узел 1 управления, осуществляющий тактировку всех узлов устройства, первый регистр 2 времени, в котором хранится очередное время рассогласования в канале, второй регистр 3 времени, в

Зо котором хранится предшествующее время рассогласования в канале, регистр

4 рассогласования частот, осуществляющий запоминание остатка рассогласования, регистр 5 признаков, в ко-. тором хранятся коды знаков остатка, регистр 6 константы рассогласования, в котором записывается код допустимого предела рассогласования, схему 7 сравнения рассогласования, осу4Q ществляющую сравнение величин остатка рассогласования и допустимого предела рассогласования, регистр 8 константы скорости, в который записывается код скорости передачи по данному каналу, дешифрато 9 времени, осуществляющий в зависимости от скорости передачи запись определенных разрядов кода времени в регистры 2 и 3, сумматор 10, осуществляющий сложение и вычитание кодов моментов рас о согласования в канале, коммуникаци" онный процессор 11. Узел управления состоит из счетчика 12 состояний и распределителя 13.

Устройство работает следующим образом.

Информация из канала связи преобразуется аппаратурой передачи данных в уровни напряжения. Кажцое изменение напряжения в канале (характеЬО ристический момент восстановления) записывается в оперативную память процессора 11 с отметкой реального времени для изменения состояния в канале. Каждому каналу в определенном поле оперативной памяти со798774 ответствует макрокоманда (управляющее слово приема информации), в поле которой при первоначальной нагрузке устройства заносятся коды константы скорости обмена по каналу связи, допустимой для данной скорости и длины передаваемого блока константы рассогласования, отводится поле признаков рассогласования (знаки остатка преобразования), в которое помещаются преобразованные из временных меток двоичные биты полученного из канала сообщения.

По запросам узла 1 процессор 11 осуществляет посылку по своим выходным шинам из массива временных меток оперативной памяти в регистр 2 кода времени изменения очередного состояния в канале, а также осуществляет чтение из оперативной памяти управляющего слова приема информации.

Коды макрокоманды записываются в регистр 8 константы скорости, в регистр 5 признаков, регистр 4 рассогласования частот, регистр 6 константы рассогласования, в регистр 2 в соответствии с кодом дешифратора 9, g$ который декодирует содержимое регистра 8, записывая код со времени рассогласования в канале. После этого по сигналам узла 1 содержимое регистров ? 3 поступает на сумматор 10, ЗО которйй осуществляет вычисление количества битов и их полярность, содержащихся на заданном временном интервале. Значение остатка вычислений записывается в регистр 4 рассогласования частот, знак остатка (+ или †) . заносится в регистр 5 признаков. По сигналам узла 1 код времени конца интервала переписывается из регистра 2 в регистр 3. Схема

7 сравнения сравнивает величины ко- 40 дов в регистре 4 и регистре б константы рассогласования, в который при записи управляющего слова записывается код определенной величины.

Если содержимое регистра 4 меньше величины константы рассогласования, то по сигналам узла 1 в регистр 2 иэ поля массива временных меток оперативной памяти процессора 11 записывается очередное время pacco- . щ гласования по данному каналу. Аналогично описанному происходит вычисление остатков на очередных интервалах и их алгебраическое суммирование в сумматоре 10,.причем после. каждого суммирования результат из сумматора 10 пересылается в блок

4 рассогласования частот. Схема сравнения рассогласования сравнивает коды величин, записанных в регистрах

4 и б. Если содержимое регистра 4 ф больше содержимого регистра б, то по команде узла 1 содержимое регистра 3 и регистра 4 пересылается в сумМатор 10, где происходит сложение или вычитание этих величин в соответ- Я ствии со знаком остатка, находящегося в регистре признаков, знак "+" рассогласования в регистре признаков означает, что частота генератора в приемнике аппаратуры передачи данных превышает частоту генератора в передатчике аппаратуры передачи данных удаленного терминала, знак величины рассогласования указывает на отставание частоты генератора в приемнике по отношению к генератору передатчика.

Полученный результат записывается из сумматора 10 в регистр 3 и в этом случае происходит временная синхронизация информации.

После получения всего передаваемого блока, содержимое, записанное в регистре константы скорости, втором регистре времени, регистре рассогласования частот, регистре признаков, регистре константы скорости по сигналам узла 1 записывается в поле управляющих слов оперативной памяти коммуникационного процессора 11.

Работа узла 1 управления состоит в следующем.

Пс тактирующим импульсам (частота тактирующих импульсов равна тактовой частоте коммуникационного процессора 21), поступающим от процессора в узел 1, в соответствии с кодами счетчика 12 состояний, распределитель 13 сигналов осуществляет выработку сигналов управления на своих выходных шинах.

Сигналы управления осуществляют запись кода в определенные узлы устройства, перепись кода в коммуникационный процессор. Каждый сигнал управления модифицирует код счетчика 12 состояний, кроме того, состояние счетчика 12 модифицирует сигналы с выхода процессора 11 и сигналы с выхода схемы 7 сравнения . рассогласования.

Таким образом, в отличие от известного устройства, данное устройство производит временную синхронизацию поступающей информации, что позволяет увеличивать длину передаваемых блоков, применять менее стабильные генераторы в приемной и передающей аппаратуре передачи данных абонентских пультов (удаленных терминалов), мультиплексорах передачи данных.

Увеличение длины передаваемого блока позволяет уменьшить избыточность передаваемой информации за счет снижения количества служебных ответов и обрамления (синхронизирующие коды передаваемых блоков), что увеличивает эффективную скорость передачи по каналу связи.

Формула изобретения

1. Устройство для синхронизации ввода информации из канала связи, со798774

ВНИИПИ Заказ 10031/64 Тираж 756 Подписное

Филиал ППП "Патент ", r. Ужгород, ул . Проектная, 4 держащее два регистра времени, регистр константы скорости и регистр признаков, первые входы которых соединены с выходом узла управления, а вторые входы — со входом устройства и первым входом узла управления, выход которого является первым выходом устройства, схему сравнения рассогласования, сумматор, первый вход. которого подключен к выходу первого регистра времени и третьему входу второго регистра времени, выходом соединенного со вторым входом сумматора и вторым выходом устройства, а четвертым входом — с третьим входом первого регистра времени и выходом дешифратора времени, вход которого подключен к выходу регистра константы скорости, третьему входу сумматора и третьему выходу устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения эффективной;, скорости передачи данных в канале связи, в устройство введены регистр рассогласования частот и регистр константы рассогласования, причем первые входы регистра рассогласования частот и регистра константы рассогласования соединены с выходом узла управления, четвертым входом сумматора и первым входом схемы сравнения рассогласования, а вторые входы — co входом устройства, выход схемы сравнения рассогласования подключен к пятому входу сумматора и второму входу узла управления, второй вход — к выходу регистра признака и четвертому выходу устройства, третий вход — к выходу регистра константы рассогласования и пятому выходу устройства, а четвертый вход — шестому входу сумматора, пятому входу второго регистра времени и выходу регистра рассогласования частот, третьим входом соединенного с выходом сумматора.

2. Устройство по и. 2, о т л и35 ч а ю щ е е с я тем, что узел управления содержит распределитель и счетчик состояний, причем вход распределителя соединен с первым входом счетчика состояний и первым входом узла, а выход — с выходом узла и вторым входом счетчика состояний, третий вход которого является вторым входом узла.

Источники информации, принятые во внимание при экспертизе

1. Патент СИА 9 3362015, кл. 340-172.5, 1967.

2. Авторское свидетельство СССР

Р 497725, кл. Н 03 К 13/17, 1972 (прототип).