Преобразователь дробных двоичныхчисел b десятичные

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублнн

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

< >798798

g Дфоп©9@+©ko св змльс вУ (е!) Дополнительное к вет. сеид-ау (22) Заявлено 18. 01; 79 (Щ 2714762/18-24

М (лЗ

G 06 F 5/02 с присоединением зевки 89,—

Госуяаретвеииый комитет

СССР по делам изобретеиий и открытий

{23} ПриоритетОпубликовано 23,0181 Ьюллетень Йэ 3

Двтв опубликования описания 2 3. 01. 81 (53) УДК 681.325 (088.8) (72) Авторы изобретения

В. В. Мымриков и Н. М. Грибков (7 3 ) За яв ит ел ь (54) ПРЕОБРАЗОВАТЕЛЬ ДРОБНЫХ ДВОИЧНЫХ ЧИСЕЛ

В ДЕСЯТИЧНЫЕ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в арифметических устройствах для преобразования параллельных двоичных кодов дробных чисел в десятичные. Известен преобразователь дробных двоичных чисел в десятичные, содержащий каскад сумматоров, выходной регистр, выходную тетраду и коммутатор (1).

Недостаток этого преобразователя состоит в его большой сложности.

Наиболее близким к предлагаемому по технической сущности и схемному -. "5 решению является преобразователь дробных двоичных чисел в десятичные, содержащий сумматор, первый регистр, разрядные входы которого соединены с первой группой выходов сумматора, тетради выходного регистра $2) .

Недостаток этого преобразователя состоит в относительно большом объеме аппаратуры, свяэанньм с дублированием тетради в регистре и в выхОдном регистре, также в невозможности преобразования с помощью одного преобразователя нескольких чисел.

Цель изобретения - упрощение пре-. образователя. 30

2 (ЩД ЩфЩ, Поставленная цел тем, что преобразователь дробных двоичных чисел в десятичные,содержащий сумматор, первый регистр, разрядные входы которого соединены с первой группой выходов сумматора, тетради выходного регистра, дополнительно содержит группы элементов И, группу элементов ИЛИ, регистр сдвига, второй регистр, информационные входы которого соединены с выходами первого регистра,. а разрядные выходы второго регистра соединены с первыми входамн элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И первой группы, вторая группа выходов сумматора соединена с информационными входами тетрад выходного регистра, управляющие входы тетрад которого соединены с соответствующими выходами элементов И второй группы, первые входы которых соединены с разрядными выходами регистра сдвига, вторые входы элементов И второй группы соединены с первым входом синхронизации преобразователя и с управляющим входом первого регистра, первые входы элементов И первой группы соединены с информационным входом преобра798798

110011

Первый разряд,2-ой цикл +

l 11111

11111 е0

3- и цикл +

1011

1011

0110,111 — третья б частная сумма

Третий разряд зователя, второй вход синхронизации преобразователя соединен с входом регистра сдвига и с управляющим входом второго оегистра, выход младшего разряда регистра сдвига соединен со вторыми входами элементов И первой группы, выход и-ого элемента И первой группы (где п -число разрядов преобразуемого кода соединен со вхо. дом .(n-1)-ого разряда первого регистра и с первым входом младшего разряда сумматора, выход (n-1)-ого элемента ИЛИ группы соединен со входом (n-2)-ого разряда первого регистра.и с первым входом (и-1)-ого разряда сумматора, выход i-ого (i=1+

p(n-2) элемента ИЛИ группы соединен с первым входом i-ого разряда сум,матора и вторым входом (i+2) ого разряда сумматора.

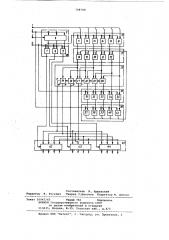

На чертеже приведена блок-схема предлагаемого преобразователя для случая, преобразования шестиразрядных дробных двоичных чисел в трехразрядные.десятичные.

Преобразователь содержит информационный вход 1 для подачи параллельного двоичного кода дробного числа, вход 2 для подачи импульса признака кода, входы 3 и .4 синхронизации преобразователя путем подачи сдвинутых друг относительно друга синхроимпульсов, блок 5 управления, состоящий из регистра б сдвига и элементов И 7,8 и 9, первую группу 10 элементов И 11-16, группу 17 элементов

ИЛИ 18-22, сумматор 23, состоящий из полусумматоров 24-26 и сумматоров

27-29, первый регистр 30, триггеров

31-35, второй регистр 36, триггеров

37-41 и тетрады 42-44 выходного регистра 45 ° Элементы И 7-9 образуют вторую группу 46 элементов И.

Преобразователь работает следующим образом.

Двоичный код преобразуемого дробного числа поступает с информационного входа 1 на входы группы элементов И 10, причем первый после запятой двоичный разряд поступает на вход элемента И 11. О поступлении на преобразование очередного кода свидетельствует импульсный признак кода, поступающий с входа 2 на вход первого разряда регистра сдвига б.

Продвижение информации по регистру б осуществляется синхросигналами, поступающими с входа З.При поступлении очередного сийхроимпульса признак кода записывается в регистр и появляется на выходе первого разряда регистра, с выхода которого он поступает на вход элемента И 7 и управляющие входы элементов И группы

10, разрешая прохождение двоичного кода через группу элементов И 10 и ИЛИ 17 на вход сумматора 23, обеспечивающего сложение этого кода с о

5 (О

20 тем же кодом, сдвинутым на два разРяда в сторону старших разрядов..

Таким образом, осуществляется умножение входного кода на число 10 (1010). По окончании процесса распространения переносов в сумматоре, на ьго выходах появляется код первой частной суммы, четыре старших разряда которой с выходов полусумматоров и сумматора 24, 25 и 27 определяют код старшей тетрады десятичного числа. Этот код поступает одновременно на входы всех тетрад 42-44, но записывается только в тетраду 42, науправляющий вход которой поступает при появлении на входе 4 — синхронизирующего сигнала сигнал приема первой тетрады числа. Одновременно с этим дробная часть кода суммы с выходов полусумматора и сумматоров

26, 28 и 29 ИЛИ 22 и И 16 записывается в первый регистр 30.

При поступлении очередного синхроимпульса на вход 3 код дробной части суммы из первого регистра

30 переписывается во второй регистр

36, с выходов которого через группу элементов ИЛИ 17 поступает на входы двоичного сумматора 23 и умножается на число 10 (1010). Этим же синхросигналом в регистре сдвига б единица сдвигается в следующий разряд, отчего группа элементов И 10 и элемент И 7 запираются, а при поступлении очередного синхросигнала на вход 4 на выходе элемента И 8 появился сигнал приема второго числа, которое записывается в тетраду 43 выходного регистра 45.

Этот процесс поочередного выделения разрядов десятичного числа продолжается до окончания преобразования. После и циклов преобразования преобразователь самоочищается. Числовой.пример преобразования шестиразрядного двоичного кода, 310011:

1-й цикл +,110011

011111111 — первая частная сумма 7 дробная часть первой частной суммы

ВтоРой РазРЯд 100Д,1011 — вторая

9 частная сумма

798798

4-й цикл +, 111

111 — четвертая час1000,11 тная мма

Четвертый разряд 8

5-й цикл

+,11 11

,0111 1 ная сумма Я

Пятый разряд 7

6-й цикл + 00,1

Шестой разряд

†01 — шестая част н ая сумма дробная часть отсутствует, т.е. преобразователь самоочистился.

Формула изобретения

Преобразователь дробных двоичных чисел в десятичные, содержащий сумматор, первый регистр, разрядные входы которого соединены с первой группой выходов сумматора, тетрады . выходного регистра, о т л и ч а юц и и с я тем, что, с целью упрощены

Использование предлагаемого преобразователя позволяет упростить известный преобразователь эа счет сокра щения разрядности регистра на четыре разряда, исключить цепи передачи кода при сдвиге на четыре разряда и упростить расширение разрядности преобразователя (не требуется увеличивать число цепей сдвига) . Кроме того, предлагаемый преобразователь, вотличие от известного, имеет возможность преобразования нескольких входных чисел,, для чего следует увеличить число выходных регистров и с соответствующими цепями коммутации. Остальная же часть преобра.зователя остается общей. преобразователя, он содержит „группы элементов И, группу элементов ИЛИ регистр сдвига, второй регистр, информационные входы которого соединены с выходами первого регистра, а разрядные выходы второго регистра соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И первой группы. вторая группа выходов сумматора соединена с информационными входами тетрад выходного регистра, управлякицие входы тетрад которого со« единены с соответствующими выходами элементов И второй группы, первые входы которых соединены с разрядными выходами регистра сдвига, вторые входы элементов И второй группы соединены с первым входом синхронизации преобразователя и с управляющим входом первого регистра, первые входы элементов И первой группы соединены с информационным входом преобразователя, второй вход синхронизации преобразователя соединен с входом регистра сдвига и с управляющим входом второго регистра, выход младшего разряда регистра сдвига соединен со вТорыми входами элементов И!первой группы, выход п-ого элемента И первой группы (где и -чис. ло разрядов преобразуемого кода) соединен со входом (n-1) -ого разряда первого регистра и с первым входом младшего разряда сумматора, выход (.n-1)-ого элемента ИЛИ группы соединен со входом (и-2) -ого разряда первого регистра и с первым входом (n-1)-ого разряда сумматора, выход

i -ого (i =1 + (n-2) ) элемента ИЛИ группы соединен с первым входом 1-oro разряда сумматора и вторым входом (i + 2) -ого разряда сумматора.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ 9 1963030, кл. 42 m3 5/02, 1973. .2. Авторское свидетельство СССР

Ф 308426, кл. G 06 F 5/02, 1969 (прототип).

198798

Составитель М. Лршавский

Редактор Н. Рогулич Техред T.Nàòî÷êà Корректор М. Демчик

Заказ 10047/65 Тираж 756 Подписное

ВНИИПИ Государствеккого комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4