Логический модуль

Иллюстрации

Показать всеРеферат

Союз Севетавюх

СециаюктмМесюе

° мвублнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<« 798806

К АВТОУСК©МУ Св ЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22} Заявлено 03.10. 78 (21) 2687227/18-24

Р > Ц К З

G 06 Р 7/00 с присоединением заявки HP—

Гвсударетвеякия квивтет

СССР вв яелаи язебретевяй н открытка (23) Приоритет —

Опубликовано 230131, Бюллетень Н9 3 (53) УДК 681. 327 (088.8) Дата опубликования описания 23 .01 . 81 (72) Авторы изобретения

В. Л. Артюхов, А. А. Шалыто и В. Е. Вольский (71) Заявитель

-(54) ЛОГИЧЕСКИЙ МОДУЛЬ

Изобретение относится к автоматй-ке и вычислительной технике и предназначено для реализации путем настройки всех логических формул в бевисе Ч, ив грех и менее букв лри ревной доступности прямых и инверсных выходов источников информации .

Известен логический модуль, содержащий элементы И, ИЛИ (1). 1©

Недостатком его является большая сложность.

Наиболее близким к предлагаемому является логический модуль, содержащий два элемента И, два элемента ИЛИ,1 причем первый вход модуля соединен с первым входом первого элемента ИЛИ, второй вход модуля соединен с первым входом первого элемента И, выход первого элемента HJIH и третий вход моду- 20 ля соединены с входами второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, .выход которого является выходом модуля . Кроме того, второй вход второго элемента ИЛИ является входом модуля 32 l°.

Недостатком его является невозможность реализации всех формул из трех букв . 30

Цель изобретения . — расширение функциональных возможностей за счет реализации всех формул из трех букв .

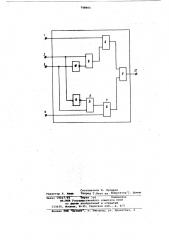

Цель достигается тем, что модуль содержит третий элемент И и два элемента НЕ, причем четвертый вход модуля соединен через первый элемент

НЕ с вторым входом первого элемента

ИЛИ и непосредственно соединен с первым входом третьего элемента И, второй вход которого через второй элемент НЕ соединен с первым входом модуля, а выход подключен к второму входу первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ.

На чертеже схематически представлен предлагаемый модуль.

Модуль содержит входы 1-4, элемент

И 5-7, элемент ИЛИ 8 и 9, элемент

НЕ 10 и 11, выход 12.

Структура устройства описывается формулой i яч хъ)ч xxxsx4Работа устройства при различных режимах настройки, позволяющих реализовать представителей всех типов формул в базисе у, j из трех букв, представлена в таблипе.

798806

Арифметический полином

Настройка

Реализуемая формула

ӄ— Х1 Х Х4 х =0

1+ 2

2= х1ч хЗх4

У2= хчх х >

1(1 + 1) "3 Х4 (Х1Ч 4) .1 х,(х ч-, 1+1+1 х(=1

Q = ХУх ч Х4 х =О, Х4=1 х(=0, х2-О у = х1х х4 х2=Х4 i Х4. 1

Х4=1,: х =1

У = Х1Ч X .Ц= харч <у хз=х4=1 9y= х 2 х =х =0 У

7 х1=0, х2=х, Из таблицы следует, что устройство путем настройки реализует любого представителя типов формул в базисе

,1/ из одной, двух и трех букв соответственно 1, 2, 1+1, 3, 1+2, 1 (1+1 ), 1+1+1 . Поэтому при равной доступности пряьых и инверсных выходов источников .информации устройство позволяет рЕализовать любую 30 формулу,в указанном базисе из трех и менене букв.

Таким образом, предлагаемое устройство обладает более широкими фуркциональными возможностями по срав 3$ нению с известным при незначительных его усложнениях (на два инвертора и один двухвходовой элемент И) и увеличении числа внешних выводов (на один вход). Число внешних выводов предла- gg гаемого устройства минимально и при указанных функциональных возможностях не может быть снижено.

Формула изобретения

Логический модуль, -содержащий два элемента И, два элемента ИЛИ, причем первый вход модуля соединен с первым входом первого элемента ИЛИ, второй 50 вход модуля оединен с первьа4 входом первого элемента И, выход первого элемента ИЛИ и третий вход модуля соединены с входами второго элемента

И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого является выходом модуля, отличающийся тем, что, с целью расширения функциональных воэможностей за счет реализации всех формул из трех букв, он содержит третий элемент И и два элемента НЕ, причем четвертый вход модуля соединен через первый элемент ИЕ с вторым Входом первого элемента ИЛИ и непосредственно соединен с первым входом третьего элемента И, второй вход которого через второй элемент НЕ соеди нен с первым входом модуля, а выход подключен к второму входу первого элемента И, выход которого соединен с вторЫм входом второго элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 275524, кл. 9 06 F 7/00, 20 .03.69.

2. Стопский С.Б. Логические схемы на полупроводниках и их применение.

Л., "Энергия", 1969, с. 21. табл. 12, рис. 4 (прототип).

798В06

Составитель Е. Пупырев

Мекред Т.усато ка .,Корректор С . Щомак

Редактор Л. NOeN т4иИ, r. Ужгород, ул. Проектная, 4

Филиал

Заказ раж 756 Подписное

ВИ. ИПИ Государственного комитета СССР по @армм изобретений и открытий

113035, Иооапва, Ж-35, Раушская наб., д. 4/5