Умножитель частоты

Иллюстрации

Показать всеРеферат

О П ИС А Н И Е

ИЗОБРЕТЕНИЯ

Союз Советских

Сециэлнстическмх

Республнк (1)798831

К АВТОУСМОМУ СВИ ВТИЛЬСТВУ (61) Дополнительное к авт. сеид-ву (5f)M. Клз (22) Заявлено 24. 10. 78 (21) 2677506/18-24 с присоединением заявки Но (23) Приоритет

G 06 F 7/60

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 23.01,81. бюллетень Н9 3

Дата опубликования описания 2601.81 (53) УДК 681.328 (088.8) (72) Авторы изобретения

Р.M.Ãàéäó÷îê,. Н.В.Кирианаки и С.С.Кочеркевич (71) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к измерительной технике и, в частности, может найти применение в информационноизмерительных и управляющих системах, где требуется синхронизация работы вторичных измерительных устройств, а также повышение быстродействия и точности измерения.

Известен умножитель частоты, содержащий счетчики, генератор тактовых импульсов, блок сравнения, два делителя частоты, регистр, триггер. управления и элементы И, ИЛИ (11 .

Недостатком его является малая точность измерения полученной частоты на выходе.

Наиболее близким к предлагаемому является .умножитель частоты, содержащий генератор опорной частоты, последовательно соединенные суммирую- 2 щий счетчик, схему записи, регистр, схему переноса и вычитающий счетчик, а также формирователь импульсов, схему дифференцирования и распределения, управляющий триггер, вспомогательный счетчик, схему фиксации нуля, два ключа и дополнительный опорный генератор (2 .

Недостатком его является также низкая точность. 30

Цель изобретения — повышение точности умножения. Поставленная цель достигается тем, что в умножитель частоты, содержащий генератор опор-" ной частоты, выходом подключенный к управляющему входу вычитающего счетчика, выходы которого соединены с входами блока фиксации нуля, выход которого подключен к первым входам соответствующих элементов И группы, выходы которых, кроме элемента И группы младшего разряда, соединены с -информационными входами вычитающего счетчика, а вторые входы элементов И группы - с выходами регистра, суммирующий счетчик, формирователь импульсов, вход которого является входом умножителя, в него введены делитель частоты и два триггера, причем счетный вход первого триггера подключен к выходу блока фиксации нуля, а выход подключен к выходу умножителя и к третьему входу элемента

И группы младшего разряда, выход которого подключен к раздельному вхо- ду второго триггера, выход которого подключен к входам младшего разряда вычитающего счетчика, а счетный вход — к выходу генератора опорной частоты к первому входу делителя

798831 частоты, второй вход которого подключен к выходу формиронателя импульсов, управляющему входу регистра и первому входу суммирующего счетчика, второй вход которого подключен к выходу делителя частоты, а выходы — к информационным входам регистра.

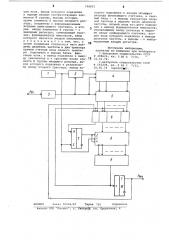

На чертеже представлена блок-схе" ма предлагаемого умножителя частоты, умножитель частоты содержит генератор 1 опорной частоты, делитель 2 частоты, формирователь 3 импульсов, суммирующий счетчик 4, регистр 5, группу элементов И б перезаписи, второй триггер 7, вычитающий счетчик

8, блок 9 фиксации йуля и первый .триггер 10.

Работает устройстно следующим образом.

Формирователь 3 формирует импульсы начала и конца периода, которые произвОдят сброс делителя 2 частоты, перезапись состояния счетчика 4 импульсов в запоминающий регистр 5 и последующий сброс счетчика 4 импульсов. При этом от импульса начала периода до импульса конца периода в счетчике 4 импульсов формируется число N, Которое по окончании периода заносится в регистр 5. Через днухвходовые элементы 46 перезаписи число епс(+ (целая часть) иэ рес%.з гистра 5 перезаписывается в вычитающий счетчик 8 импульсов. Младший разряд числа N из запоминающего регистра 5 записывается в триггер

7 через трехвходовый элемент 46 перезаписи один раэ эа два раза открытия остальных двухвходовых элементов И б.

Если в младшем разряде числа и нуль, то на выходе триггера 7 устанавливается еДиничное состояние, открываюшее j k=t входы вычитающего счетчика 8, и первый после конца периода импульс тактовой частоты генератора 1 начинает производить вычитание импульсов счетчика 8 из числа М /2, .Как только в счетчике

8 устанавливается расстояние "0", срабатывает блок 9 и производит одновременно переброс триггера,10, что приводит к закрытию трехнходового элемента И 6 и перезапись числа . N в вычитающий счетчик 8.

Цикл вычитания повторяется и снова в конце его срабатывает блок 9, который перебрасывает триггер 10 в исходное состояние. Таким образом, триггер 10 производит деление на два выходной умноженной частоты из блока 9, а ввиду того, что в вычитающем счетчике 8 записывается число . и /Z а не Nq то частота

/ импульсов из блока 9 получается вдвое больше, что в общем не приводит к уменьшению коэффициента умножения.

В результате этого на выходе устройства получаются импульсы типа

"меандр", частота которых не уменьшается вдвое, что в свою очередь не приводит к увеличению погрешности измерения умноженной частоты.

Если в младшем разряде числа N единица, то на выходе триггера 7 устанавливается нулевое состойние, запрещающее по j.k-входам вычитающего счетчика его работу, и поэтому первый после конца периода импульс тактовой частоты .генератора 1 не начинает производить вычитание импульсов из счетчика 8, а перебрасывает триггер 7, что принодит к открытию j. k -входов счетчика 8 и началу вычитания из него числа

15 N< /2, . Как только в счетчике 8 установится состояние "0", срабатывает блок 9, он перебрасывает одновременно триггер 10, который в свою очередь закрывает трехвходовый эле;ф мент 4,6 и он же открывает двухвходовйй элемент И б и производит за-.. пись числа N /2 в счетчик 8.Цикл вычитания повторяется. Поэтому снова срабатывает блок 9, он перебрасывает триггер 10 в исходное состояние, что приводит н открытию всех элементов

И б, в результате в триггере 7 снова записывается "1" младшего разряда, а aN /2 . Триггер

7 снова не пропускает первый импульс генератора 1 на счетчик 8 и вычитание начинается с второго импульса. Процесс продолжается циклически до нового значения и, которое записы" вается в запомийающий регистр 5 в

35 конце последующего нового периода.

Таким образом, каждый импульс типа "меандр" выходной частоты умножителя получается в результате двух вычитаний числа и /2 счетчика 8.

В случае если в младшем разряде "0" и с учетом единицы младшего разряда регистра 5 на триггере 7, если число и /2 содержит дробную часть, т.е.

N содержит "1" в младшем разряде, то н первом цикле вычитается число.

1+ М /2, а во втором — и /2. При этом выходная частота . умноженного сигнала не уменьшается вдвое и получаемый на выходе умножителя сигнал типа "меандр" позволяет повысить точность измерения до величины +0,5 единицы младшего разряда, т.е.

-повышается стабильность показаний и улучшается условия синхронизации при использовании такого умножителя в информационно-измерительных системах

Формула изобретения

Умножитель частоты, содержащий генератор опорной частоты, выходом подключенный к управляющему входу вьтчитающего счетчика, выходы которого соедииены с входами бдока фикса

798831

ВНИИПИ Заказ 10056/67 . Тираж 756 Подписное

Филиал ППП "Патент", r. ужГоро3, ул. Проектная, 4 ции нуля, выход которого подключен к первым входам соответствующих элементов И группы, выходы которых, кроме элемента И группы младшего разряда, соединены с информационными входами вычитающего счетчика, а вторые входы элементов И группы — с выходами регистра, суммирующий счет-: чик, формирователь импульсов, вход которого является входом умножителя, отличающийсятем,что,с целью повышения точности,в него введены делитель частоты и два триггера причем счетный вход первого триггера подключен к выходу блока фиксации нуля, а выход подключен к выходу умножителя и к третьему входу эле- мента И группы младшего разряда,. выход которого подключен к раздельному входу второго триггера, выход которого подключен к входам младшего разряда вычитающего счетчика, а счетный вход — к выходу генератора опорной частоты и первому входу делителя частоты, второй вход кот. рого подключен к выходу формирователя импульсов, управляющему входу регистра и первому входу суммирующего счетчика, второй вход которого подключен к выходу делителя частоты, а выходы — к информационным входам регистра.

Источники информации, принятые во внимание при экспертизе

1.АвторСкое свидетельство СССР

Ф 498624, кл. G.06 G 7/16,,*

22.03.74.

2.Авторское свидетельство СССР

Р 503238, кл. G 06 F 7/52,.

28.06.74 (прототщр).