Устройство для решения системалгебраических уравнений

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕДЬСТВУ

Союз Сееетскии

Сецналнстнческнк

Республик

oi)798861 (61) Дополнительное к авт. свид-ву— (22) Заявлено 12. 07. 78 (21)2644543/18-24 с присоединением заявки Йо (23) Приоритет—

Ойубликоване 23.0181. бюллетень М 3

Дата опубликования описания 2301,81

М K ç

G 06 F 15/324

Государственный комнтет

СССР но делам нзобретеннй н открытий (5Ç) УА1(681.14 (088.8) (72) Автрры изобретения

Л.В.Дербунович, В.Ф.Евдокимов, Ю.A.Ïëþù и В.В.Шатилло

Институт электродинамики АН Украинской ССР и Харьковский политехнический институт (71) Заявители (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ

АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ

Изобретение относится к области вычислительной техники и может быть использовано для решения систем алгебраических уравнений.

Известны устройства, представляющие собой совокупность комбинационных решающих узлов, соединенных между собой в соответствии с математическим описанием решаемой задачи и искомое решение находится как установившееся значение переходного процесса в схеме с обратной связью (1).

Использование дискретных логических элементов для построения укаэанной совокупности комбинационных решающих узлов и функционирующих в схемах с обратной связью не всегда позволяет установиться схеме в устой. чивое состояние вследствие возникновения состязаний, вызванное разбросом параметров задержек логических элементов.

Наиболее близким по технической сущности является устройство, состоящее из группы сумматоров, выходы которых соединены с выходами устройства и с входами группы комбинационных масштабных узлов, выходы комбинационных масштабных узлов соединены соответственно с первой группой входов группы сумматоров, вторая группа входов группы сумматоров соединена с входами устройства 12).

Недостатком известного устройства является низкая достоверность решения из-за возникновения генерации, вследствие состязаний в схеме, вызванное разбросом параметров задержек логических элементов.

Целью изобретения является повышение достоверности решения.

Поставленная цель достигается тем, что в устройство, содержащее группу сумматоров, одни входы кото l5 рых подключены к выходам масштабных узлов группы, а другие входы — являются входами устройства, введена группа Д-триггеров, компарстор, элемент задержки и генератор одиночных

20 импульсов, причем выходы сумматоров группы соединены с первыми входами

Д-триггеров группы и с первой группой входов компаратора, выход которого через элемент задержки подключен ко входу генератора одиночных импульсов, выход которого соединен со вторыми входамй Д-триггеров группы, выходы которых соединены с второй группой входов компаратора и

ЗО входами масштабных узлов группы.

798861

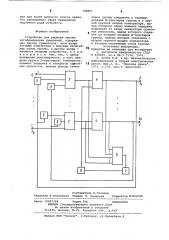

На чертеже представлена блок-схема устройства.

Устройство для решения систем алгебраических уравнений содержит входь устройства 1, группу сумматоров

2, группу масштабных узлов 3, группу Д-триггеров 4, выходы устройства

5, компаратор 6, элемент задержки генератор одиночных импульсов 8.

На входы 1 поступают значения сво бодных членов.Г F> заданной системы уравнений, представленной в матричном виде

Х =Вх+Р (1)

На,выходах 5 вырабатывается значение искомого вектора неизвестных х1-. х . На группе комбинационных масштабйых узлов 3 производится умножение искомого вектора неизвестных х †.х на постоянные коэффициенты мат"1 И .Г рицы В заданной системы уравнений (1). На группе сумматоров 2 произво- 20 дится суммирование частичных произведений искомого вектора неизвестных х - .х с коэффициентами матрицы В и с компонентами свободных членов F; .

Устройство работает следующим образом. В исходном состоянии выходы

Д-триггеров 4 группы находятся в соо. о стоянии х„-.х„, которое определяет начальный вектор неизвестных переменных х, а коэффициенты матрицы В задан- о ной системы уравнений (1) введены в группу масштабных узлов 3. При поступлении компонент свободных членов системы уравнений (1) F„ - .F„ на входы устройства 1 на выходах группы сумматоров вырабатывается новое значение вектора Х в течение времени Переходных процессов схемы. Компаратор 6 сравнивает поступающие на первую и вторую группы входов значения кодов и как только произойдет изменение 40 какого-либо входа, компаратор вырабатывает сигнал несоответствия, который поступает на элемент задержки 7.

Элемент задержки 7 задерживает выходной сигнал с компйратора 6 на время, 4 необходимое для того, чтобы все группы выходов сумматоров установились в устойчивое состояние.

По истечении времени задержки на элементе задержки 7 генератор одиноч- 0 ных импульсов 8 выдает импульс на входы синхронизации группы Д-триггеров 4 и производит запись значения кода на выходах группы сумматоров 2 в группу Д-триггеров 4. Новое значение кода, поступающее с выходов груп- 5 пы Д-триггеров 4 на вход группы масштабных узлов 3, умножается на коэффициенты матрицы В и,просуммировавшись со значениями свободных членов

F< -,F> на выходах группы сумматоров 2, Щ вырабатывает новое значение кода, которое сравнивается со значением кода на выходах группы Д-триггеров компаратором 6, который вырабатывает новый сигнал несоответствия и про- у цесс повторяется до тех пор, пока значения кодов на выходах группы сумматоров 2 и группы Д-триггеров 4 не совпадут по своему значению, которое и будет соответствовать искомому вектору неизвестных х„- .х заданной системы уравнений (1).

Для исключения неправильной работы устройства в схему включены задержки. Только при правильном выборе величин задержек можно устранить существенные и критические состязания в схеме.

На величины задержек накладываются два ограничения.

Первое — переключающий фронт такта подается на вторые входы Д-триггеров, когда их информационные входы находятся в устойчивом состоянии.

Следовательно. где t. — максимальная задержка в

1 Ма Х устройстве;

1 ИМ И с. „- минимальная задержка в устройстве;

t . — минимальная задержка в

L И11 1 компараторе 6 и генераторе 7; с — максимальное время эадержвгиси ки Д-триггера; о — время между первым и последним изменением входных переменных Г -:F>, подаваемых одновременно.

Второе — чтобы генератор одиночных импульсов 8 генерировал в течение перехода один импульс, а не несколько, что может произойти в результате состязаний между состояниями. Необходимо также длительность импульса или минимально возможный период срабатывания ограничить следующей величиной c > (t yzx ти n)+(t e>y, овцою)+

+ (t4woa t.м и), где с — .минимальное время переклювв1п чения Д-триггера;

tÄ Ä- максимальное время задержь иак ки в компараторе 6 и генераторе 7. Причем с3 а и Г определяется иэ данной элементной базы.

Использование дополнительных элементов схемы и новых связей между ними выгодно отличает данное устройство для решения систем алгебраических уравнений от известных, так как позволяет устранить состязания в схеме путем применения самосинхрониэации в цепи обратной связи с помощью Д-триггеров на время максимальной задержки в цепях групйы кслбинационных масштабных узлов и группы сумматоров и тем самым находить реше798861

Формула изобретения

Составитель H.Ïàëååâà

Редактор Н.Кончицкая Техред Н. Ковалева Корректор M.Ø Ð

Заказ 10057/68 Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная,4 ние для более широкого класса задач, что увеличивает сферу применения подобного рода устройств.

Устройство для решения систем алгебраических уравнений, содержащее группу сумматоров, олни входы которых подключены к выходам масштабных узлов группы, а другие входыявляются входами устройства, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности, в него введены группа Д-триггеров, компаратор, элемент задержки и генератор одиночных импульсов, причем выходы сумматоров группы соединены с первыми входами Д-триггеров группы и с первой группой входов компаратора, выход которого через элемент задержки подключен ко входу генератора одиночных импульсов, выход которого соеди" нен со вторыми входами Д-триггеров группы, выходы которых соединены с второй группой входов компаратора и входами масштабных узлов группы.

Источника информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 428405, кл.6 06 6 7/34, 1976.

2. Пухов Г.Е. и др. Математическое моделирование и теория электрических

15 цепей. Вып.2, К., "Наукова думка", 1973, с.3-8, рис.5 (прототип).