Интегратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ТЕЛЬСТВУ

Союз Советскнх

Соцналистнческих

Реслубннк ()798884 (61) Дополнительное к авт. свмд-ву (22) Заявлено 2704,79 (21) 276 796 4/18-24 с присоединением заявки М— (23) Приоритет (51)М. Кл.

G G 7/18

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 23.01,81 Бюллетень Н9 3 (53) УДК 681.335 (088.8) Дата опубликования описания 230181 (72) Авторы изобретения

Н.Т. Харин и A.Н. Харин (71) Заявитель (54) ИНТЕГРАТОР

Изобретение относится к дискретным системам управления и измерительной технике и предназначено для интегрирования дискретных сигналов °

Известен дискретный интегратор, реализующий интегрирование, например, по методам прямоугольника (Эйлера), трапеции 1/3 и 3/3 Симпсона, Уэддля и т.д., выполненные на сумматорах, усилителях, блоках памяти 11 .

Недостатком интегратора является малая точность при увеличении спектра частот входных сигналов.

Наиболее близким по технической сущности к предлагаемому является интегратор, Z-передаточная функция которого имеет вид:

Т 1+ 262 + Ы2 +Z

1 .1

5 1 1о у 1- <02 ъ -4 20 где Т вЂ” период дискретности, с.

2 =6

Известный интегратор содержит первый сумматор, первый вход которого через первый усилитель соединен с выходом ключа, вход которого является входом интегратора, четыре блока памяти, соединенные последовательно, вход первого блока памяти подключен, к выходу первого сумматора, соединен- з0 ному с первым входом второго сумматора, второй вход которого через вто-. рой усилитель подключен к выходу первого блока памяти, соединенному через третий усилитель со вторым входом первого сумматора, выход второго блока памяти через четвертый усилитель подключен к третьему входу второго сумматора, выход третьего блока памяти через пятый усилитель подключен к пятому входу второго сумматора и через последовательно соединенные инвертор и шестой усилитель соединен с третьим входом первого сумматора, четвертый вход которого через инвертор подключен к выходу четвертого блока памяти, выход которого соединен с пятым входом второго сумматора (2, Недостатком такого интегратора является снижение точности интегрирования при дальнейшем повышении частоты входных сигналов. Цель изобретения — повышение точности интегрирования.

Эта цель достигается тем, что в интегратор, содержащий первый сумматор, первый вход которого через первый усилитель соединен с выходом ключа, вход которого является входом интегратора, четыре блока памяти, 798884 соединенные последовательно, вход первого блока памяти подключен к выходу первого сумматора и к первому входу второго сумматора, второй вход которого через второй усилитель подключен к выходу первого блока памяти и через третий усилитель ко второ му входу первого сумматора, выход

:второго блока памяти через четвертый усилитель подключен к третьему входу второго сумматора, выход третьего блока памяти через пятый усилитель подключен к четвертому входу второго сумматора и через последовательно соединенные первый инвертор и шестой усилитель — с третьим входом первого сумматора, а выход четвертого блока памяти подключен ко входу второго инвертора, введены пятый блок памяти, три допОлнительных усилителя и третий инвертор, причем пятый блок памяти включен между выходом четвер того блока памяти и пятым входом второго сумматора, выход второго блока памяти через первый дополнительный усилитель подключен к четвертому входу первого сумматора, выход четвертого блока памяти через второй дополнительный усилитель подключен к шестому входу второго сумматора, выход пятого блока памяти через третий инвертор соединен с пятым входом первого сумматора, между шестым входом которого и выходом второго инвертора включен третий дополнительный усилитель.

Интегратор имеет передаточную функцию:

-2 -5„-4 . -5

12Бт +4ох -407. -252 -z )

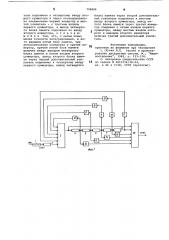

На фиг. 1 представлена функциональная схема интегратора, на фиг. 2 — 40 сравнительные амплитудно-частотные характеристики (АЧХ) различных интеграторов. Эти АЧХ рассчитаны на

ЭВМ ЕС-1020.

Интегратор содержит ключ 1, уси- 4 литель 2 с коэффициентом усиления

Т/б, первый сумматор 3 с шестью входами, пять последовательно соединенных блоков памяти 4-8, три инвертора 9-11, усилители 12-19 с коэффи- ур циентами усиления, равными соответственно 57, 30, 302, 57, 25, 40, 40, 25, второй сумматор 20 на шесть входов. Выход второго блока 5 памяти через первый дополнительный усилитель 17 соединен с четвертым входом сумматора 3; выход четвертого блока 7 памяти через цуррой дополнительный усилитель 15 и через инвертор 10 и третий дополнительный усилитель 19 соединены, соответственно, с шестыми входами второго 20 и первого 3 сумматоров, выход сумматора

3 соединен со входом сумматора 20 непосредственно и через пять последовательно соединенных блоков 4-8 па. мяти, последний блок 8 памяти является дополнительным, выход которого через инвертор 11 соединен с пятым входом сумматора 3.

Устройство работает следующим образом.

Дискретный сигнал х(КТ) с выхода ключа 1 через усилитель 2 поступает на сумматор 3, где суммируется с задержанными в блоках 4-8 паМяти, инвертированными в инверторах 9-11 и усиленными в усилителях 16-19 выходными сигналами блоков памяти.

Результирующие сигналы с первого сумматора 3 непосредственно и через те же пять последовательно соединенных блоков 4-8 памяти поступают на второй сумматор 20, где происходит их сложение с сигналами с выходов усилителей 12-15, на входы которых соответственно поступают сигналы с блоков памяти 4, 5, б, 7. Выходной сигнал х(КТ) в виде интеграла от входного сигнала х(КТ) снимается с сумматора 20. О точности интегратора можно судить по близости его частотной характеристики к характеристике идеального интегратора.

Из графиков на фиг. 2 видно, что

АЧХ предлагаемого интегратора ближе всех и в большем диапазоне частот расположена к АЧХ идеального интегратора, следовательно, его точность выше остальных дискретных интеграторов.

Например, при псевдочастоте 7=tvl2 относительные погрешности дискретных интеграторов имеют следующие значения: — известный интегратор 0 531Ъ предлагаемый интегратор 0,105%

Из этих данных видно, что предлагаемый интегратор значительно точнее известного, примерно в 5 раз.

Одновременно существенно расширен диапазон частот, в котором обеспечивается высокая точность интегрирования.

Формула изобретения

Интегратор, содержащий первый сумматор, первый вход которого через первый усилитель соединен с выходом ключа, вход которого является входом интегратора, четыре блока памяти, соединенные последовательно, вход первого блока памяти подключен к выходу первого сумматора и к первому входу второго сумматора, второй вход которого через второй усилитель подключен к выходу первого блока памяти и через третий усилитель ко второму входу. первого сумматора, выход второго блока памяти через четвертый усилитель подключен к третьему входу второго сумматора, выход третьего блока памяти через пятый усили798884

Фиг. тель подключен к четвертому входу второго сумматора и через последовательно соединенные первый инвертор и шестой усилитель — с третьим входом первого сумматора, а выход четвертого блока памяти подключен ко входу второго инвертора, о т л и ч а юшийся тем, что, с целью повышения точности интегрирования, в него введены пятый блок памяти, три дополнительных усилителя и третий инвертор, причем пятый блок памяти включен между выходом четвертого блока памяти и пятым входоМ второго сумматора, выход второго блока памяти через первый дополнительный усилитель подключен к четвертому входу 15 первого сумматора, выход четвертого блока памяти через второй дополнительный усилитель подключен к шестому входу второго сумматора, выход пятого блока памяти через третий инвертор соединен с пятым входом первого сумматора, между шестым входом которого и выходом второго инвертора включен третий дополнительный усилитель.

Источники информации, принятые во внимание при экспертизе

1. !Кузин Л.Т. Расчет и проектирование дискретных систем. М., "Машиностроение", 1962, с. 121-124.

2. Авторское свидетельство СССР по заявке 9 2610714/18-24, кл. G 0б G 7/18, 1978 (прототип).

798884

1,0. ор фиг.2

Составитель С. Белан

Редактор T. Кугрышева Техред Е.Гаврылешко Корректор И. Муска

Заказ 10060/70 Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4