Параллельный дешифратор на допол-няющих мдп-транзисторах"

Иллюстрации

Показать всеРеферат

ОПИС Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<11>798997

К АВТОРСКОМУ СВ ТЮЛЬСТВУ (61) Дополнительное к авт. саид-ау (51)М. Кл.з (22) Заявлено 281278 {21) 2703091/18-24 с присоединением заявки Но (23) Приоритет

Опубликовано 230181. Бюллетень Й9 3

Дата опубликования описания 2 30 181

G 11 С 8/00

Государственный комитет ссср по делам. изобретений и открытий (5З) УДКб 81. 327.67 (088. 8) (72) Авторы изобретения

В. B. Баранов, Ю. М. Герасимов, A.Н. Кармазин ский, Э.П.Савостьянов и В.П.Старенький (71) Заявитель (54) IIAPAJIJIEJIbHbIA ДЕ!3ИФРАТОР HA ДОПОЛНЯЮЦИХ

МДП- T P AH 3 И СТ OP AX

Изобретение относится к вычислительной технике и электронике и может быть использовано при постро ении микромощных интегральных запоминающих устройств (ЭУ).

Известны параллельные дешифраторы на одноканальных NgII-транзисторах статического и динамического типа, содержащее логические ячейки, состоящие из параллельной группы -транзисто- 10 ров и нагрузочного транзистора, на отношение размеров которых наЛожено ограничение (1.) и (2).

Однако эти дешифраторы потребляют значительную мощность в статическом 15 режиме и непригодны для ЗУ на дополняющих МДП-транзисторах.

Наиболее близким к предлагаемому является параллельный дешифратор на дополняющих МДП-транзисторах, содержа-20 дий логические ячейки, состоящие из группы параллельно соединенных транзисторов и коммутирующего транзисто ра р-типа, управляющего транзистора и транзистора обратной связи п-типа, 25 ,и логического элемента ИЛИ-НЕ,инвертор, одновходовой логический элемент

ИЛИ (схему повторения) с задержкой причем стоки управляющего транзистора, транзистора обратной связи, груп- 30 пы параллельно соединенных транзисторов подкл.,учены к первому входу логического элемента ИЛИ-НЕ, вторые входы которых и затворы управляющих транзисторов объединены во всех ячейках и подключены ко входу логического элемента ИЛИ с задержкой, вход которого подключен к выходу инвертора и к объединенньи во всех ячейках затворам коммутирующих транзисторов, истоки которых подключены к шине питания, а стоки — к истокам параллельно соединенной гругпы транзисторов, истоки транзисторов обратной связи и управляющих транзисторов подключены к шине нулевого потенциала, затворы транзисторов обратной связи подключены к выходам логических элементов ИЛИ-НЕ, затворы транзисторов параллельной группы, объединенные по дешифраторной схеме, подключены к прямым или инверсным адресным шинам дешифратора,вход инвертора — к стробирующей шине дешифратора (3).

Недостатком известного дешифратора является низкая надежность его работы, что связано с возможностью выборки в нем ложных адресов, пониженное быстродействие и сложная структура топологического чертежа, что

798997 обусловлено наличием последователь ого соединения коммутирующего тран истора и группы параллельно соединенных транзисторов . Кроме того, в динамическом режиме при отсутствии разрешающего строб-сигнала, дешифратор $ ютребляет значительную мощность, :вязанную с перезарядом больших ем<остей адресных шин.

Цель предлагаемого изобретения гнижение потребляемой мощности, позы- © аение быстродействия и надежности работы дешифратора и его упрощение.

Поставленная цель достигается тем, юто параллельный дешифратор на дополняющих МДП-транзисторах, содержаций логические ячейки, состоящие из группы параллельно соединенных тран-. зисторов р-типа,, управляющего транЗистора п-типа, транзистора обратной связи п-типа и логического элемента 26

ИЛИ-НЕ, логический элемент ИЛИ с зацержкой H первый инвертор, причем стоки всех транзисторов логической ячейки подключены к первому входу логического элемента ИЛИ-НЕ, истоки 2$ обоих транзисторов и-тйпа в логических ячейках - к шине нулевого потенциала, а затвор транзистора .обратной связи и-типа - к выходу логического элемента ИЛИ-НЕ, вторые входы логических элементов ИЛИ-НЕ объединены во всех логических ячейках и подключе ны к выходу логического элемента ИЛИ с задержкой, шину питания, адресные и стробирующие шины, дополнительно содержит второй инвертор с задержкой и адресные логические элементы И-НЕ, причем затворы управляющих транзисторов,п-типа. всех логических ячеек объединены и подключены к выходу первого инвертора .и к первому входу 40 логического элемента ИЛИ с задержкой, истоки параллельно соединенных транзисторов группы р-типа подключены к шине питания, затворы, объединен. ные соответственно и подключены к 4$ выходам адресных логических элементов

И-НЕ, .первые входы которых подключены соответственно к прямьм или инверсным адресным шинам дешифратора, вторые входы объединены и подключены к выходу второго инвертора с задержкой и ко входу первого инвертора, вход второго инвертора с задержкой и второй вход логического элемента ИЛИ с задержкой подключены к стробирующей шике дешифратора.

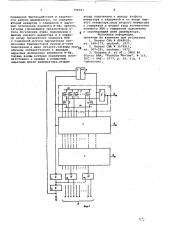

На фиг. 1 приведена схема дешифратора на дополняющих МДП-транзисторах) на фиг. 2 - временная диаграмма функционирования дешифратора.

Схема дешифратора содержит логичес-6О кие ячейки 1 состоящие из группы параллельно соединенных транзисторов

2 р-,типа, управляющего транзистора

3 й-типа,транзистора 4.обратной связи h-типа и логического элемента 6$

ИЛИ-НЕ 5, стоки всех транзисторов 2, 3 и 4 в ячейке объединены и подключены к первому входу логического элемента ИЛИ-НЕ 5, выходы логических элементов 5 являются выходами б дешифратора, вторые входы логических элементов 5 объединены во всех ячейках и.подключены к выходу логического элемента ИЛИ с задержкой 7, первый вход которого и объединенные во всех ячейках затворы управляющих транзисторов 3 подключены к выходу первого инвертора 8, вход которого и объединенные вторые входы адресных логических элементов,И-НЕ 10 подключены к выходу второго инвертора с задерж-; кой 9, первые входы 11 адресных логических элементов 10 являются прямыми и инверсными адресными шинами дешифратора, вход 12 второго инвертора с задержкой 9, объединенный со вторым входом логического элемента ИЛИ с задержкой 7 является стробирующей шиной дешифратора, в логической ячейке 1 .истоки 2 транзисторов р-типа подключены к шине 13 питания, истоки транзисторов И-тина 3 и 4 — к шине 14 нулевого потенциала, затвор транзистора 4 обратной. связи -подключен к выходу логического элемента

5, затворы транзисторов группы 2 в различных логических ячейках 1 объе динены по дешифраторной схеме и подключены к выходам адресных логических элементов И-НЕ 10.

Временная диаграмма содержит входной стробсигнал 15, адресный сигнал

16, управляющий сигнал на первом входе логического элемента ИЛИ c: задержкой 17, сигнал на затворах транзисторов параллельной группы

18, сигналы на первом и втором входах логического элемента ИЛИ-НЕ в ячейке 19 и 20, сигнал на выходе дешифратора 21.

Параллельный дешифратор на дополняющих МДП-транзисторах работает следу" ющим образом.

В исходном состоянии (режим невыборки) управляющий сигнал на стробирующей шине 12 соответствует логической 1 . На выходах всех адресных логических элементов 10 и первого инвертора 8 напряжения соответствуют также логической 1, в результате чего транзисторы группы 2 в каждой из логических ячеек 1 закрыты, а управляющие транзисторы 3 открыты.

На первых входах всех логических элементов ИЛИ-HE 5 в ячейках (стоках транзисторов параллельной группы) напряжение соответствует логическому 0 (выбранное состояние). Однако запрещаищий сигнал логической 1 на вторых входах этих элементов, подаваемый с выхода логического элемента HJIH c задержкой 7, приводит к тому, что на всех выходах 6 дешифрато798997 ра напряжения соответствуют режиму невыборки - логическому 0 . Транзисторы 4 обратной связи во всех ячейках дешифратора закрыты.

В режиме выборки на стробирующую шину 12 подается сигнал, соответствую- 5 щий логическому 0 . Управляющие транзисторы во всех ячейках закрываются. На вторых входах адресных логических элементов И-НЕ 10 потенциал изменяется на логическую 1 g

1О половина шин дешифратора, связанных /c затворами транзисторов параллельной

I группы, изменяет свой потенциал с логической . 1 на логический 0

В результате чего во всех ячейках дешифратора 5; кроме одной вйбраиной, 1$ открывается хотя бы однй иэ транзи .сторов параллельной группы и потенциал на первом входе элементов КЛИНЕ 5 этих ячеек устанавливаетоя равным логической 1 (невыбранное сос- Щ тояние). В одной выбранной ячейке транзисторы группы 2,управляющий тран. зистор З,транзистор 4 обратной связи закрыты и напряжение логического ., 0 на первом входе элемента ИЛИНЕ 5 сохраняется. После появления разрешающего сигнала, соответствующего логическому 0, на выходе элемента ИЛИ с задержкой 7 (вторых входах элементов 5) на выходе 6 выбранной ячейки устанавливается потенциал логической 1, а транзистор 4 обратной связи открывается, поддерживая, выбранное состояние ячейки. Для предотвращения появления ложных адресов необходимо, чтобы в невыбранных ячейках напряжение, соответствующее логической 1, на первом входе элементов 5 установилось раньше, чем появится разрешающий сигнал логического 0 на вторых входах этих элемен40 тов. Это условие обеспечивается выбором требуемой задержки логического элемента ИЛИ с задержкой 7.

После подачи на стробирующую шинУ 45

12 сигнала, соответствующего логической 1 (режим невыборки), в каждой из невыбранных ячеек транзисторы параллельной группы закрывается, а управляющий транзистор 3 открывает- gp ся. В результате чего на всех первых, входах элементов ИЛИ-НЕ 5 устанавливается напряжение, соответствующее выбранному состоянию — логическйй 0

Для предотвращейия появления ложных адресов необходимо, чтобы запрещающий сигнал логической 1 пришел на вторые входы элементов 5 раньше чем разрешающий сигнал логического 0 яа их первые входы. Это условие обеспечивается > во-первых, под- 60 ключеиием второго входа элемента ИЛИ с задержкой 7 к стробирующей шине

l2 и, во-вторых, вь1бором-требуемой . задержки второго инвертора с задержкой 9.Правильный выбор задержки эле- 6$ мента ИЛИ 7 и инвертора 9 предотвра / щает появление ложных адресов и гарантирует высокую надежность работы дешифратора. На практике логический элемент ИЛИ с задержкой реализуется последовательньик соединением элемента ИЛИ-НЕ и иивертора, инвертор с задержкой 9 — в виде последовательного соединения нечетного числа обычных инверторов (не больше трех).

Снижение динамической потребляемой мощности в дешифраторе по сравнению с известным обусловлено следующим.

Во-первых в режиме невыборки при

/ изменении адресных сигналов в дешифраторе перезаряжаются только входные емкости адресных элементов И-НЕ

10, которые значительно меньше, чем емкости шин дешифратора, связаннйе с затворами транзисторов группы 2.

Во-вторых, в режиме выборки в дешифраторе добиваются того, чтобы управляющие сигналы на затворы транзисторов группы 2 и управляющих транзисторов 3 приходили практически одновременно, устранив тем самым состав ляющую динамической мощности, связанную с протеканием сквозного тока через эти транзисторы.

В предлагаемой схеме дешифратора в логических ячейках отсутствуют последовательно соединенные однотипные транзисторы р-типа. В результате чего при заданной площади ячейки время ее переключения в состояние логической единицы уменьшается приблизительно в 3 раза, что приводит к повышению быстродействия схемы в целом на 15-303. Логические ячейки предлагаемы-о дешибратора имеют более простую .структуру топологического чертежа, а дешифратор в целом при числе выходов более 32 содержит меньше, транзисторов, чем известный.

Формула изобретения

Параллельный дешифратор на дополняющих МДП-транзисторах, содержащий логические ячейки, состоящие из группы параллельно соединенных транзисторов р-типа, управляющего, транзистора п-типа, транзистора обратной связи и-типа и логического элемента ИЛИНЕ, логический элемент ИЛИ с задержкой и первый инвертор, причем стоки транзисторов логической ячейки подключены к первому входу логического элемента ИЛИ-НЕ, истоки обоих транзисторов и-типа в логических ячейках — к шине нулевого потенциала, а затвор транзистора обратной связи п-типа - к к выходу логического элемента ИЛИ-НЕ вторые входы логических элементов ИЛИНЕ подключены к. выходу логического элемента ИЛИ с задержкой, шину питания, адресные и стробирующие шины, отличающийся . тем, что, с целью снижения потребляемой мощности

798997

ff

4 f повышения быстродействия и надехности работы дешифратора, он содержит второй инвертор с задержкой и адресные логические элементы И-НЕ, причем, .затворы управляющих транзисторов итипа логических ячеек подключены к выходу первого инвертора и к первому входу логического элемента ИЛИ с задержкой, истоки параллельно соединенных транзисторов группы р-типа подключены к шине питания, затворы под- ключены соответственно к.выходам адресных логических элементов И-НЕ, первые входы которых подключены соответственно к прямым и инверсным адресным шинам дешифратора,вторые входы подключены к выходу второго инвертора с задержкой и ко входу первого инвертора,вход второго инвертора с задержкой и второй вход логического элемента ИЛИ с задержкой подключены к стробирующей шине дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 4048629, кл. 340-173, опублик. 1977.

2. Патент США Р 3679911, кл. 307-251, опублик. 1972.

3. Onoyama A. at af,, CMOS 4К

Static RAM, "Toshiba 1teview", М 110, Jut.. — an/., 1977, р. 24, fig. 4

<прототип).

798997

Составитель Ю. Яааков

Техред T.Ìâòî÷êà . Корректор H. Швыдкая

Редактор Н. Рогулич

Заказ 10079/76 Тирах 656 Подписное

ВЧИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 3-35, Раушская наб., д. 4/5

Филиал ППП Патент, r . Ужгород, ул Проект ная, 4

Г

1 1

I 1

111