Блок памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Сеоэ Сфаетскик

Сециапистнчкких

Ркпублнк >799000

К АВТОРСКОМУ СВ ВПЛЬСТВУ (61) Дополнительное к авт. свид-ву

<о)м. к. (22) Заявлено 110479 (21) 2751274/18-24 с присоединением заявки М (23) Приоритет 03.05.78

G 11 С 11/02

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 23.01.81. Бюллетень Й9 3 (53) УДК6 81. 327. б 6 (088. 8) Дата опубликования описания 230181 (72) Авторы изобретения

И.К.Ростовцев, И.Р. Нозик и С.М.Василишин (71) Заявитель (54) БЛОК ПАМЯ 1 И

Изобретение -относится к вычислительной технике и может быть исполь зовано при построении схем считывания информации..

Известен блок памяти, который со» держит обмотки считывания, разделенные на секции, при этом несколько секций соединяются с входом усилите» ля считывания, например, через коммутируемые разделительные диоды (1).

Недостатком такого блока памяти является его низкая надежность.

Наиболее близким по технической сущности к предлагаемому изобретению является блок памяти запоминающЕго устройства, ссдержащий ферритовые сердечники, прошитые адресньвии и разрядными шинами, шиной считывания, разделенной на секции, усилители считывания, выходы которых; соединены с входами элемента ИЛЙ 121.

Недостатком такого .блока памяти также:является низкая надежность изsa возникающих помех в процессе считывания информации.

Цель изобретения — повышение надежностц блока памяти.

«азанная цель -достигается тем, что шины считывания, проходящие через ферритовые сердечники, прошитый

2 разными адресными и разрядным шинами, соединены параллельно и подключены ко входам соответствующих усилителей считывания.

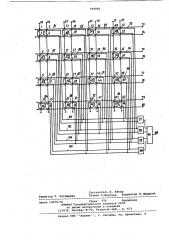

% На чертеже представлена структурная схема блока памяти.

Блок памяти содержит ферритовые сердечники 1-64, адресные шины 65-72, разрядные шины 73-80, шины 81-96

Ю считывания усилители 97-100 считывания, элемент ИЛИ 101, группы шин

102-105 считывания, выходную шину 106.

Шины 81, 86, 91, 96 считывания, охватывающие феррктовые сердечники

1-4, 21-24, 41-44, 61-64 соответственно, прошитые разньйи группами адресных и разрядных обмоток 65, 66 и 73, 74; 67,68 и 75, 76; 69,70 к 77,78)

71,72 и 79,80 соответственно соеди26 невы параллельно в группу 102 к подключены ко входу усилителя 9(считывания.

Аналогичнььс образом соединены в группы 103,104,105 шины считывания

25 82,87,92,93; 83,88,89,94; 84,85;90, 95 соответственно и подключены к усилителям 93,99,100 считывания соответствеенно. Выходы усилителей 97-100 считывания соединены со входами эле30 Мавта ИЛИ 101.

799000

Устройство работает следующим образом.

При считывании информации подаются полутоки выборки в одну иэ адрес ных шин 65-72 и в одну из разрядных шин 73-80. Один из сердечников 1-64, в котором суммируются полутоки выборки, выбирается и наводит рабочий сигнал в соответствующей шине считывания одной из групп шин 102-105 считывания, при этом в других шинах этой же группы сигналы помехи не наводятся, так как полувыбранные вердечники не охватываются этими шинами, т.е. эти шины считывания выполняют функцию шунтирующей нагрузки по отношению к шине,в которой наводится считанный 1S сигнал. Считанный сигнал состоит из рабочего сигнала, сигналов помех от полувыбранных сердечников и емкостных помех от полутоков выборки.

Вследствие различной мощности рабо- 20 чего сигнала и сигналов помех, помехи шунтируются эффективнее рабочего сигнала, что приводит к увеличению отношения рабочего сигнала к сигналам помех. 25

Считанный сигнал усиливается одним из усилителей 97-100 считывания и через элемент ИЛИ 101 подается на выходную шину 106. При этом коэффициент усиления должен быть больше, чем в том случае, когда к одному усилителю подключена одна шина считывания.

Возможно параллельное соединение

B группы и другого числа шин, начи- 35 ная с двух.

Введение параллельного соединения шин считывания в группу по предлагаемому принципу позволяет за счет увеличения отношения рабочего сигнала к сигналам помех расширить область работоспособности блока памяти, а также соответственно уменьшить количество упилителей считывания в блоке памяти;

Формула изобретения

Блок памяти, содержащий элементы памяти на ферритовых сердечниках, прошитые адресныаи и разрядными шинами во взаимно перпендикулярных направлениях, шины считывания, каждая из которых пропущена через группы ферритовых сердечников крест-накрест и усилители считывания, выходы которых соединены с соответствующими входами элемента ИЛИ, о т л и ч а ю щ ий с я тем, что, с целью. повышения его надежности, шины считывания, проходящие через ферритовые сердечники, прошитые разныаи адресными и разрядными шинами, соединены параллельно и подключены ко входам соответствующих усилителей считывания.

Источники информации, принятые во внимание при экспертизе

1. Патент CUJA 9 3487384, кл. 340-174, опублик. 1969.

2. Патент США М 3518640, кл. 340-174, опублик, 1970 (прототип).

799000

Составитель В. Вакар

Техред Т. Маточка Корректор Н Швыдкая

Редактор Т. Кугрышева

Филиал ППП Патент, r. Ужгород, Ул. Проектная, 4

Заказ 10079/76 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москват Ж-35, Раушская наб., д. 4/5