Доменное запоминающее устройство

Иллюстрации

Показать всеРеферат

CoIo3 Советских

Соцнапнстнчвскнх

Республик

ОПИСАНИЕ, р . ()799003

К АВТОРСКОМУ СВИДЕТИЗЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлеио280676 (21) 2377674/18-24 (51)M. с присоедииением заявки Йо

G 11 С 1lll4

А 11 С 19/08

Государствеинмй комитет

СССР ио делам изобретений н открытий (23) Приоритет

Опубликовано 230181.6þëëeòåíü 89 3 (53) УДК 628.327.6 (088. 8) Дата опубликования описания 23.01.81 (72) Автор изобретения

Л.Н.Падюков (71) Заявитель

Институт электронных управляющих машин (54) ДОМЕННОЕ ЗАПОМИНИОЦЕЕ УСТРОЙСТВО

j 95@ yP j лу - - ., Изобретение относится к вычислительной технике и может быть использовано при разработке накопителей информации большой емкости.

Известны доменные запоминающие 5 устройства, содержащие накопительный регистр, устройства считывания,, источники управляющего и смещающего полей. В таких устройствах требуется дополнительный чип для размещения 10 регистра синхронизации (11.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее накопительный регистр, блок управления, одни выхады 15 которого связаны с входами блока записи, а другие - с аниигилятором, датчики считывания, вход одного из которых подключен к .выходу накопительного регистра, а их выходы через уси- 20 литеяь считывания — ко входу .блока управления, регистры синхронизации, источники управляющего и смещающего полей, подключенньн. к другим входам блока управления (2). 25

При значительной длине накопительного регистра в таком устройстве регистр синхронизации занимает еедопус тимо много места на чипе, чем резко снижает коэффициент использования по- 30 леэной площади чипа, а, следователь - но,и его информационную емкость. С увеличением длины накопительного регистра увеличивается и количество регистров синхронизации, каждый иэ которых требует отдельногз устройства записи и считывания; в этом случае регистры синхронизации располагаются на дополнительном чипе.

Однако, если регистр синхронизации расположен на отдельном чипе, условия для него и для накопительного . регистра неодинаковы, так как поля смещения и управления имеют некоторую несднородность в пределах модуля.

Это может отрицательно сказываться на надежности работы устройства, так как его область устойчивой работы (ОУР) определяется меньшей.ОУР накойительного чипа и чипа синхронизации.

Целью изобретения является повышение информационной емкости и надежности устройства.

Указанная цель достигается путем введения в устройство элемента И, входы которого соединены с выходами регистров синхронизации, а выход со входом второго датчика считывания, причем длина накопительногэ регистра, 1,99003 выраженная в периодах доменопродвигающей структуры, равна произведению длин регистров синхронизации.

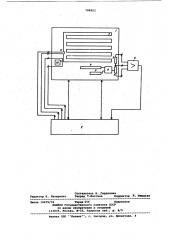

На чертеже изображено предлагаемое ,устройство.

На чипе 1 расположены накопительный регистр 2,.выход которого подключен ко входу первого датчика 3 считывания, регистры 4 и 5 синхронизации и элемент

И 6, входы которого связаны с выходами регистров 4 и 5 синхронизации, а выход - со входом второго датчика 7 считывания. Датчики 8 считывания через усилитель подключены ко входу блока 9 управления выходы которого подключены, соответственно, к расположенным на чипе устройству записи 10. и ан- И нигилятору 11.

Работа предлагаемого устройства показана на примере использования одного мостового магниторезистивного датчика, в два плеча которого вклю- 20 чены датчики 3 и 7 считывания. При этом датчик 3 считывания является рабочим датчиком для накопительного регистра 2 и компенсационным датчиком для регистров синхронизации, а з5 датчик 7 считывания является рабочил датчиком для регистров синхронизации и компенсационным для накопительного регистра.

В накопительном регистре 2 под .действием управляющего поля циркулирует основная информация таким образом, что между последним адресом информации и первым имеются свободные позиции. При прохождении их через рабочий датчик на выходе датчика 3 сигнал отсутствует. d этот промежуток времени на входы элемента И 6 одновременно приходят домены регистров синхронизации и на выходе элемента 6 появляется сигнал, который индициру- 40 ется датчиком 7, представляющим в этот момент рабочую часть мостового датчика. аким образом, происходит регистрация датчиком 7 считывания сигнала маркера начального адреса, 4я которая основана на получении различного вида сигналов от датчиков 3 и 7 считывания. Различие сигналов с датчиков 3 и 7 считывания, включенных в мостовую схему, может быть $0 и по полярности и по фазе. Для более надежной регистрации .маркера начального адреса датчик 7 считывания следует располагать так, чтобы считывание сигнала с элемента 6 происходило со сдвигом по .фазе относительно момента считывания информации датчиком 3 считывания (например, íà 180 ).

В предлагаемом устройстве регистры синхронизации имеют значительно меньшую длину йо сравнению с накопительным регистром, что позволяет расположить их на том же чипе и сэкономить полезную площадь чипа, а, следователь. но, увеличить. коэффициент его информационного использования и повысить надежность устройства в целом.

Использование двух датчиков считывания, включенных по мостовой схеме

I позволяет уменьшить количество датчиков считывания. Управление записью и стиранием информации в регистрах сийхронизации можно организовать с помощью проводниковых шин, одновре менно используемых для записи и стирания в накопительном регистре, т.е. без дополнительных выводов с чипа.

Таким образом, сокращается количество выводов с чипа прч выполнении функций синхронизации.

Формула изобретения

Доменное. запоминающее устройство содержащее накопительный регистр, блок управления, одни выходы которого связаны с входами записи, а другие - c аннигилятором, датчики считывания, вход одного из которых подключен к выходу накопительного регистра а их выходы через усилитель считывания - ко входу блока управления, источники:управляющего и смеща.ющего полей, подключенные к другим входам блока управления и регистры синхронизации, о т л и ч а ю щ е ес я тем, что, с целью повышения информационной емкости и надежности устройства, оно содержит, элемент И, входы котооро о соединены с выходами регистров сиихронизацйи, а выходс входом второго датчика считывания, причем длина накопительного регистра, выраженная в периодах доменопродвигающей структуры, равна произведению длин регистров синхронизации, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 481939, кл. G ll С 11/16, 27. 12.72.

2. Авторское свидетельство СССР

9 551694, кл. G 11 С 7/00, 04.08.75 (прототип).

799003

Состаэитель В. Гюрдонова

Редактор В. Лазаренко Техред Т.Маточка Корректор Й. Йзцдкал

ЮЮ

Заказ 10079/76 Тирам 656 Подписное

ВНИИПИ Росударстзенного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент ; г. Ужгород, ул. Проектная, 4