Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Сееэ Сееетекнх

Сецналнстнческнх

Реснублнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТИЗЬСТВУ (ii)799006 (61) Дополнительное к авт. свид-ву (22) Заявлено 100179 (21) 2711190/18-24 с присоединением заявки М2 (23) Приоритет

Опубликовано 2 01,81, Бюллетень Н9 3

Дата опубликования описания 2 3.0 1.81 51) М. („.З

Q11 С 17/00

Государственный комитет

СССР

IIo дмам изобретений и открытий (53) УДК681, 327. .66(088.8) (72) Автор и изобретения

И. Я. Козырь, Л. А . Коледов и О, A. Петросян

Московский институт электронной техники (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО что увеличивает количество паяных соединений, увеличивает паразитные емкости — уменьшается быстродействие, снижается надежность функционирования устройства, усложняется технология ее изготовления.

Наиболее близким по технической сущности .является ПЗУ, содержащее адресный дешифратор, выходы которого соединены с соответствующими входными шинами накопителя, состоящего из

rn секций, выходные шины. накопителя и шифратор, и шины управления по числу секций и вентили по числу выходных шин накбпителя, при этом все первые входы всех вентилей соединены с соответствующими выходными шинами накопителя, а вторые входы вентилей каждой секции объединены и подключены к соответствующей шине управления, выходы одноименных вентилей всех секций объединены между собой и подключены к соответствующему входу шиф ратора (2).

Однако в известном устройстве использование большого количества вентилей увеличивает паразитные емкосaи, уменьшает быстродействие устройства, увеличивает потребляемую мощИзобретение относится к вычислительной технике, в частности к мик-, роэлектронным запоминающим устройствам и может быть использовано в устройствах обработки цифровой информации в качестве постоянной памяти подпрограмм, табличных данных, гене-, раторов символов, функций и др.

Известно постоянное запоминающее устройство (ПЗУ), содержащее матричный накопитель с разрядными и числовыми шинами, подключенными к первым входам элементов И и к нагруэочным ре зисторам, инвертор, включенный между нагрузочным резистором и вторым вхо- 15 дом элемента И 11j.

Недостатки ПЭУ следующие большое количество схем управления - по входам X и по входам У, что увеличивает потребляемую мощность и 20 уменьшает быстродействие считывания информации; большое количество резисторов, инверторов и элементов И, что увеличивает потребляемую мощность, уменьшает быстродействие считывания информации; невозможность изготовления на одном кристалле накопителя, резисторов, инверторов и элементов совпадения, 30

799006. накопителя 4 на соответствующий вход элемента ИЛИ 6, с выхода которого сигнал поступает на соответствующий

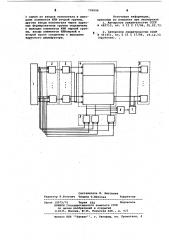

ПЗУ содержит адресный дешифратор

1, соответствующие выходы которого подключены к одноименным входам соответствующих элементов ИЛИ первой группы 2, выходы элементов ИЛИ первой группы подключены ко входам соответ ствующих адресных формирователей первой группы 3, выходная адресных формирователей первой группы подключены к соответствующим первым входам накопителя 4, причем одноименные входы 4$ элементов ИЛИ первой группы 2 подключены к одноименным входам соответствующих элементов ИЛИ второй группы 5, выходы элементов ИЛИ второй группы подключены к соответствую-- ® щим вторым входам накопителя 4, а также к соответствующим входам элемента ИЛИ 6, выход которого подключен к входу адресного формирователя 7, при этом выходы накопителя 4 подключены к одноименным входам соответствующих формирователей 8 считывания, а также к соответствующим выходам адресного формирователя 7.

ПЗУ работает следующим образом.

На одном (необходимом) выходе dO адресного дешифратора 1 вырабатывается низкий уровень напряжения U а на остальных выходах вырабатываются высокие уровни напряжения ()в . При этом сигнал через выбранный адресный 65

Формула изобретения ность, снижает надежность функционирования устройства.

Невозможность изготовления всех

Узлов ПЗУ на одном кристалле ограни чивает информационную емкость.

Кроме того, однокоординатная выбор- 5 ка является ограничивающим фактором увеличения информационной емкости, в результате для построения ПЗУ с боль шой информационной емкостью необходимо использовать большое количество кристаллов, а это уменьшает быстродействие устройства и снижает надеж- ность функционирования устройства.

Цель изобретения - повышение быст-. родействия устройства.

Поставленная цель достигается тем, 15 что в постоянное запоминающее устройство, содержащее адресный дешифратор и накопитель, введены группы элементов ИЛИ, группа адресных формирователей, группа формирователей считывания,2О элемент ИЛИ и адресный формирователь, выходы которого соединены с выходами накопителя и входами соответствующих формирователей считывания группы, вход адресного формирователя через элемент ИЛИ соединен с одним из входов накопителя и выходами элементов

ИЛИ второй группы другие входы накопителя через адресные формирователи г группы подключены к выходам элементов

ИЛИ первой группы, входы элементов

ИЛИ первой и второй групп соединены с выходами адресного дешифратора.

На чертеже представлена структурная схема предлагаемого ПЗУ; формирователь первой группы 3 поступает на соответствующие первые входы накопителя 4, а также через выбранный элемент ИЛИ второй группы 5 поступает на соответствующий второй вход вход аДресного формирователя 7,.на выходах последнего устанавливаются высокие уровни напряжения. При этом выбираются необходимые запоминающие элементы (по одному в каждой секции) и из накопителя 4 в .результате . считывается М-разрядное двоичное слово с помощью формирователей 8 считывания. После этого на выходах адрес ного формирователя второй группы 7 вырабатываются низкие уровни напряжения и происходит быстрый перезаряд паразитных емкостей.

По сравнению с известным предлагаемое ПЗУ имеет следующие преимущест. ва: введение элемента ИЛИ 6 и адресного формирователя 7 существенно повышает быстродействие устройства (происходит быстрая разрядка паразитных емкостей); отсутствие большого количества вентилей, в результате уменьшаются паразитные емкости {повышается быстродействие устройства); уменьшается задержка считывания информации (повышается быстродействие устройства}, повышается надежность функционирования устройства; упрощение технологии изготовления устройства; введение адресных формирователей первой группы и элементов ИЛИ первой и второй групп позволяют построить

ПЗУ с большой информационной емкостью (считывание информации осуществляется двухкоординатной выборкой), уменьшаются параэитные емкости (повышается быстродействие устройства), уменьшается количество паяных соединений (повышается быстродействие и надежность функционирования устройства) .

Постоянное запоминающее устройство, содержащее адресный дешифратор и накопитель, о т л и ч а ю щ е с я тем, что, с целью повышения быстродействия, в него введены группы элементов ИЛИ, группа адресных формирователей, группа формирователей считывания, элемент ИЛИ и адресный формирователь, выходы которого соединены с выходами накопителя и входами соответствующих формирователей считывания группы, вход адресного формирователя через элемент ИЛИ соединен

799006

Составитель Л. Амусьева

Редактор H.Рогулич Техред T.Маточка Корректор

Подписное

Эаказ 10079/76 Тираж 656

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. ужгород, ул. Проектная, 4 с одним из входов накопителя и выхо дами элементов ИЛИ второй группы, другие входы накопителя через адресные формирователи группы подключены к выходам элементов ИЛИ первой группы, входы элементов ИЛИнервой и второй групп соединены с выходами адресного дешифратора.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР

Р 483713, кл. 6 .11 С 17/06, 05.02.73.

2, Авторское свидетельство СССР

9 461451, кл. 0 11 С 17/06i 19.12.73 (прототип),