Сдвигающий регистр

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ CoIo3 Советских

Соцнвпнстнческнх

Респубнни

G 11 С 19/00

Фваударатавиный каматат

СССР ае делам нзеаретеник и открытей

Опубликовано 23.01.81 Бюллетень Лв 3

Дата опубликования описания 23.01.8! (53) УД К681.3 (088Я) (72) Авторы изобретения

В.И.Редченко, В.В.Куванов, Г.А.Кузьмин и В.М (7I) Заявитель (54) СДВИГАЮЩИЙ РЕГИСТР

Изобретение относится к автоматике и вычислительной технике и может быть использовано в счетно-решающих устройствах для преобразования параллельного кода в последовательной н обратной операции, а также для реализации функции сдвига.

Известен сдвигающий регистр, содержащий пару триггеров в каждом разряде (1).

Наиболее близким техническим решением к предлагаемому изобретению являетсяссдвнгающий то регистр,содержащий в каждом разряде информационный и буферный триггеры, построенные на основе элементов И-ИЛИ с перекрестными связями (2}. .

Недостатком известных сдвигающих регистров, является их сложность, поскольку на каждый разряд информационного слова приходится нара триггеров.

Целью изобретения является упрощение сдвигаю щего регистра.

Поставленная цель достигается тем, что сдвигающий регистр, содержащий триггеры памяти и бу-. . ферные триггеры, каждый из которых состоит нз двух элементов И-ИЛИ, причем выходы перво.

2 го и второго элементов И-ИЛИ подключены к первому иэ неГ ой группы входов соответственно второго и первого элементов И-ИЛИ, содержит.дополнительный триггер, причем выход первого н выход второго элементов И-ИЛИ i-го ,буферного триггера (i=1,...,n; 2n - число разрядов сдвигающего регистра) подключены к первому входу второй грунпы первого элемента И-ИЛИ соответственно (2i-1) -го и 2i-ro триггеров памяти, выход первого и выход второго элементов И-ИЛИ (2j- l)-го тр птера памяти (j= 1,...,n-1) подключены к первому входу второй группы соответственно первого и второго элементов И-ИЛИ (+!)-ro буферного триггера, выход первого н выход второго элементов И вЂ” ИЛИ 2j-го триггера памяти (=1,...,n-1) подключены к первому входу третьей группы соответственно первого и второго элементов И-ИЛИ ()+1)-го буферного триггера, вторые. входы второй и третьей групп элементов

И-ИЛИ всех буферных триперов подключены к первому тактовому входу, а вторые входы вторых групп элементов И-ИЛИ всех триггеров памяти, а также счетный вход дополнительного триггера — ко второму тактовому входу сдвигаюФормула изобретения

3 79900 щего регистра, прямой выход дополнительного триггера подключен к третьим входам второй группы элементов И-ИЛИ всех буферных триггеров и триггеров памяти с номерами 21 -l, инверсный выход дополнительного триггера — к третьим входам третьей группы элементов И-ИЛИ всех буферных триггеров и к третьим входам второй группы элементов И-ИЛИ триггеров па мяти с номерами 2i, вторые входы второй группы элементов И-ИЛИ, первого буферного М триггера являются информационными входами, а выходы (2n-1)-ro и 2п-го триггеров памяти информационными выходами сдвигающего регистра.

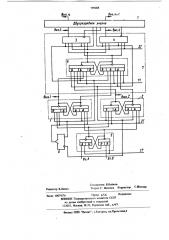

Функциональная схема сдвигающего регистра д представлена на чертеже. устройство содержит информационные триггеры памяти 1.4, буферные триггеры 5 и 6, двухразрядные ячейки 7,образованные парами информационных и одним буферным триггероь|, дополнителыгый триггер 8.

Сдвигающий регистр работает следующим образом.

Первый тактовый импульс на шине 1 Т вызывает прием информации со входов А и Б в первый буферный триггер 5 и передачу информации из левого (правого) ряда, информационных триггеров в соответствующие буферные триггеры последующих ячеек и на выходы сдвигающего регистра. Первый тактовый импульс на шине

2 Т вызывает передачу информации из буферных триггеров в информационные триггеры левого (правого) ряда своих ячеек и изменяет состояние дополнительного триггера 8. Вторые тактовые импульсы по шинам 1Т и 2Т вызывают ана. ЗЮ логичные действия, но с участием правого (лево го ряда информационных триггеров, что.определяется состоянием дополнительного триггера. В . результате происходит сдвиг информации на одну двухразрядную ячейку и r.ä.

В предлагаемом регистре на каждую пару информационных разрядов приходится всего лишь один буферный триггер.

Сдвигающий регистр, содержащий триггеры памяти и буферные триггеры, каждый из которых состоит из двух элементов И-ИЛИ, причем выхо8 ф ды первого и второго элементов И-ИЛИ подключены к первому иэ первой группы входов соответственно второго и первого элементов И-ИЛИ, отличающийся тем, что.с целью упрощения сдвигающего регистра, он содержит дополнительный триггер, причем выход первого и вцход второго элементов И-ИЛИ i-ro буферного триггера (И,...,n; 2n - число разрядов сдвигающего регистра) подключены к первому входу второй группы первого элемента И-ИЛИ соответственно

Ф (2i-1)-ro и 2i-го триггеров памяти, выход первого и выход второго элементов И-ИЛИ (2)-1)ro триггера памяти (1=1,...,п-1) подключены к первому входу второй группы соответственно первого и второго элементов И-ИЛИ (j+1)-го буферного триггера, выход первого и выход второго элементов И-ИЛИ 2 j -ro триггера памяти ()=1,...,n-1) подключены к первому входу третьей группы соответственно первого и второго элементов И-ИЛИ (+1)-го буферного триггера, вторые входы второй и третьей групп элементов И-ИЛИ всех буферных триггеров подключены к первому тактовому входу, а вторые входы вторых групп элементов И-ИЛИ всех триггеров памяти, а также счетный вход дополнительного триггера — ко второму тактовому входу сдвигающего регистра, прямой выход дополнительного триггера подключен к третьим входам второй группы элементов И-ИЛИ всех буферных триггеров и триггеров памяти с номерами 2i-1, инверсный выход дополнительного триггера- к третьим входам третьей группы элементов И вЂ” ИЛИ всех буферных триггеров и к третьим входам второй группы элементов И-ИЛИ триггеров памяти с номерами 2i, вторые входы второй группы элементов И вЂ” ИЛИ первого буферного триггера являются информационными входами, а выходы (2n-1) -го и 2п-го триггеров памятиинформационными выходами сдвигающего регистра.

Источники информации, принятые во внимание при экспертизе

1. Букреев Н.Н. и др. Микроэлектронные схемы цифровых устройств. М., Советское радио", 1973.

2. Шляпоберский В.Н. Основы техники передачи дискретных сообщений. М,, Связь", 1973, с.109, рис.3.5, (прототип).

799008 бала.п

Составитель В.Банков

Техрсд Т. Маточка Корректор С.Шекмар

Редактор ВЛанко

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4

Заказ 10079/76 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открьпий

113035, Москва, Ж-35, Раушская наб., д.4/5