Ячейка памяти для буферногорегистра

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социаяистичесиих

Респубяик он799010 (61) Дополнмтаенюе н авт. свмд-ау 9 661606 (22) З 12О4.79 (21) 2751957/18-24 (23) Приоритет

Оаубамнееане 2301.81, бюллетень ЙВ 3

Дата опубликования описания 230)З1 (51)М. Кя.

G 11 С 19/ОО

Государственный комитет

-СССР по делам изобретений и открытий (53) УДК681. 327.66. (088. 8) P2) Автор иэабрвтаиия

Б.С.Цнрлнн (П ) Заявитель

Институт социально-экономических прОблем АН СССР (54) ЯЧЕЙКА ПАМЯТИ ЦЛЯ БУФЕРНОГО

РЕГИСТРА

Изобретейие относится к вычис.лительной технике, в частности к технике запоминающих устройств,и может быть использовано при проектировании буферных запоминающих устройств.

Известна по основному авт. св °

Р 661606 ячейка памяти, которая содержит три элемента И-ЙЛИ-НЕ, включенные по схеме трехстабильного триггера так,что входы первого элемента 10

И каждого из элементов И-ИЛИ-НЕ соединены с выходами двух других элементов И-ИЛИ-НЕ, и шесть входных шин,соединенных со входами вторых элементов И элементов И-ИЛИ-НЕ в следующем поряд« т5 ке.

Первая шина соединена со входамй первого и третьего элементов И-КЛИНЕ, вторая — со входами первого и второго, третья - со входом первого, а 29 четвертая, пятая и шестая - со входами второго и третьего элементов ИЯЛИ-НЕ (11.

Однако в буферном регистре (pipe, line), состоящем из ячеек памяти 25 указанного типа, каждая порция информации продвигается от первой ячейки к последней, причем время, через. которое информация появляется на выходе регистра,зависит как от собствен-30

2 ных (реальных) задержек элементов последнего, так и от его заполнения информацией, т.е. в регистре неизвест» но, находится ли в данный момент времени 1-й разряд сдвигаемого кода в

1-й ячейке памяти регистра,а также неизвестно, когда этот разряд попадет в 1 -ю ячейку. Следовательно, из такого регистра нельзя осуществлять параллельное считывание информации,что ограничивает его функциональные возможности н является недостатком.

Цель предлагаемого иэобретения— расширение области применения ячейки памяти за счет обеспечения параллельного считывания из нее информации.

Поставленная цель достигается тем, что ячейка памяти для буферного регистра содержит дополнительный трехстабильный триггер, выполненный на трех элементах И-ИЛИ-HE и четыре дополнительные входные шины, первая, вторая и третья из которых соединены соответственно с первым, вторым и третьим дополнительными входами первого элемента И-ИЛИ-НЕ основного трехстабильного триггера, первый и второй входы первого элемента И-ИЛИ-HE дополнительного трехстабильного триггера соединены с первыми и вторыми дополнитель799010. ными входами второго и третьего элементов И-ИЛИ-НЕ основного трехстабильного триггера и первой и второй основными входными шинами, выход второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера подсоединен к третьим и четвертым дополнительным входаы второго и третьего элементов И-ИЛИ-НЕ основного трехстабильлого триггера, выход третьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера соединен с пятыми и шестыми дополнительными входами второго и третьего элементов

И-ИЛИ-НЕ основного трехстабильного триггера, первые выходы второго и третьего элементов И-ИЛИ-НЕ дополни- 15 тельного трехстабильного триггера соединены с седьмыми дополнительными входами второго и третьего элементов

И-ИЛИ-НЕ основного трехстабильного триггера и с четвертой дополнительной gp входной шиной, четвертый, пятый и шестой дополнительные входы первого элемента И-ИЛИ-НЕ основного трехстабильного триггера соединены со вторыми, третьими и четвертыми входами второго и третьего элементов И-ИЛИ-2

НЕ дополнительного трехстабильного триггера и третьей,. четвертой и пятой основными входными шинами, выход второго элемента И-ИЛИ-НЕ основного грехстабильного триггера соединен с Çp четвертым входом второго элемента

И-ИЛИ-НЕ дополнительного трехстабильного триггера, пятый вход второго элемента И-ИЛЙ-HE которого подключен к выходу первого элемента И-ИЛИ-HE 35 эсновного трехстабильного тригГера и к пятому входу третьего элемента

И-ИЛИ-НЕ дополнительного трехстабильного триггера, выход третьего элемента И-ИЛИ-НЕ основного трехстабильного О триггера соединен с шестым входом тре. тьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера.

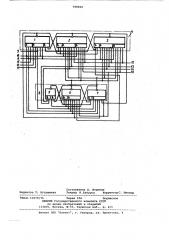

На чертеже представлена функциональная схема предлагаемой ячейки памяти для буферного регистра. 4S

Устройство содержит элементы

4-ИЛИ-НЕ 1-3 основного трехстабильюго триггера 4, элементы И-ИЛИ-НЕ

>-7 дополнительного трехстабильного григгера 8, основные входные шины Ы

)-14, дополнительные входные шины

15-18.

Ячейка работает следующим образом.

Основной триггер предлагаемой ячейки. памяти имеет три устойчивых состояния, которые определяются значениями на выходах элементов 1,2,3;.

011 — информация в триггере

4 отсутствует, 110 — в триггере. 4 записана 6р

"1"

У

101 — в триггере 4 записан

"0"

Аналогичные состояния имеет и дополнительный триггер 8. 6S

Пока в дополнительном триггере 8 отсутствует информация, изменение со стояний основного триггера происходит так же, как и в известном устройстве.

Условием записи (стирания) информации в 1-й ячейке в этом режиме является отсутствие (наличие) информа-, ции в (+1)-й и наличие (отсутствие) информации в (1-1)-й ячейках соответственно. При этом запись (стирание) информации в 1-й ячейке происходит

4ерез элементы 2,3(Х)

Пусть теперь в (j+1)-й ячейке оказался (i+1) -й разряд сдвигаемого кода, в результате чего в дополнительный триггер 8 (i+1). — и ячейки записалась информация, этот триггер оказался в состоянии 110 или 101. Эти состояния дополнительного триггера 8 (i+1)-й ячейки разрешают перепись информации из (1 -1)-й ячейки в -ю ячейку через элементы 2 и 3. При этом, очевидно в 1 -ю ячейку запишется I-й разряд, сдвигаемого кода,а в (i-1) -й ячейке информация будет стерта. Условием пе реписи информации из основного триггера 4 1 -й ячейки в ее дополнительный триггер 8 является наличие информации в основном 4 и дополнительном триггерах 8 (i+1)-й ячейки и отсутствие информации в (1-1)-й ячейке. Эти условия являются признаком того, что в

j-ю ячейку записан 1-й разряд сдвигаемого кода.

Таким образом, информация на выходах элементов б и 7 1-й ячейки появляется только после того, как в этой ячейке окажется записанным 1-й разряд сдвигаемого кода, что позволяет осуществить параллельное считывание информации из буферного регистра;

Возврат 3-й ячейки памяти буферного регистра в исходное состояние происходит в следующем порядке.

Сначала стирается информация в основном триггере 4 -й ячейки (условием этого является отсутствие информации в основном 4 и наличие ее в дополнительном триггере 8 (-1)-й ячейки соответственно), а затем стирается информация в дополнительном триггере

8 -1 -й ячейки (условием этого является отсутствие информации в основном триггере 4 (i +1 -й ячейки.

Процесс установки ячеек буферного регистра в исходное состояние распространяется последовательно от первой ячейки к п-й, причем как только 1-я ячейка оказывается в исходном состоянии (т.е. отсутствует информация в ее основном 4 и дополнительном триггерах 8), она снова может принимать информацию из (-1)-й ячейки.

При этом пока дополнительный триггер

8 1-й ячейки хранит информацию (находится в состоянии 110 или 101), запись информации в ее основной триггер 4 блокируется и поэтому запись

799010 очередного П -разрядного кода в регистр можно начинать сразу после того, как его первая ячейка установится в исходное состояние (не дожидаясь установки в это состояние всех ячеек регистра), В предлагаемой ячейке памяти время записи(стирания)информации в режиме простого сдвига составляет 2 (,средняя задержка одного элемента ИИЛИ-НЕ),а в режиме сдвига с параллельным считыванием — 4 .

Хотя предлагаемая ячейка памяти ® содержит дополнительное оборудование

1по сравнению с известной ячейкой (дополнительный трехстабильный триггер ), однако общий объем оборудования, необходимый для построения буферного И регистра (типа jjpegiee,), не увеличивается: в том и другом случае буферный регистр для хранения и-разрядного кода должен содержать 2 П трехстабильных триггеров. 26

Аналогичный вывод можно сделать и о быстродействии буферного регистрами сдвиг кода на и разрядов производится. за время, равное 4Ы, как в регистре из известных ячеек памяти, так и s регистре нз предлагаемых ячеек памяти.

Буферный регистр. (типа р(рб иф), построенный на основе предлагаемых ячеек памяти, позволяет осуществлять параллельное считывание информации и его целесообразно использовать для, преобразования последовательного кода в параллельный.

Формула изобретения ЭЗ

Ячейка памяти для буферного регистра по авт. св. э 661606, о т л ич а в щ а я с я тем, что, с öåëüâ расширения области применения ячейки памяти за счет обеспечения возможно- 40 сти параллельного считывания информации, она содержит дополнительный трехстабильный триггер, выполненный иа трех элементах И-ИЛИ-НЕ, и четыре дополнительные входные шины, первая, 45 вторая и третья из которых соединены соответственно с первым, вторым и третьим дополнительными входами нервого элемента И-ИЛИ-НЕ основного трехстабильного триггера, первый и второй входы первого элемента И-ИЛИ"НЕ дополнительного трехстабильного триггера соединены с первыми и вторыми дополнительными входами второго и третьего элементов И-ИЛИ-HE основного триггера и первой и второй основными входными шинами, выход второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера подсоединен к третьим и четвертым дополнительным входам второго и третьего элементов

И-ИЛИ-НЕ основного трехстабильного триггера, выход третьего элемента КИЛИ-НЕ дополнительного трехстабильного триггера соединен с пятыми и шес- тыми дополнительными входами второго и третьего элементов И-ИЛИ-HE основного трехстабильного триггера, первые выходы второго и третьего элементов

И-ИЛИ-НЕ дополнительного трехстабильного триггера соединены с седьмыми дополнительными входами второго и третьего элементов с четвертой дополнительной входной шиной, четвертый пятый и шестой дополнительные входй . первого элемента И-ИЛИ-НЕ основного трехстабильного триггера соединены со вторыми и третьими и четвертыми входами второго и третьего элементов

И-ИЛИ-НЕ дополнительного трехстабильного триггера и третьей, четвертой и пятой основными входными шинами, выход второго элемента И-ИЛИ-НЕ основного трехстабильного триггера соединен с четвертым входом второго элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера, пятый вход второго элемента И-ИЛИ-НЕ которо- . го подключен к выходу первого элемента И-ИЛИ-НЕ основного трехстабильного триггера и к пятому входу третьего элемента И-ИЛИ-НЕ дополнительного трехстабильиого триггера, выход третьего элемента И-ИЛИ-ИЕ основного трехстабильного триггера соединен с шестым входом третьего элемента И-ИЛИ-НЕ дополнительного трехстабильного триггера.

Источники информации, принятые во. внимание при экспертизе

1. Авторское свидетельство СССР

9 661606, кл. 6 11 С 19/00, 12.03.74.

799010

Составитель A. Воронин

Техред Н.Бабурка КорректорС. Шекмар

Редактор Т. Кугрышева

Заказ 10079/76 Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Ю

13 и