Устройство для контроля блокапостоянной памяти

Иллюстрации

Показать всеРеферат

Союз Сеаетскнк

Соцнавктнческик

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТ©РСКОММ C ИЛЬСТВУ

<щ799019 (61) Дополнительное к авт. сеид-еу(я)М. Кл3

G 11 С 29/00 (22) ЗаявленО 10 .04 Л9 (21) 27Ы82у18-24 с присоединением эалвкн й9— (23) Приоритет—

ГосударствекиыА комятет

СССР по дедам язобретеняй к открытяА

Опубликовано 23,01.81. Бюллетень N9 3

Дата опубликования описания 23 .01 .81 (33) УДК 681.32 (088.8) P2) Автор изобретения

В . A . Носачев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯННОЙ ПАИЯТИ

Изобретение .относится к запоминающим устройствам.

Известно устройство для контроля блока постоянной памяти, которое содержит блок управления, подключенный к счетчику адреса, связанному с блоком индикации адреса и проверяемым блоком постоянной памяти (БПП), сумматор, входы KoToporo соединены с выходами поверяемого блока и блока управления, выходы - co входом схемы сравнения, вЪ ход которой подключен к блоку управления .

В этом устройстве операция суммирования считанной с БПП информации осуществляется за время нескольких рабочих обращений к одному адресу с использованием информации, выведенной эа одно обращение (1).

Недостатком устройства является невозможность контроля достоверности считывания информации второго и последующих обращений к одному адресу проверяемого БПП при неустойчивом считывании.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для контроля постоянного запоминающего блока, содержащее регистр числа, выходы которого подключены к одним входам схемы сравнения, вторые входы которой подсоединены к выходам БПП, а выход - к блоку управления, подсоединенного к счетчику адресов, подключенному ко входам ПЗБ и блок вентилей, информационные входы которого подключены к другим входам схемы сравнения, управляющие входы объединены н подключены к блоку управления, а выходы лодкточены ко входам регистра числа (2).

Однако это устройство, условно принимая информацию, считываемую с проверяемого ВПП в первом обращении

1В по адресу, за эталонную, не обеспечивает контроля достоверности считанной информации из БПП в первом обращении .

Цель изобретения - повмаение дос20 товерности контроля считанной информации.

Поставленная цель достигается тем, что в устройство для контроля блока постоянной памяти, содержащее счетчик, регистр числа, первую схему сравнения, элементы И и блок управления, причем выходы регистра числа подключены к одним из входов первой схеьва сравнения, другие входы которой сое-, 30 динены со входами устройства, а вы-

799019 ход подключен к первому входу блока управления, первый и второй выходы которого соединены с первым выходом устройства и входом. счетчика, выход которого соединен со вторым выходом устройства, один из входов элементов

И подключены к третьему выходу блока управления, другие входы соединены со входами устройства, а выходы - с входами регистра числа введены сумматор, вторая схема сравнения и дополнитель- о ный регистр, причем входы второй схемы сравнения подключены соответственно к выходам дополнительного регистра и выходам сумматора, один из входов которого соединен с четвертым выходом блока управления, другие входы сумматора соединены с выходами регистра числа, выход второй. схемы сравнения подключен ко второму входу блока управления .

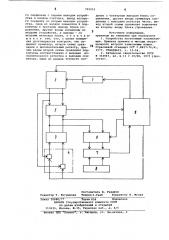

На чертеже изображена структурная 20 схема устройства для контроля блока постоянной памяти.

Устройство содержит счетчик 1, служащий для образования кодов адресов, выбираемых из БПП 2 чисел, ре- д гистр 3 числа, используемый для хранения кодов чисел ° БПП, вводимых с помощью группы элементов И 4, первую схему 5 сравнения, сумматор б, исполь— зуемый для циклического суммирования кодов чисел, считываемых с БПП 2,на регистр 3 числа, вторую схему 7 сравнения, используемую для сравнения содержимого сумматора 6 с кодами чисел, задаваемыми дополнительным регистром 8, хранящим контрольную сумму массива чисел БПП 2 . Синхронизация работы перечисленных блоков осуществляется блоком 9 управления, первый второй и третий выход которого соединены соответственно с первым выхо- 4р дом устройства, входом счетчика 1 и одними из входов элементов И 4, а первый вход блока 9 подключен к выходу cxema 5 сравнения .

Входы схемы 7 сРавнения подключе- 4 ны соответственно к выходам регистра

8 и выходу сумматора б,.один из входов которого соединен ° с четвертым выходом блока 9 . Другие входы сумматора б соединены с выходами регист- о ра 3. Выход схемы 7 сравнения подключен ко второму входу блока 9.

Устройство работает следующим образом.

Блок 9 управления формирует серию

К обращений по каждому адресу заданного массива адресов блока 2. Информация блока 2, считываемая при первом обращении к проверяемому адресу, передается в регистр 3 числа с помощью элементов И 4 сигналом от блока 9 gp управления и в сумматор б сигналом с блока 9 управления, При последующих (к-1) обращениях производится поразрядное сравнение считываемых из блока 2 кодов чисел с кодом числа регистра 3. В случае их совпадения формируется код следующего контролируемого адреса счетчиком

1, блок 9 управления формирует К обращений по следующему адресу, причем информация блока 2, считанная при первом обращении, передается в регистр 3 числа и в сумматор 6, где происходит сложение этой информации с содержимым сумматора б. В случае несовпадения кодов чисел, считываемых из блока 2, с кодом числа регистра 3, хотя бы при одном из (к-1) обращений по контролируемому адресу блоком 9 управления прерываются обращения к блоку 2, производится останов устройства, а разряд и адрес сбоя определяются состоянием регистра 3 числа счетчика 1 и выходного регистра числа блока 2.

При отсутствии сигнала неисправности со схемы 5 сравнения при (к-1) обращениях по каждому контролируемому адресу заданного массива адресов блока 2 после сложения кода числа, считанного из блока 2 по последнему адресу заданного массива адресов схемой 7 сравнения производится сравнение содержимого сумматора б с кодом, выдаваемым регистром 8. В случае совпадения блок 9 управления в зависимости от заданного режима либо производит останов с индикацией благополучного исхода контроля заданного массива адресов, либо формирует повторное обращение к заданному массиву адресов блока 2 . В случае несовпадения образованной сумматором 6 суммы кодов чисел заданного массива с кодом числа, выдаваемым регистром 8, блок 9 управления производит останов с индикацией неблагополучного исхода контроля заданного массива блока 2 по контрольной сумме. Разряд и адрес сбоя в этом случае определяются методом последовательного уменьшения задаваемого массива адресов проверяемого блока 2.

Введение в состав устройства для контроля блока постоянной памяти дополнительных схем, реализующих режим циклического суммирования, выгодно отличает предлагаемое изобретение от известного, так как повышает достоверность контроля постоянной памяти .

Формула изобретения

Устройство для контроля блока постоянной памяти, содержащее счетчик, регистр числа, первую схему сравнения, элементы И.и блок управления, причем выходы регистра числа подключены к одним из входов первой схемы сравнения, другие входы которой соединены со входами устройства, а выход подключен к первому входу блока управления, первый и второй выходы которо799019

Составитель В. Рудаков

Редактор Т . Кугрьваева Техред H.Ãðàá Корректор И . Муска

Заказ 0080 7 ираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул . Проектная, 4 го соединены с первым выходом устройства и входом счетчика, выход которого соединен со вторым выходом устройства, одни из входов элементов И подключены к третьему выходу блока уп-.. равления, другие входы соединены со входами устройства, а выходы — со входами регистра числа, о т л и ч а ющ е е с я тем, что, с целью повышения достоверности контроля, оно содержит сумматор, вторую схему сравнения и дополнительный регистр, причем входы второй схемы сравненйя подключены соответственно к выходам дополнительного регистра и выходам сумматора, один из входов которого соединен с четвертым выходом блока управления, другие входы сумматора соединены с выходами регистра числа, выход второй схемы сравнения подключен

Ко второму входу блока УПравления.

Источники информации, принятые во внимание при экспертизе

1 . Устройства постоянные запоминающие. Правила приемки и методы операционного котроля записанных кодов.

Отраслевой стандарт OCT 5.8427-76, М., 1977, ГР8028615, с. 12-16.

2 . Авторское свидетельство СССР

Ф 364967, кл . G 11 С 29/00, 1971 (прототип) .