Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

бвФ "CoIo3 Соаетскмд

Соцмалмстмческмх

Реснублмк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

И АЬТОИЗ©ММ (61) Дополнительное к авт. санд-ву(22) Заявлено 11.04.79 (21) 2751884/18-24 (5t)M. Кл.

G 11 С 29/00 с прнсоеднненнем заавкн ЙУ— (23) Прнорнтет—

Государственный комитет

СССР ио делан изобретений и открытий

Опублнкоеамо 23,01.81,Ьоллетемь Н9 3 (S3) УДК 681,327 (088. 82

Дата опублнкоеаннв опнсання 23 .01 .81 (72) Авторы изобретения

В .Л . Герасимова, Л .А . Колосков и 10..Л . Усов (71) Заявитель (542 УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к запсминающим устройствам.

Известно устройство для контроля памяти, которое содержит кодовый преобразователь, обрабатывакщий контроль- ный разряд и размещенный в системе передачи данных между процессором и запоминающим устройством P$

Недостатком этого устройства является то, что его затруднительно применять в двунаправленных системах передачи данных..

Наиболее близким по технической сущности к предлагаемому изобретению является устрОйство, содержащее ре" t$ гистр, мультиплексор данных, схему свертки и шинные формирователи f2) .

Недостатком этого устройства яв» ляется то, что при его использовании ЗО с двунаправленными шинамп значнтельНо увеличивается оборудование (возрастает количество регистров и схем сверток), что приводит к снижению достоверности передачи информации, 2 т .е. надежности устрой тва . Устройство также обладает ограниченным быстродействием, определяемым полным временем срабатывания многоразрядной свертки, которая должна сра- 30 батывать дважды прн передаче по одной магистрали адреса и данных.

Цель изобретения - повышение быстродействия н надежности устройства.

Поставленная цель достигается тем, что в устройство контроля памяти, содержащее регистр адреса, два мультиплексора, две группы формирователей сигналов, блок управления, первый триггер, первый блок свертки по модулю два и схему сравнения, п 1ичем выход регистра адреса соединен с первым входом первого мультиплексора, выход которого подключен ко входу первого блока свертки по модулю два н первым входам формирователей сигналов, вход регистра адреса соединен со вторым входом первого мультиплексора н с одним иэ выходов формирователей сигналов второй группы, другие выходы которых подключены к первому входу второго мультиплексора, второй вход. которого соединен с одним из выходов формирователей сигналов первой группы, другие выходы которых подключены к третьему входу первого мультиплексора, выход второго мультиплексора соединен со вторыми входами форьвтрователей сигналов, третьи входы ко" торых подключены к информационным к

799020 адресным входам устройства, первый и второй входы схемы сравнения соедг с выходом и первым входом одного из формирователей сигналов первой группы 4, второй вход которого подключен ко входу устройства. Выход схемы 11 сравнения соединен с первым входом первого триггера 7, выход которого подключен к индикаторному входу устройства.

Второй вход первого триггера 7 и управляющие входы регистра 1 адреса, мультиплексоров 2 и 3 и формироватенены соответственно с -выходом и первым входом одного иэ формирователей сигналов первой группы, второй вход которого подключен ко входу устройства, выход схемы сравнения соединен с первым входом первого триггера, выход которого подключен: к индикаторному выходу устройства, второй вход перволей сигналов первой 4 и второй 5 групп соединены с соответствующими выходами блока 6 управления.

Первый вход второго блока 10 свертки по модулю два подключен к выходам второго мультиплексора 3, второй вход — к первому входу второго триггера 8 и выходу первого блока 9 свертки по модулю два, а выход - к одному иэ входов полусумматора 12, друной вход которого соединен с выходом второго триггера 8, а выход — с втоблока свертки по модулю два, а выход-2О к одному из входов полусумматора, другой вход которого соединен с выходом второго триггера, а выход — с вторым входом схемы сравнения, второй рым входом схемы 11 сравнения. Второй вход второго триггера 8 подключен к соответствующему выходу блока 6 управления, являющегося микропрограммным.

Контролируемое з апоми нающее устройство и блок 14 микропроцессоров подключены двунаправленными шинами к адресным и информационным входам устройства.

Устройство работает следующим образом.

Предлагаемое устройство для контроля памяти позволяет выполнить контроль передачи информации запоминающего устройства в двух режимах: в режиме считывания инФормации из запоминающего устройства и в режиме записи информации в запоминающее устройство.

В режиме считывания и-разрядный адрес, сформированный в блоке 14 микропроцессоров через формирователи 5 второй группы, управляемые микропрограммным устройством 6 управления, запоминается на регистре 1 адреса . С выхода регистра 1 адреса через первый мультиплексор 2 и формирователи

4 сигналов первой группы адрес поступает в запоминающее устройство 13.

С выхода мультиплексора 2 и-разрядные адреса поступают также на первый блок 9 свертки по модулю два,и результат свертки запоминается на втором триггере 8 . По соответствующему адресу из контролируемого запоминающего устройства 13 через формирователи 4 сигналов первой группы, и разрядов информации поступает через мультиплексор 2 на первый блок 9 свертки по модулю два и m разрядов информации поступает через второй мультиплексор 3 на второй блок 10 свертки по модулю два, в последнюю ступень которого поступает результат с выхода первого блока 9 свертки по

J вход второго триггера r,oäêëâ÷åí к соответствующему выходу блока управления .

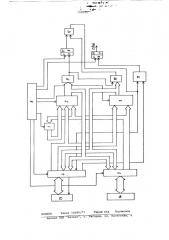

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит регистр 1 адреса, первый 2 и второй 3 мультинлексоры, первую 4 и вторую 5 группы формирователей сигналов, блок 6 управления, первый триггер 7 и второй триггер 8, являющийся 13-триггером,0 первый 9 и второй 10 блоки свертки по модулю два, схему 11 сравнения и полусумматор 12.

Выход регистра 1 адреса, содержащий и шин, соединен с первым входом первого мультиплексора 2, выход кото- 4Q рого, содержащий п шин, подключен ко входу первого блока 9 свертки по модулю два и первым входам формирователей сигналов групп 4 и 5.

Вход регистра 1 адреса соединен со вторым входом, содержащим и шин, первого мультиплексора 2 и с одним иэ выходов формирователей 5 сигналов

45 второй группы, другие выходы которых подключены к первому входу, содержащему m шин, второго мультиплексора 3, второй вход которого, содержащий m шин, соединен с одним из выходов формирователей сигналов первой группы 4, другие выходы которых подключены к третьему входу, содержащему и шин, первого мультиплексора 2. Выход второго мультиплексора 3 соединен со вторыми входами формирователей сигналов первой 4 и второй

5 групп, третьи входы которых, содер- щ жащие n + m разрядов, подключены к информационным и адресным входам устройства.

Первый и второй входы схемы 11 сравнения соединены соответственно го триггера и управляющие входы регистра адреса, мультиплексоров и формирователей сигналов соединены с соответствующими выходами блока управления, введены второй триггер, второй блок свертки по модулю два и полусумматор, причем первый вход второ- l5 го блока свертки по модулю два подключен к выходам второго мультиплексора, второй вход — к первому входу второго триггера и выходу первого

799020 модулю два . На выходе полусумматора

12 получается контрольный разряд как результат свертки информация, считанной из запоминающего устройства и поступающей с блока 10, и адреса, запомненного в триггер 8 в предыдущем такте. На выходе схемы 11 сравнения получается результат сравнения контрольного разряда, считанного с запоминающего устройства 13 через один из формирователей 4 сигналов первой группы v контрольного разряда с выхода полусумматора 12. Результат сравнения запоминается в триггере 7, управляемом микропрограммным устройством 6 управления, а на выходе триггера 7 (индикаторном выходе устройства)формируется сигнал "Сбой".

Во втором режиме (записи) и-разрядный адрес и информация, сформированные в блоке 14 микропроцессоров, поступают, как и в первом режиме, через формирователи 5 сигналов второй группы, регистр 1 адреса, первый мультиплексор 2 и формирователи 4 сигналов второй группы, в контролируемое запоминающее устройство 13.

С выхода мультиплексора 2 и разрядов адреса и и разрядов информации поступает на вход блока 9 и результат свертки адреса запоминается на триггере 8, a m разрядов информации, сформированной в блоке 14 микропроцессоров, поступает через формирователи 5 сигналов второй группы и второй мультиплексор 3 на второй блок

10 свертки по модулю два,в последнюю ступень которого подается результат свертки с выхода блока 9.

На выходе полусумматора 12 формируется контрольный разряд как результат свертки по модулю два информации, поступившей из блока 14 микропроцессоров, и адреса, запомненного в триггере 8 в предыдущем такте. Этот контрольный разряд с выхода полусумматора 12 вместе с п разрядами информации, поступающими с выхода первого мультиплексора 2, и в разрядами информации, поступающими с выхода второго мультиплексора 3, подаются через формирователи 4 первой группы на запись в контролируемое запоминающее устройство 13.

Технико-экономические преимущества предлагаемого устройства заключаются в повышении его быстродействия и надежности при обеспечении воэможности работы с двунаправленными шинами .

Формула изобретения

Устройство для контроля памяти, содержащее регистр адреса, два мультиплексора, две группы Формирователей сигналов, блок управления, первый триггер, первый блок свертки по модулю два и схему сравнения, причем вьйод регистра адреса соединен с пер5 вым входом первого мультиплексора, выход которого подключен ко входу первого блока свертки по модулю два и первым входам формирователей сигналов, вход регистра адреса соединен со вторым входом первого мультиплексора и с одним из выходов формирователей сигналов второй группы, другие выходы которых подключены к первому входу второго мультиплексора, второй вход которого соединен с одним из выходов формирователей сигналов первой группы, другие выходы которых подключены к третьему входу первого мультиплексора, выход второго мультиплексора соединен со вторыми входами

20 формирователей сигналов, третьи входы которых подключены к информационным и адресным входам устройства, первый и второй входы схемы сравнения соединены соответственно с выхо2 дом и первым входсм одного из формирователей сигналов первой группы, второй вход которого подключен ко входу устройства, выход схемы сравнения соединен с первым входом первого триггера, выход которого подключен к индикаторному выходу устройства, второй вход первого триггера, и управляющие входы регистра адреса, мультиплексоров и Формирователей сигналов соединены с соответствующими выходами блока управления, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности устройства, оно содержит второй триггер, второй блок свертки

40 по модулю два и полусумматор, причем первый вход второго блока свертки по модулю два подключен к выходам второго мультиплексора, второй вход— к первому входу второго триггера и

4 выходу первого блока свертки по модулю два, а выход — к одному из входов полусумматора, другой вх д кото.рого соединен с выходом второго триггера, а выход — с вторым входом схеО мы сравнения, второй вход второго триггера подключен к соответствующему выходу блока управления.

Источники информации, 5 принятые во внимание при экспертизе

1 . Заявка Японии Р 52-647, кл . 97 (7) С 01, опублик . 10 .01 .77 .

2. Заявка Японии Р 52-26663, кл . 97 (7) Q 11,опублик . 15 .07.77 (прот тип) .