Устройство для контроля логических схем

Иллюстрации

Показать всеРеферат

Союз Саевтскид

Сецналнстнчвскнк

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ С ТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.07.78 (21) 2б42103/18-21 ®М с присоединением заявки М (23) Приоритет

Н 03 К 5/01

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 373 (088.8) Опубликовано 230181. Бюллетень Й9 3

Дата Опубликования описания 2 3. 01. 81 (72) Авторы изобретения

Т.М. Алиев и И.П. Сколецкий

ВАТЬ ф- У 1 +) 4. ОТОЙ зер а джанский институт нефти и хи и

5ssQ (зйсдЬь9 3 Рте (71) Заявитель им. М. Азизбекова (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ

Изобретение относится к импульсной технике и может найти применение при разработке, наладке и ремонте цифровых измерительных приборов и ЭВМ.

Известно устройство для контроля логических схем, содержащее элементы индикации, включенные в цепь логических элементов 2 И-НЕ индикации, и управляющие инверторы (1J

Недостаток известного устройства заключается в низкой достоверности отсчета.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для контроля логических схем, содержащее два элемента индикации, включенные в цепь логических элементов, управляющие инверторы, ключевые элементы, резисторы и диод 2 .

Устройство выполнено на полупроводниковых интегральных вентилях и способно однозначно отображать 4 состояния контролируемой точки, а именно: обрыв контролируемой цепи, логический ноль, логическая единица и низкочастотную генерацию.

Недостатком известного устройства .является невозможность индицировать высокочастотную генерацию, а также одиночные импульсы и пачки импульсов в контролируемой точке.

Целью изобретения является расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство для контроля логических схем, содержащее два элемента индикации, включенные в цепь двух логических элементов, вход одного иэ которых через третий логический элемент соединен с выходом одного ключевого элемента и с одним из входов второго логического элемента, второй вход которого соединен с выходом второго ключевого элемента и входом етвертого логического элемента, диод и резисторы, введены два триггера, пятый логический элемент,.инвертор, два элемента индикации и дифференцирующая цепь, причем выход четвертого логического элемента соединен со втврым входом третьего логического элемента, одним из входов пятого логического элемента и через дифференцирующую цепь со входом инвертора, выход которого подключен ко второму входу четвертого логического элемента и тактовым

799118

Устройство работает следующим образом.

При подключении питания и отсутствии сигнала на входной шине 20 (обрыв) ключевой элемент 9 открыт током, проходящим через резистор 10, а ключевой элемент 8 закрыт, так как прямо падение напряжения на диоде 12 понижает потенциал его входа ниже порога открывания. Элемент

2И-HE 4 закрыт низким потенциалом .40 с выхода ключевого элемента 9, а элемент 2И-HE 3 закрыт низким потенциалом с выхода элемента И-НЕ 5. Ввиду этого элементы индикации 1 и 2 не светятся. 65 входам триггеров, при этом единичный выход первого триггера соединен с информационным входом второго триггера, нулевой выход которого соединен с третьим элементом индикации и выходом пятого логического элемента, другой вход которого подключен к первому входу третьего логического элемента, выход которого соединен со входами сброса триггеров,а нулевой выход первого из которых подключен к четвертому элементу индикации.

В качестве элементов индикации применены включенные через токоог- .. . раничивающие резисторы сегменты циро-синтезирующей светодиодной матрицы, r.ðè÷åì второй элемент индикации содержит два правых сегмента, первый — остальные крайние сегменты, третий — десятичный сегмент, а четвертый — внутренний сегмент матрицы.

Такое выполнение позволяет помимо индикации в удобной цифровой форме логических уровней контролируемой точки индицировать также одиночные импульсы обеих полярностей, пачки импульсов обеих полярностей и непрерывную высокочастотную генерацию.

Восстановление устройства (сброс триггеров) осуществляется.автоматически при отсоединении входной шины устройства от контролируемой точки, -..е. без использования каких-либо контактных устройств, снижающих надежность.

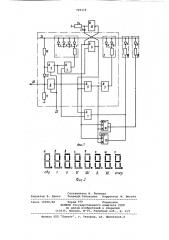

На фиг. 1 изображена структурная электрическая схема устройства;на фиг. 2 — вид индикации при различных состояниях контролируемой точки. устройство для контроля логических схем содержит первый и второй элементы 1 и 2 индикации, логические элементы И-НЕ 3-7, ключевые элементы

8 и 9, резисторы 10 и 11, диод 12, дифференцирующую цепь, состоящую из конденсатора 13 и резистора 14, инвертор 15, триггеры 16 и 17, третий и четвертый элементы 18 и 19 индикации, входную шину 20, шину 21 питания, шину 22 напряжения смещения.

Элементы И-НЕ 5 и 7 открыты высокими потенциалами, поступающими с выходов элемента И-НЕ б И ключе-..oão элемента 8. Вследствие этого триггеры 16 и 17 сброшены в "ноль", и через элемент 2И-НЕ 7 светится элемент 18 индикации, в то время как элемент

19 индикации не светится.

При подключении входной шины 20 к контролируемой точке с высоким потенциалом ключевой элемент 9 от1крывается током, проходящим через резистор 10, так как диод 12 заперт высоким потенциалом контролируемой точки. Ключевой элемент 8 также открывается, и низкий потенциал с его выхода, проходя через элемент И-НЕ 5, открывает элемент И-НЕ

3, а элемент И-НЕ 4 закрыт.

Это приводит к закрыванию элемента И-НЕ 7, ввиду чего прекращается свечение элемента 18 индикации, включается элемент 2 индикации, а триггеры 16 и 17 подготавливаются к работе высоким потенциалом с выхода элемента 5. Цифровой индикатор высвечивает единицу двумя правыми сегментами (см.фиr.2б)

При подключении входной шины 20 к контрольной точке с низким потенциалом ключевые элементы 9 и 8 закры ты. Элемент И-HE б открывается (выход инвертора 15 имеет высокий потенциал) и закрывает по вторым входам элементы И-НЕ 5 и И-НЕ 7. Это приводит к тому, что наряду с элементом 2 индикации светится элемент

1 индикации при остальных погашенных элементах индикации и подготовленных к работе триггерах 16 и 17. Цифровой индикатор высвечивает "Нуль" всеми своими крайними сегментами (фиг.2в).

Если входная шина 20 устройства контактирует с точкой, имеющей высокий уровень, и в которой возникает одиночный импульс отрицательной полярности, то этот импульс, сформированный и расширенный одновибратором, состоящим из элементов

6 и 15, поступает на тактовые входы триггеров 16 и 17. Триггер 16 установится в единичное, а триггер

17 останется в нулевом состоянии.

Это приведет к включению элемента

19 индикации, и цифровой индикатор свечением сегментов (фиг.2г) будет сигнализировать о прохождении одиночного отрицательного импульса.

Если в контрольнои точке возникает больше одного импульса, то с выхода элемента 15 поступят дополнительные импульсы, переключающие в единичное состояние также и триггер 17. Теперь дополнительно светится и элемент 18 индикации, так как нулевой выход триггера 17 и выход элемента И-НЕ 5 объединены по схе799118 ме в "проводное ИЛИ". Цифровой индикатор свечением сегментов (фиг.2д) сигнализирует о прохождении в контрольной точке более одного отрицательного импульса.

При наличии в контрольной точке положительных импульсов включаются сегменты (фиг.2е,ж) индицируя исходное нулевое состояние контрольной точки.

В случае непрерывной генерации в контрольной точке триггеры 16 и 17 включаются при прохождении пачек импульсов. Однако ввиду того, что

) уровень сигнала на входе непрерывно меняется, сегменты индикатора либо мигают, либо светятся вполсилы, в то время как правые сегменты светятся в - чолную силу (фиг.2з).

Таким образом, изобретение однозначно индицирует в цифровой форме восемь различных состояний, в том чис- 26 ле 3 статических и 5 динамических.

Этого в большинстве случаев достаточно для проведения наладки или ремонта цифровых схем.

Устройство построено полностью р на полупроводниковых интегральных вентилях серии 133 и 155 и потребляет ток не более 100 мА.

Формула изобретения

Устройство для контроля логических схем, содержащее два элемента индикации, включенные в цепь двух логических элементов, вход одного из которых через третий логический элемент соединен с выходом одного ключевого элемента и с одним из входов второго логического элемента, второй вход которого соединен с выходом второго ключевого элемента и входом четвертого логического элемента, диод и резисторы, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей, в него введены два триггера, пятый логический элемент, инвертор, два элемента индикации и дифференцирующая цепь, причем выход четвертого логического элемента соединен со вторым входом третьего логического элемента, одним из входов пятого логического элемента и через . дифференцирующую цепь со входом инвертора, выход которого подключен ко второму входу четвертого логического элемента и тактовым входом триггеров, при этом единичный выход первого триггера соединен с информационным входом второго триггера нулевой выход которого соединен с третьим элементом индикации и выходом пятого логического элемента,другой вход которого подключен к первому входу третьего логического элемента, выход которого соединен со входами сброса триггеров, а нулевой выход первого из которых подключен к четвертому элементу индикации.

Источники информации принятые во внимание при экспертизе

1. "Электроника", 1973, Р 4, с. 74.

2. Авторское свидетельство СССР по заявке Р 2027092/18-21,17.08 ° 77.

799118!!!! !!

1111 Г1 ивИ авив@ à тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 10090/82

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Составитель М. Леонова

Редактор В. Данко ТехредМ.Табакович Корректор М. Вигула