Параллельно-последовательский пре-образователь напряжения b код

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски и

Социапистическик ресцу6пик (i ij799131 ъ (6l ) Дополнительное к авт. санд-ву— (22) Заявлено О 1.08.77 (21) 2458969/18-21 с присоединением заявки № 245896 8/1 8-2 1 (23) ПриоритетОпубликовано 23.01.81. Бюллетень № 3

Дата опубликования описания 26,01,81 (51)М. Кл.

Н 03 К 13/>75 Рзоударотовниый комитет

СССР ио долом изобретений и открытий (53) УДК 681.325 (088.8) . (72) Автор изобретения

B. И Рязанов,Г; —, 1

Рязанский радиотехнический институт (7l ) Заявитель (54) ПАРАЛЛЕЛЬНО-IIOCJIEQ0BATEIlb HbIA

ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД

Изобретение относится к информационно-измерительной технике и может быть использовано .в цифровых осцилографах, автоматизированных системах сбора ин формации, вводных устройствах БВМ и т.д. 5

Известны преобразователи напряжения в код, реализующие способ параллельнопоследовательного преобразования, нэ которых наибольшего быстродействия достигает преобразователь разомкнутого типа (l) .

Но в таком преобразователе минимальное время преобразования ограничено длительностью переходных процессов в блоке формирования разностного сигнала, неизбежно возникающих в моменты вы- ° читания эталонных напряжений из напряжения преобразуемого сигнала.

Наиболее близким к данному техничес-20 кому решению является параллельно-доследовательный преобразователь напряжения в код, содержащий канал преобразо-. вания старших разрядов, состоящий иэ . последовательно соединенных источника эталонных напряжений, блока компараторов и шифратора, и канал преобразования младших разрядов, состоящий из формирователя разностного напряжения, источника эталонных напряжений, блока компараторов и шифратора f2) .

Такой преобразователь также не обеспе» чивает необходимого быстродействия из-за влияния переходных процессов на скорость преобразования.

Бель изобретения — повышение быстродействия преобразования.

Поставленная цель достигается тем, что в параллельно-последовательный преобразователь напряжения в код, содержащий канал преобразования старших разрядов, состоящий из последовательно соединенных источника эталонных напряжений, блока компараторов и шифратора, и канал преобразования младших разрядов, состоящий из формирователя разностного напряжения, источника эталонных напряжений, блока компараторов и шифратора, введены вспо3 7991 могательный источник опорных напряжений с блоком компараторов, дополнительные каналы преобразования младших разрядов и: цифровой коммутатор каналов, причем входная клемма преобразователя соединена с сигнальными входами блока компараторов канала преобразования старших разрядов, вспомогательного блока. компараторов и аналоговы— ми входами всех каналов преобразования младших разрядов, кодовые входы которых подключены к выхоцам вспомогательного блока компараторов, а выходы — к управляемым входам коммутатора, управ, ляющие входы которого соединены с выхо- 1> цамн канала преобразования старших разрядов.

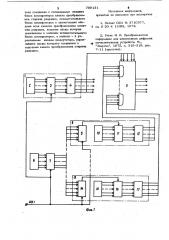

На фиг. l показана функциональная блоксхема параллельно-последовательного преобразователя напряжении в код, на фиг. 2 проиллюстрирован процесс кодировання линейно-нарастающего напряжения при иенольэованин двух каналов преобразования младших разрядов.

Устройство содержит канал 1 преобразования старших разрядов, состоящий нз последовательно соединенных источника 2 эталонных напряжений,.блока Э компаратора и шифратора 4, шина старших раэряцов которого подключена к цифровому коммутатору 5каналов,,вспомогательный источник 6 опорных напряжений, подключенный к блоку 7 компараторов, выходы которого соединены с каналом 8 преобразования младших разрядов, ЗЗ состоящим иэ формирователя 9 разностного сигнала и последовательно соединенных источника 10 эталонных напряжений, блока 1 1 компараторов и шифратора 12, причем выход формирователя 8 соединен со вторым входом блока 11 компараторов, 4й

Выходы блока 7 компараторов подключены также к вспомогательному каналу 13 преобразования млацших разрядов, содержащих аналоговые блоки: формирователь 14

4$ разностного сигнала, источник 15 эталонных напряжений, блок 16 компараторов и шифратор 17, соединенных так же, как в канале 8.

Блоки 3 и 7 компараторов и формиро- йй ватели 8 и 14 подключены к входной клемме преобразователя. Выходы шифраторов 12 и 17 подключены ко входам коммутатора 5каналов,,выход которого является выхоцом устройства. М

Устройство работает следующим образом. Преобразуемое напряжение 0() поступает на блок 3 компараторов канала

31 4

l, гце сравнивается с набором эталонных напряжений Оэ старшей группы .- (фиг. 2 а). По состоянию компараторов в шифраторе 4 формируется коц старших разрядов. Одновременно напряжение 0 (t) поступает на блок 7 компараторов, где сравнивается с опорными напряжениями О (фнр. 2 а). По состоянию компараторов формируются разностные напряжения

U(f)-0>> $ цля каждого канала преобразования младших разрядов. Р эностные напряжения (фиг. 2 б, в) через формирователи 9 и 14 поступают на блоки 11 и

16 компараторов, где сравниваются с эталонными напряжениями О сформированными источниками 10 и 15 эталонных напряжений. По состоянию компараторов шифраторами 12 и 17 в каждом канале формируется коц младших разрядов. . Но достоверным этот код будет лишь в канале, где разностное напряжение в этот момент не выходит иэ зоны эталонных напряжений (толстые линии на фиг. 2 б). Поэтому коц младших разрядов на выход устройства поступает нэ различных каналов. Подкщочение канала цля съема кода осуществляется компаратором 5 в соответствии с кодами, поступающими с шифратора 4.

Введение нескольких каналов преобразования младших разрядов и организацня поочередной работы каналов позволяют исключить влияние дпительности переходных процессов на скорость преобразования и тем самым повысить быстродействие устройства.

Формула изобретения

Параллельно-последовательный преобразователь напряжения в код, содержащий канал преобразования старших разрядов, состоящий нз последовательно соецнненных источника эталонных напряженнй, блока компаратора и шифратора, и канал преобразования младших разрядов, состоящий иэ формирователя раэноетного напряжения, источника эталонных напряжений, блока компараторов и шифратора, о т л и ч а ю щ н и с я тем, что, с целью повышения быстродействия преобразования в него введены вспомогательный источник опорных напряжений с блоком компараторов, дополнительные каналы преобразования младших разрядов и цифровой коммутатор, . каналов, входная клемма преобраэова799131 теля соединена с сигнальными входами. блока компараторов канала преобразования старших разрядов, вспомогательного блока компараторов и аналоговыми входами всех каналов преобразования млад ших разрядов, кодовые входы которых . подключены к выходам вспомогатепьногоЬ. блока компараторов, а выходы — к управляемым входам коммутатора, управляющие входы которого соединены с выходами канала преобразования старших разрядов.

Источники информации принятые во внимание при экспертизе

1. Патент США М 3710377, 5 кл. Н 03 К 13 02, 1973.

2. Гитис Э. И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия, 1975, с. 316-319, рис.

7-11 (рототип).

799 l3 1

s) "

Составитель И. Горелова

Редактор Т. Киселева Техред А.Бабинец Корректор Ю. Макаренко

Заказ 10091/83 Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фвинал ППП "Патент, г. Ужгород, ул. Проектная, 4