Многоканальный декодер

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

<о799156 (61) Дополнительное к авт. свид-ву— (22) Заявлено 250179 (21) 2717128/18-09 с присоединением заявки М(23) Приоритет—

Опубликовано 230181. ЬюллетеHb "(9 3

Дата опубликования описания 23.01.81 (51)М. Кл з

H 04 L 5/22

Н 04 . 3/ОГ)

Н 03 К 13/34

Государственный комитет

СССР ио деяам изобретений и открытий (53) УДК 62) . 394. .14(088.8) (72) Авторы изобретения

М.С. Бобров и A.È. Борунов (7 I ) 3 а яв итель (54 ) MHOPOKAHAJIbHbN ДЕ (ОДЕР

Изобретение относится к технике передачи информации и может использоваться в устройствах защиты от ошибок систем передачи и обработки дискретной информации.

Известен многоканальный декодер, содержащий последовательно соединенные генератор тактовых импульсов, счетчик цикла декодирования и распределитель каналов, а также входной коммутатор, выход которого подключен к информационному входу декодирующего блока, ко входу которого подключен выход генератора .тактовых импульсов (11 .

Однако известный декодер имеет низкую достоверность приема информацик.

Цель изобретения — повышение дос товерности приема информации.

Поставленная цель достигается тем, что в многоканальный декодер, содержащий последовательно соединенные генератор тактовых импульсов, счетчик цикла декодирования и распредели.:ль каналов, а также входной коммутатор, выход которого подключен к информационному входу декодирующего блока, ко входу которого подключен выход генератора тактовых импульсов, введены последовательно соединенные дешифратор импульса записи, коммутатор адресов записи и сумматор, а также, в каждый из каналов, оперативное запоминающее устройство (ОЗУ), выходы каждого из которых подключены ко входам входного коммутатора, при этом к управляющим входам ОЗУ подключен выход сумматора, а ко входам записи ОЗУ подключен выход дешифратора импульса записи, к первому входу которого и управляющему входу входного коммутатора подключен выход распределителя каналов, вход которого подключен к второму входу дешифратора импульса записи и второму входу сумматора.

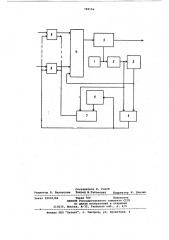

На чертеже представлена электрическая структурная схема многоканального декодера.

Он содержит генератор 1 тактовых импульсов, счетчик 2 цикла декодирования, распределитель 3 каналов, 25 входной коммутатор 4, декодирующий блок 5, дешифратор 6 импульса записи, сумматор 7, оперативные запоминающие устройства 8 и коммутатор 9 адресов записи.

Декодер работает следующим об30 „,ом

799156

Информация, поступающая с каналов, постепенно заполняет канальные

ОЗУ 8 под воздействием импульса записи, поступающего с дешифратора 6.

Период импульсов записи равен длине элементарной посылки информации в канале Тп. Между импульсами записи декодирующий блок 5 проводит обработку информации, накопленной в канальных ОЗУ 8. Число каналов, которое может обработать декодирующий блок 5 за вермя между двумя импуль" сами записи, составляет т„г

n -1 где Р— емкость канального ОЗУ, тактовая частота при декодировании.

Дешифратор 6 настроен так, что импульс записи формируется в момент поступления со счетчика 2 нулевого адреса. Таким образом, запись производится в ячейку канальных ОЗУ 8, имеющую адрес, определяемый коммутатором 9 адресов записи. По заднему

Фронту импульса записи производится переключение коммутатора 9. При де- кодировании адреса ячеек канальных

ОЗУ 8 определяются как сумма адресов коммутатора 9 и счетчика 2. В течение цикла декодирования адрес коммутатора 9 не меняется, он определяет ячейку ОЗУ, с которой начинается считывание, что необходимо для считывания информации в порядке, соответствующем ее поступлению. С выхода канальных ОЗУ 8 информация поступает на входной коммутатор 4, выход которого подключен к декодирующему блоку 5. Номер канала (номер ОЗУ), подключаемого к декодирующему блоку 5, определяет распределитель 3. Так как вся информация, приходящая из канала, должна обрабатываться декодирующим блоком 5 беэ пропусков, периодичность обращения докодирующего блока 5 к одному и тому же каналу составляет (P — L+1) тп, где L — длина зачетного отрезка при декодировании.

Время декодирования информации из

P одного канала составляет—

Рт

Число каналов М, по которым декодер может обеспечить непрерывный прием информации определяется формулой

N c(1 ) т„FT

5 и имеет порядок десятков или сотен в зависимости от соотношения быстродействия элементной базы и скорости работы по каналам.

В предлагаемом декодере обеспечи)О вается прием информации с большего числа каналоВ, прием информации с каждого канала ведется непрерывно, что расширяет область его применения и повышает вероятность приема приходящих сообщений.

Формула изобретения що Многоканальный декодер, содержащий последовательно соединенные генератор тактовых импульсв, счетчик цикла декодирования и распределитель каналов, а также входной коммутатор, выход которого подключен к информационному входу декодирующего блока, ко входу которого подключен выход генератора тактовых импульсов, о тл и ч а ю шийся тем,, что, с целью повышения достоверности приема

30 информации, введены последовательно соединенные. дешифратор импульса записи, коммутатор адресов записи и сумматор, а также, в каждый из канал@в, оперативное запоминающее уст35 ройство (ОЗУ), выходы каждого иэ которых подключены ко входам входного коммутатора, при этом к управляющим входам ОЗУ подключен выход сумматора, а ко входам записи ОЗУ подключен выход дешифратора импульса записи, к первому входу которого и управляющему входу входного коммутатора подключен выход распределителя каналов, вход которого подключен к второму: входу дешифратора импульса записи и второму входу сумматора.

Источники информации, принятые во внимание при экспертизе

1. Техническое описание к annagg ратуре "П-161". Раэработки КНИИТМУ, Калуга (прототип).

79915 6

Составитель Е. Голуб

Редактор Л. Белоусова Техред М.Табакович корректор M. Демчик

Заказ 10093/84 Тираж:709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4