Цифровой синусно-косинусный преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЬРЕтЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (и)800923 (61) Дополнительное к авт. санд-ву— (22) Заявлено 290578 (2f) 2621934/18-09 (51)м. f(g.З с присоединением заявки Нов (23) Приоритет

G 01 S 7/1ã (G оь F Л/00

Государственный комитет

СССР по дедам изобретений и открытий

Опубликовано 30.0 1,81 бюллетень 89 4

Дата опубликования описания 300 1.81 (53) УДК 821. 398.9ь. ..681 (088. 8) (72) Автор изобретения Е. Ф. Киселев

I

f (71) Заявитель (5 4 ) ЦИФРОВОЙ СИНУСНО-КОС ИНУСНЫИ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к радиотехнике и может использоваться в качестве датчика кодов синусно-косинусных зависимостей и масштабных мет6к угла поворота антенны.

Известен цифровой синусно-косинусный преобразователь, содержащий датчик прямого и инверсного п-разрядного кода, сумматор, входы которого соединены с выходами двух старших разрядов датчика прямого и инверсного и-разрядного кода, прямые и инверсные выходы остальных разрядов которого соединены с входами коммутатора, источник синхроимпульсов, выходами соединенный с входами блока управления, через который один из старших разрядов датчика прямого и .инверсного п-разрядного кода соединен с управляющим входом коммутато ра и корректирующим входом множит ельно ro блок а, ст аршие р азр яды коммутатора соединены с входами блока памяти, первая группа выходов младших разрядов коммутатора соединена с первыми входами элемента ИЛИ и компаратора, а вторая группа выходов младших разрядов коммутатора соединена с вторыми входами элемен-, .та ИЛИ и компаратора и первой группой входов множительного блока, первая группа выходов блока памяти соединена с первыми входами блока on ределения меток, второй и третий входы которого соединены соответственно с выходами элемента ИЛИ и компаратора, вторая группа выходов блока памяти соединена с первой групО пой входов выходного сумматора, третья группа выходов блока памяти соединена с третьим входом компаратора И) .

Однако известный преобразователь .имеет недостаточную точность.

Цель изобретения — повышение точности

Цель достигается тем, что в преобразователь введены два вычислительных блока и дополнительный сум20 матор, при этом выходы дополнительного сумматора соединены с второй группой входов выходного сумматора, первая и вторая группа входов дополнительного сумматора соединены соответственно с выходами первого вычислительного блока и с выходами множительного блока, вторая группа входов которого соединена с выходами второго .вычислительного блока, а

30 первая группа выходов младших раз800923 рядов коммутатора соединена с управляющими входами вычислитеЛьных блоков, к информационным входам которых подключены соответствующие группы выходов блока памяти.

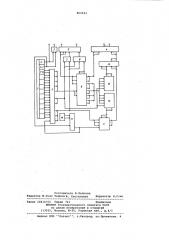

На чертеже приведена структурная электрическая схема предложенного преобраэо.ват еля.

Цифровой синусно-косинусный преобразователь содержит датчик 1 прямого и инверсного и-разрядного кода, коммут атор 2, сумматор 3, выходной сумматор 4, множительный блок 5, блок 6 определения меток, элемент

ИЛИ 7, компаратор В, блок 9 памяти, источник 10 синхроимпульсов, - блок

11 управления, дополнительный сумма- 1Я тор 12 и. вычислительные блоки 13 и

l4.

Преобразователь работает следующим образом. и-ый разряд датчика 1 является -@ з иаковым разрядом кода ы и х, а з наковый разряд кода cos х определяется сумматором 3 как сумма по модулю логических значений и-1 и n-ro разрядов датчика l.

Определение кодов чисел i sin х1 и icos xi осуществляется методом кусочно-.линейной аппроксимации с использованием тригонометрических формул приведения. Аппроксимация функций производится по синусной функции 30 в пределах.от 0 до Ъ /2. Коды Is)ï х! и Icos х определяются последовательно в каждом цикле преобразования, состоящем из двух периодов Т, и Т .

В течение Т„ определяется код 35

)sin х, а в течение Т - код Icos х) .

Для этого блок 11 вырабатывает по значению и-1-го разряда управляющий логический сигнал Q(T) таким образом, что Q(T„) =Q, à Q (Т ) =Я„, @» где Q„ — логическйй коэффиЦиент и-l-го разряда датчика 1.

Коммутатор 2 по сигналу Q(T) и прямому и инверсному п-2 разрядному коду младших разрядов датчика 1 вырабатывает код приведенного угла Xnð (Т) 5

Для осуществления дальнейшей работы и-2 разрядный код угла Х (Т) разделен на три кода, соответствующих углам Х„,+ и Х соответственно,так, что Х„(Т)=Х,+Х +Х, где Х„+Х и Ы

X> - углы, величины которых опреде,ляются соответственно значениями старших разрядов и значениями первой

"и" второй групп младших разрядов коммутатора 2. Код угла Х1 поступает 55 на входы блока 9, который по коду угла Х„комбинационно: вырабатывает коды углов, соответствующих угловым меткам, код значений синусной функции, коды угловых коэффициентов участков аппроксимации и коды поправок соответственно.

Коды угловых коэффициентов участ яов аппроксимации и коды поправок с соответствующих выходов блока 9 поступают на параллельно соединенные информационные входы вычислительных блоков 13 и 14, на параллельно соединенные управляющие входы которых поступает с первой группы выходов младших разрядов коммутатора 2 код угла Х .

По входным кодам первый вычислительный блок 13 комбинационно вы- . рабатывает код приращения синусной функции, соответствующего приращению аргумента на обрабатываемом участке, а второй вычислительный блок 14 - код углового коэффициента соответствующего подучастка обрабатываемого участка аппроксимации.

С выходов второго вычислительного блока 14 код углового коэффициента поступает на вторую группу входов множительного блока 5, на первую группу входов которого с второй группы выходов младших разрядов коммутатора 2 поступает код угла Х . На корректирующий вход множительного блока 5 с выхода блока 11 поступает логический сигнал Q(T) .

По этим сигналам множительный блок 5 вырабатывает код приращения синусной функции, соответствующего приращению аргумента.

С выходов первого вычислительного блока 13 код приращения угла Xg и с выходов множительного блока 5 код приращения угла Х> поступают соответственно на первую и вторую группу входов дополнительного сумматора 12.

Дополнительный сумматор 12 вырабатывает код приращения синусной функции соответствующего приращения аргумента на обрабатываемом участке аппроксимации на угол (Х +Хз) .

Этот код приращения с выходов дополнительного сумматора поступает на вторую группу входов выходного сумматора 4, на первую группу входов которого поступает код с второй групры выходов блока 9.

По кодам, поступающим с третьей группы блока 9 и с первой и второй групп младших разрядов коммутатора компаратор В вырабатывает сооТ ветствующие логические сигналы, поступающие на третий вход блока 6, на первые входы и второй вход которого поступают соответствующие сигналы с первой группы выходов блока 9 и с выхода элемента ИЛИ 7 соответственно. По этим входным сигналам. блок

6 вырабатывает код масштабных угловых меток вЂ,сигналы признаков масштабных угловых меток 5 и ЗОО.

Перед началом цикла преобразования блок 11 по сигналу логического зиачения Яя п-1-ro разряда датчика

1 вырабатывает управляющий сигнал

Q(T) =Q(T,) =Q«. при котором на выходах выходного сумматора 4 вырабатыва.ется код i sin х f, а на выходах бло800923 ка б — код масштабных угловых меток соответ ствующий углу Х „(T ) .

Цикл вычисления (преобразования) начинается с приводом от источника

10 на блок 11 старт-импульса.

По старт-импульсу блок ll из последовательности тактовых импульсов источника 10 выделяет два.первых импульса, следующих непосредственно после окончания старт-импульса.

По nepsoMy Hs этих aayx HMayabcos 1О блок 11 генерирует импульс, по которому производится съем с преобразователя кода sin х, а после его окончания начинается период, в течение которого блок 11 на управлчющем выходе вырабатывает управляющий логический сигнал Q(T) =Я(Tq ) =

=Я

При этом период частоты следования тактовых импульсов источника 10 вырабатывается таким, что за время, 20 заключенное между окончанием тактового импульса и началом следующего тактового импульса, все переходные процессы заканчиваются, т.е. на выходах выходного сумматора 4 устанав- р ливается код числа cos х), а на выходах блока б — код масштабных угловых меток, соответствующий углу

Х„р (Т, ).

После этого блок 11 генерирует импульс, по которому производится съем с преобразователя кода cos х, а по его окончании на выходе блока

ll устанавливается управляющий сигнал Я(Т) =Я(Т ) =Q« °

На этом цикл вычислений заканчивается, а очередной цикл начнется только с приходом от источника .10 на блок 11 очередного старт-импульса.

Предложенный преобразователь обес- 4О печивает высокую точность воспроизведения функции.

Формула изобретения

Цифровой синусно-косинусный преобразователь, содержащий датчик прямого и инверсного и-разрядного кода, сумматор, входы KQToporo соединены 50 с выходами двух старших разрядов датчика прямого и инверсного и-раэрядного кода, прямые и инверсные выходы .остальных разрядов которого соединены с входами коммутатора, источник синхроимпульсов, выходами соединенный .с входами блока управления, через который один из старших разрядов датчика прямого и инверсного п-разрядного кода соединен с управляющим входом коммутатора и кор(ректирующим входом множительного блока, старшие разряды коммутатора соединены с входами блока памяти, первая группа выходов младших разрядов коммутатора соединена с первыми . входами элемента ИЛИ и компаратора, а вторая группа выходов младших разрядов коммутатора соединена с вторыми входами элемента ИЛИ и компаратора и первой группой входов мно1кительного блока, первая группа выходов блока памяти соединена с первы« ми входами блока определения, меток, второй.и третий входы которого соединены соответственно с выходами элемента ИЛИ и компаратора, вторая группа выходов блока памяти соединена с первой группой входов выходного сумматора, третья группа выходов блока памяти соединена с третьим входом компаратора, о т л и ч а юшийся тем, что, с целью повышения точности, введены два вычислительных блока и дополнительный сумматор, при этом выходы дополнительного сумматора соединены с второй

rpynnoA входов выходного сумматора, первая и вторая группы входов дополнительного сумматора соединены соответственно с выходами первого вычислительного блока и .с выходами множительного блока, вторая группа входов которого соединена с выходами второго вычислительного блока, а первая группа выходов ютадших разрядов коммутатора соединена с управляющими входами вычислительных блоков, к информационным входам которых подключены соответствующие группы выходов блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидет ельство СССР по заявке 9 2587867,кл.G 06 Г 15/00, 03.03. 78 (прототип) .

800923

Составитель Е. Петрова

Редактор М.Ткач Техред Ж. Кастелевич Корректор Н,Стец

Заказ 10414/62 Тираж 743 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул.Проектная, 4