Устройство обработки последовательныхчастотно-разнесенных сигналов

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (63) Дополнительное к авт. сеид-ву (22) Заявлено 210329 (21) 2740167/18-09 (53)М. Кл. с присоединением заявки ¹

Государственный конитет

СССР по делан изобретений и открытий

G 0l S 7/30 (23) Приоритет

Опубликовано 3001.81. Бюллетень N9 4

Дата опубликования описания 30.0 1.81 (53) УДК 621. 369, .96 (088.8) E.M.Âåäåíååâ, A.A.Æåíæåðà, В.С.Иванцовский, Г.М.ЛуКейсв,:;

A. И.Морозова, И.Р.Сиваков и В.П.Коробенко (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ОБРАБОТКИ ПОСЛЕДОВАТЕЛЬНЫХ

ЧАСТОТНО-РАЗНЕСЕННЫХ СИГНАЛОВ

Изобретение относится к радиотех нике и может использоваться в приемниках последовательных. частотно-разнесенных сигналов. известно устройство обработки последовательных частотно-разнесенных

Г сигналов, содержащее два параллельных канала, каждый из которых состоит из последовательно соединенных первого электронного ключа и интегратора, сумматора, второго и третьего электронных ключей и блока памяти, входы первых электронных ключей обьединены и являются входом устройства обработки (1). т5

Однако в работе данного устройства возрастают ошибки из-за паразитного статического напряжения, Цель изобретения — уменьшение выходного статического напряжения

20 ошибки.

Указанная цель достигается тем, что в устройство обработки последовательных частотно-разнесенных сиг.— налов, содержащее два параллельных канала, каждый из которых состоит из последовательно соединенных первого электронного ключа и интегратора, .сумматора, второго и третьего элект- 36 ронных ключей и блока памяти, входы первых электронных ключей объединены и являются входом устройства обработки, введены четвертый и пятый " электронные ключи и дополнительный сумматор, причем в каждом канале выход интегратора подключен к первому входу сумматора, выход сумматора каждого канала через последовательно соединенные второй электронный ключ, блок памяти и третий электронный ключ подключен к второму входу сумматора противоположного канала, выход блока памяти одного канала через четвертый электронный ключ соединен с первым входом дополнительного сумматора, второй вход которого соединен с выходом сумматора другого канала через пятый электронный ключ, выход дополнительного сумматора является выходом устройства обработки.

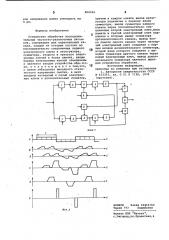

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг,2 - временные диаграммы, поясняющие его работу.

Устройство содержит первые электронные ключи 1, интеграторы 2, сумматоры 3, вторйе электронные ключи

4, блохи 8 памяти, третьи и четвер-, тые электронные ключи 6 и 7, допол800926 нительный сумматор 8 и пятый электронный ключ 9, Устройство работает следующим образом, На вход устройства с выхода фазовых детекторов приемника поступает видеосигнал, состоящий из последовательности информационных прсылок длительностью Т (фиг.2а) . Посылки имеют положительную или отрицательную полярность и содержат п элементов равной длительности, которые могут отличаться друг от друга по амплитуде, а в случае сильного искажения сигнала в приемнике и по полярности.

В момент прихода первого элемента информационной посылки (когда число элементон и является четным) открывается ключ 1 первого канала устройства. При этом происходит накопление информации в интеграторе 2 этого канала, выходное напряжение которого 2О показано на фиг.2б. В момент прихода второго элемента включается ключ 1 второго канала и начинает работать интегратор 2 этого же канала (фиг.2в).

Одновременно открывается ключ 4 первого канала и происходит считывание напряжения с выхода интегратора 2 первого канала и запоминание его в блоке 5 памяти этого же канала .(фиг,2г), Затем, к моменту окончания второго элемента, осуществляется разряд емкости интегратора 2 первого канала. В момент прихода третьего элемента информационной. посылки вновь открывается ключ 1 первого канала и сигнал поступает на интегратор канала, вследствие чего в соответствующем блоке 5 запоминается сумма выход. ного напряжения интегратора второго канала и напряжения, хранящегося н блоке 5 первого канала (фиг,2д). К 40 моменту окончания третьего элемента посылки осуществляется разряд интегратора 2 второго канала и стирание информации в блоке 5 первого канала.

Во время обработки четвертого злемен- Q5 а посылки первый и второй каналы работают по алгоритмам, описанным, .соответственно, для второго и первого каналов в период обработки третьего элемента. В результате, по окончании четвертого элемента посылки,сумма, напряжений от предыдущих трех элементов записывается в блоке 5 перв го канала, ° °

Таким образом, осуществляется почеременная работа обоих каналов устройства, обеспечиваемая с йомощью ключей 1,4 и 6. При этом н блоках

5 памяти поочередно записывается накапливаемая сумма напряжений, являющихся результатом интегрирования 60 отдельных элементов посылки, Величина коэффициентов усиления суммато ров 3 по.первым входам выбирается равной единице, а по вторым входамнемного больше единицы, чтобы компен- 65 сировать потери за счет уменьшения напряжений при хранении их в блоках

5 памяти.

В момент окончания информационной посылки открываются ключи 7 и 9

При этом на один вход сумматора 8 поступает суммарное напряжение от первых (n-1) элементов, хранящееся в блоке 5 первого канала, а на другой вход — напряжение от интегратора второго канала. В итоге на выходе сумматора 8 устанавливается напряжение, являющееся результатом последовательного интегрирования всех элементов принятой информации посылки (фиг.2е). К моменту окончания первого элемента следующей посылки производится гашение информации н блоке 5 первого канала, Интегрирование последующих информационных посылок ныполняется таким же образом, В том случае, если используется сигнал с нечетным числом элементов в информационной посылке, следует обрабатывать первый элемент но втором плече, Далее работа устройства осуществляется так же, как и при четном числе элементов.

Для управления ключами используется система синхронизации,применяеемая в приемном устройстве, Необходимую величину общего коэффициента передачи устройства устанавливают путем соответствующего выбора коэффициента усиления сумматора 8 по обоим входам, За счет включения в каждом канале устройства сумматоров, у которых коэффициент усиления по второму входу больше единицы, а также вторых ключей и блоков памяти возникает возможность при приеме посылок иэ и элементов уменьшить в и раз постоянную времени интеграторов при сохранении прежнего максимального значения напряжения на их выходе, или, для той же постоянной .времени, улучшить линейность интегрирования. Кроме того, в данном устройстве появляется возможность уменьшения величины паразитного статического напряжения ошибки на выходе устройства. Поскольку при сохранении заданной нелинейности интегрирования и-элементного сигнала можно. уменьшить постоянную времени интегратора в и раз, то при этом во столько же раз возрастает максимальная амплитуда,напряжения íà его выходе. Следовательно, для сохранения .заданной амплитуды напряжения на выходе всего устройства уменьшается в п раз коэффициент усиления выходного сумматора по обоим входам. Соответственно, во столько же раз уменьшается паразитное выходное статическое напряжение ошибки. К примеру, для восьмиэлементногo сигнала статичес800926

Формула изобретения (Риг. Я кое напряжение можно уменьшить на

9 дБ.

Устройство обработки последова тельных частотно-разнесенных сигналов, содержащее два параллельных канала, каждый из которых состоит из последовательно соединенных первого электронного ключа и интегратора, сумматора, второго и третьего электронных ключей и блока памятМ, входы первых электронных ключей объединены и являются входом устройства обработки, о т л и ч а ю щ е е с я тем,что, 15 с целью уменьшения выходного статического напряжения ошибки, в него введены четвертый и пятый электронные ключи и дополнительный сумматор, I

Ьричем в каждом канале выход интегратора подключен к первому входу сумматора, выход сумматора каждого канала. через последовательно соепиненные второй электронный ключ, блок памяти и третий электронный ключ подключен к второму входу сумматора противоположного канала, выход блока памяти одного канала через четвертый электронный ключ соединен с первым входом дополнительного сумматора, второй вход которого соединен с выходом сумматора другого канала через пятый электронный ключ, выход дополнительного сумматора является выходом устройства обработки.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

Р 633353, кл. G 01 S 7/30 1976 (прототип) .

ВНИИПИ Заказ 10)14/62

Тираж 743 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4