Устройство для определения рангачисла

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнапистичаских

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

<18ОО989

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свир;ву— (51)М. Кл3 (,, 06 F 5/02 (22) Заявлено 21,03. 79 (21) 2739552/18-24 с присоединением заявки Йо (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 300181. Бюллетень Ne 4

Дата опубликования описания 300131 (53) УДК 881.3 (088. 8) (72) Авторы изобретения

A. A. Коляда и Л

Белорусский ордена Трудового Красного Знамени государственный университет им. В. И. Ленина (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ .РАНГА

ЧИСЛА

Изобретение относится к вычислительной технике и гложет быть исполь зовано в быстродействующих специализированных вычислительных машинах, работающих в поточном режиме и функционирующих в системах остаточных классов (СОК).

Известно устройство определения нормированного ранга. числа 111

Быстродействие этого устройства снижается вследствие производимых .вычислений по модулю P.(i=3,4...n) (n - число модулей системы остаточных классов) по сравнению с результатами вычислений по предыдущим модулям. Кроме того это требует дополнительных аппаратурных затрат. Наиболее близким к предлагаемому является устройство для формирования позиционных признаков непоэиционного кода, содержащее и регистров (и — число модулей системы остаточных классов), блоки памяти, сумматор ранга, блок счммиоования вычетов (2) Несмотря на то, что сую.шрование каждого набора констант может быть распараллелено, быстродействие устройства снижается иэ-за необходимости учета числа переполнений при .суммировании констант.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее и регистров (n — число модулей системы остаточных классов), блоки памяти и сумматор ранга, дополнительно вв"-дены и блоков суммирования вычетов, (и-1) схем сравнения, блок задания знака.и дополнительный блок памяти, причем выход j --го регистра (j"-1,,и) соединен со входом каждо1э,го (j,k,k+1)-го и (j,k, k+2) -ro блоков памяти (K=j -1,,п), входы к-го блока суммирования вычетов (К3,,n) соединены соответственно с выходами (i,K -2, К)-ro (i, К-l, K)-го (i 1...

20 К-1) и (К, К-l, К) -го блоков памяти, i--й вход первого блока суммирования вычетов соединен с выходом (i,ï,ï)-ro блока памяти (1 1,,и) первый и второй входы второго блока. суммирования вычетов соединены соответственно с выходами (1,0,2)-ro и (2,1,2) -го блоков памяти, выходы i-го и (i+.1)-ro блоков суммирования вычетов подключены соответственно к первому и вто30 рому входам 1-й схемы сравнения (1

800989

2,,и -1), выходы первого и п-го блоков суммирования нычетов подключены соответственно к первому и второму входам дополнительного блока памяти, выход которого подключен к первому .входу сумматора ранга, выходы схем сравнения соединены с соответствующими входами блока задания знака, выход которого соединен со вторым:входом сумматора ранга, выход которого является входом устройства.

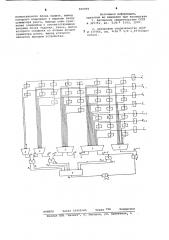

На чертеже предстанлена блок-схема устройства определения ранга числа, Устройство .содержит, регистры 1, блоки 2 памяти, блоки 3 суммиронания вычетов, схемы 4 сравнения, блок 5 )5 задания 3нака, дополнительный блок б памяти, сумматор 7 ранга.

Устройство работает следующим образом.

Вычисляется нормированный ранг

r числа А= сС, Хг,...,Х„. Нормирован—

А 1 ный код 8. д-г,... vL g alp) р-1i

Р Р; Р„

P„j =1, 2,, и; >=Р„, >,,P„, P„Р» "-Р модули СОК числа А, находящиися в ре- 5 гистрах, подается на входы блоков памяти, хранящие значения таблиц, которые по значениям входных цифр числа A определяют соответственно величины, j>-1

e =max )Ч н,= ) 36(1 ) =3 1

Формула изобретения сов), блоки памяти и сумматор ранга, о т л и ч а ю.щ е е с я тем, что, с целью повышения быстродействия, в него введено и блоков суммирования вычетов, и-1 схему сравнения, блок задания знака и дополнительный блок памяти, причем выход j --горегистра (j=l...,n) соединен со входом (j, К, К г 1) -ro и (j, K, К+ 2) -го блоков памяти (K=j -1,,n) входы к-ro блока суммирования вычетов (K=3,,n) соединены соответственно с выходами (i,Ê-2,К)-го, (i, К - 1, К)-го (i 11, ...,К-1) и (К, К - 1, К)-го блокон памяти, (-й вход первого блока суммирования вычетов соединен, с выходом (i, и, n)-ro блока памяти

55 (i=1,...,n), первый и второй входы второго блока суммирования вычетонсое— ) .— jpj (=12,,к;к= 2,,| - ), с,- = Р д. — „, Р, p„(l=c,г,,K; к=1,1,..., )1-2), (1) P„Zq 1

В результате вычисляются все сла.— гаемые выражений (к) KÄ («+ 7 (к+ )1

= Е" Ы 1-с(, Р (K=<2.,„., n-1), к к к (к) > (к+г.) (к+г) „(к =1,z, и г)

2 ° gK К КФг =1

„(ил), d () I „;

Эти сигналы поступают в соответствующие блоки 3 суммирования вычетов для вычисления остаточного кода (Р,, p ) индекса г к (K=1 2, и-1) числа Ар Я.;сС„ . Величины ,ф")...ф ; 11 с выходов блоков 3 подаются на входы схем сравнения, которые вычисляют признаки Нк (K=

1,2...,п-l}, а р(п "1 и р(" )подаются на входы дополнительного блока б па мяти для вычисления величины с1= г <1 ) Я < -1)

Признаки Нк и З опРп ределяются по формулам

Q,ÅÑÞ ГА E(0,(г, щ,} ) О, ВСЛи rÀ 0

Н = 3= (K) (н) K (к) (н)

1, ЕСЛИ Г„ф о,(п „},) 1, ЕСЛИ г >(r где.(г " ) — максимальное значение (н)

П>С1Х К нормированного ранга числа А н системе модулей Р,, Рг>"., Рц,.

Блок задания знака по значениям признаков jj,, Нг, ...,Н определяет число и формирует на выходе 3В . Затем подается на вход сумматора ранга, который по входным величинам Эй и а формирует ранг числа по формуле

ГА =а- 3Е.

В отличие от известного, предлагаемое устройство имеет более высокое быстродействие (2 + 31>oq (-мо2 дульных тактов), так как используемый алгоритм не требует формирования признаков аддитивного переполнения по модулям системы остаточных классов по отдельным модулям. Устройство может работать в поточном режиме, что повышает его пропускную способность.

Устройство для определения ранга числа, содержащее и регистров (n — число модулей системы остаточных класдинены соответственно с выходами (1,0, 2) -го и (2,1,2) -го блоков памяти,выхо-. ды.i)-го и (i+1)-го блоков суммирования вычетов подключены соответственно к первому и второму входам i é схемы сравнения (i= 2,...n-l), выходы первого и и-ro блоков суммирования вычетов подключены соответственно к первому и второму входам доB009R9

? и-2

ВНИИПИ Заказ 10430/65 Тираж 756 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 полнительного блока памяти, выход которого подключен к первому входу сумматора ранга, выходы схем срав— нения соединены с соответствую цими входами блока задания, знака, выход которого соединен со вторым входом сумматора ранга, выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 365701, кл . Ci 06 F 5/02, 1970 .

2. Авторское свидетельство СССР

Р 377766, кл. 6 06 + 5/О 2, 1970 (прототип) .