Комбинационный сумматор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<1>800992

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 16.04.79 (21) 2752934/18-24 с присоединением заявки №вЂ” (23) Приоритет

Опубликовано 3001.81. бюллетень ¹ 4 . (51)М. К„.з

G 06 F 7/50

Государственный комнтет

СССР яо делам нэобретеннй н открытия (53) УДН 681.325.5 (088.8) Дата опубликования описания 31.01.81 (72) Авторы изобретения

Л.В.Дербунович и В.В.Шатилло

Харьковский ордена Ленина поли им. В.И.Ленина (71) За яв и те л ь (54) КОМБИНЛЦИОНН61Й СУММАТОР

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных устройствах высокой информацион5 ной производительности.

Известны различные сумматоры, у. которых увеличиние быстродействия достигается за счет обеспечения работы по реальным задержкам и индикации моментов окончания переходных процессов. Например, асинхронный сумматор, выполненный на триггерах (1).

Существенным недостатком данного сумматора является то, что один разряд сумматора эквивалентен по быстро- 15 действию 7-8-уровневой комбинационной схеме, так как задержка триггера в

2-3 раза больше задержки логических элементов.

Наиболее близким по технической сущности к предлагаемому является комбинационный сумматор, содержащий в каждом разряде элементы И и ИЛИ и реализующий с помощью четырех элементов И и одного элемента ИЛИ логическую функцию суммы данного разряда сумматора и с помощью других четырех элементов И и одного элемента ИЛИ логическую функцию переноса в последующий разряд сумматора (21.

Недостатком такого сумматора является малая надежность при использовании его в асинхронном режиме, так как" сигнал завершения переходного процесса может появляться раньше сигнала на выходе суммы.

Цель изобретения — устранение этого недостатка, т.е. повышение его надежности.

Для достижения поставленной цели в комбинационном сумматоре, содержащем в каждом разряде элементы И и ИЛИ, причем входы первого элемента И сое-. динены соответственно со входами инверсного значения первого, прямого значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы второго элемента И соединены соответственно со входами прямого значения первого, инверсного значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы третьего элемента И соединены соответственно со входами инверсных значений первого и второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы четвертого элемента И соединены соответствен800992

50 но со входами прямых значений первого и второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы пятого элемента И соединены соответственно со входами инверсного значения первого, прямого значения второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы шестого элемента И соединены.соответственно со входами прямого значения первого, инверсного значения второго операндов и входом прямого .значения переноса из предыдущего разряда сумматора, входы седьмого элемента И соединены соответственно со Входами прямых значений первого и второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, выходы первого, второго и третьего элементов

И соедиНены соответственно со входами первого элемента ИЛИ, выходы четвертого, пятого и шестого элементов

И соединены соответственно со входами второго элемента ИЛИ, входы восьмого элемента И соединены со входами инверсных значений первого и второго операндов и входом инверсного значения перЕНООа из предыду»(его разряда сумматора, выходы первого элемента

ИЛИ и седьмого элемента И соединены соответственно со входами третьего элемента ИЛИ и с первыми входами девятого и десятого элементов И, вторые входы которых соединены соответственно с выходом третьего элемента ИЛИ и выходом суммы данного разряда сумматора, входы четвертого элемента ИЛИ подк >ючены соответственно к выходам восьмого и девятого элементов И, а выход — к выходу инверсного значения переноса в последующий разряд сумматора, входы пятого элемента ИЛИ подключены соответственно к выходам второго элемента ИЛИ и десятого элемента И, а выход — к выходу прямого значения переноса в последующий разряд сумматора.

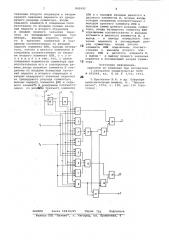

На чертеже представлена функциональная схема одного разряда комбинационного сумматора.

Разряд комбинационного сумматора содер>кит элементы И 1-1 O, элементы

ИЛИ 11-15. Для организации инверсных входов разрядов первого и второго операндов а и Ь используются элементы НЕ 16 и 17.

Выход S †. выход сигнала суммы, выхоцы y„ y+ — выходы соответственно инверсного и прямого значений перейосов в последующий разряд (сигналы завершения переходного процесса в сумматоре), у, у, — входы инверс3 ного и прямого значений переносов из предыдущего разряда (сигналы завершения переходного процесса в предыдущем разряде), z — сигнал, приводящий схему сумматора в инертное состояние, характеризующееся набором выходных переменных s y y (0,0,0). > 2

Логические элементы И и ИЛИ 1-15, входящие в состав каждого разряда комбинационного сумматора, реализуют четыре булевых функции Х,Х, Х>, Х,>.

Наборы, значений выходов булевых функLIHA Х,Х2,Х,Х4 состояниям сумматора, приведенным в табл.1.

Состояние 5-инертное.

В табл.2 — приведены данные истинности комбинационного сумматора.

Схема комбинационного сумматора описывается следующей системой булевых выражений

Х„= ОЪЪ 2 = 4V2 Ь2+аЬV 2

1 1 2

= t>> 2+с Ь 2+ Qgy g

I, Х Об 2

{1) б=х2+Х., Y =x 5+x а

Ут- Х45+ Х

Сумматор работает следующим образом.

В исходном состоянии на вход подается сигнал "0", который приводит схему в инертное состояние. Сумматор находится в состоянии ожидания сигнала разрешения на сложение от предыдущего разряда, которым служит появление "1"на любом из входов или у или у,>,Это говорит о том, что в предыдущем разряде переходной процесс закончился и появляется информация b переносе из предыдущего разряда "0" или "1". При появлении на входе y„ или у сигнала "1" сумматор начи2 нает сложение и переходит из инертного состояния в действительное.

Если при переходе из инертного состояния, в котором сигнал суммы

S=0, в действительное состояние, в котором 5=1, то сигнал завершения (Y 1 или Y =1) появляется тольКо после, появления на выходе сигнала 5=1. Если при переходе из инертного в действительное состояние выход суммы S остается в состоянии

S=O, то выход S не влияет на появление на выходе У 1 или У,2 единицы.

При такой организации схемы сумматора логические элементы И 9 и 10 служат в качестве управляемых временных задер>кек, время появления сиг.нала которых от времени появления сигнала суммы S=1(т.е. 5) является управляющим сигналом..

Если а и Ь устанавливаются одновременно. то выгодно булевые функции

Х и Х З записать в следующем виде

„= Э%2. (())

X =ariz. Ì ã+àÜ г

2 2

800992

Это повысит быстродействие параллельного сумматора, так .как разрешение на суммирование одновременно распространяется и от младшего разряда и от разрядов, у которых входы ар равны 00 и

11.

1 О О О

О 1 О 0

О О 1 О

О О О 1

О О О О

Таблица 2

1 ΠΠ— — О

О О

1 1 О О 0 О 1 О

1 1 О О 1 1 1 О

1 1 О 1 О 1 1 О

1 1 О 1 1 О О 1

1 О 1 О О 1 1 0

1 О 1 О 1 О О 1

О 1

1 О 1 1 О О

1 О, 1 1 1 1 О 1

О О

О О

5р со входами инверсных значении пер . го и второго операндов и входом пр мого значения переноса из предыдущего разряда сумматора, входы четвертого элемента И соединены соответственно со входами прямых значений первого и второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы пятого элемента И соединены соответственно со входами инверсного значения

40 первого, прямого значения второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы шестого элемента И соединены соответственно со входами прямого значения первого инверсного

Формула изобретения

Комбинационный сумматор, содержащий в каждом разряде элементы И и

ИЛИ, причем входы первого элемента

И соединены соответственно со входами инверсного значения первого, прямого значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы второго элемента И соединены соответственно со входами прямого значения первого, инверсного значения второго операндов и входом инверсного значения переноса из предыдущего разряда сумматора, входы третьего элемента И соединены соответственно

Таким образом. предложенная ооганизация комбинированного сумматора выгодно отличает его от известных сумматоров, так как позволяет производить индикацию момента окончания переходного процесса с повышенной надежностью.

Т а б л и ц а 1

О О

1 О

О 1

1 1

О О

800992

ВНИИПИ Заказ 10430/65 . Тираж 758 . Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 значения второго операндов и входом прямого значения переноса из предыдущего разряда сумматора, входы седьмого элемента И соединены соответственно со входами прямых значений первого и второго операндов и входом прямого значения переноса из предыдущего разряда сум матора, выходы первого, второго и третьего элементов И соединены соответственно со входами первого элемента ИЛИ, выходы четвертого, пятого и шестого элементов И соединены соответственно со. входами второго элемента ИЛИ, о т л ич а ю шийся тем, что, с целью повышения надежности сумматора при использовании его в асинхронном режиме, входы восьмого элемента И сое- динены со входами инверсных значений первого и второго операндов и входом инверсного значения переноса из предыдущего разряда .сумматора, выходы первого элемента . ЛИ и седьмого элемеита И соединены cooTBBTGT венно со входФЙйи третьего элемента а"

ИЛИ и с первыми входами девятого и десятого элементов И, вторые входы которых соединены соответственно с выходом третьего элемента ИЛИ и выходом суммы данного разряда сумматора, входы четвертого элемента ИЛИ подключены соответственно к выходам восьмого и девятого элементов И, а выход — к выходу инверсного начения переноса в последующий разряд сумматора, входы пятого элемента ИЛИ подключены соответственно к выходам второго элемента ИЛИ и десятого элемента И, а выход — к выходу прямого значения переноса в последующий разряд сумматора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

9 491949, кл. G 06 F 7/50, 1973.

2.Преснухин Л.Н. и др. шифров >е вычислительные машины. M., "Высшая школа", 1974, с. 138, рис.334 (прототип).