Вычислительный узел цифровойсетки

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

<11800997

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61 } Дополнительное к авт. саид-ву— (22) Заявлено 28. 03. 79 (21) 2742735/18-24 с присоединением заявки №вЂ” (23) Приоритет

Опубликовано 3001.81. Бюллетень ¹ 4

Дата опубликования описания 31.0181 (51)М. КЛ.З

G 06 F 15/31

Государственный комитет

СССР по дедам изобретении н открытий (53) УДК 681. 323 (088.8), )

В.П.Воюн, Е.Л.Вашков, Л.И. Дорожно и Л.Г.Ксзлов

4 Ф,ф

ХИ 1 (72) Авторы изобретения

I 3 \

Донецкий ордена Трудового Красного Знамени институт и Ордена Ленина институт кибернет

ЛН Украинской CCP (71) Заявитель (54 ) ВЫЧИСЛИТЕЛЬНЫЙ УЗЕЛ ЦИФРОВОЙ СЕТКИ

Изобретение относится к средствам вычислительной техники и предназначено для построения устройств, ориентированных на решение задач математической физики, описываемых дифференциальными уравнениями в частных производных.

Известен вычислительный узел цифровой сетки, содержащий процессор, выполняющий последовательно, разряд за разрядом, арифметические и логические операции и два блока памяти, емкостью по 2048 единиц каждый 1) .

Недостатком этого устройства является большое количество оборудования, поскольку каждый вычислительный узел представляет за собой универсальную вычислительную машину, программно настраиваемую на выполнение требуемой последовательности действий, и низкое быстродействие последовательного способа обработки информации.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому устройству является вычислительный узел цифровой сетки содержащий многовходовый сумматор, регистр сдвига, элемент И, группу элементов И. Входы сумматора соединены со входами узла, выход сумматора соединен с последовательным входом регистр;: сдвига. Последовательный выход сдвигового регистра соединен с первым входом -элемента И, па5 раллел.нь!е входы реги,,ра соедин;ны с первыми входами группы элементов

И Выход элемента И соединен с выходом узла, выходы группы элементов И соединены с параллельными выходами узла, Управляющие входы регистра и элементов И соединены с управляющей шиной (2).

Недостатком устройства является узость класса решаемых задач. Решет5 ние дифференциальных уравнений с переменными коэффициентами возможно только при помощи универсальной вычислительной машины по методу "невязок", что значительно увеличивает

20 общее время решения задачи, так как этот метод требует большого количества итераций, а все операции в ЦВМ выполняются последовательно.

Цель изобретения — расширение класса решаемых задач.

Поставленная цель достигается тем, что в вычислительный узел цифpoBQA сетки, содержащий многовходовый сумматор, сдвиговый регистр и

30 группу элементов И, выходы которых

800997 являются группой выходов узла, а входы подключены к группе выходов сдвигового ре> истра. Тактовые входь сдвигового регистра элементов И группы соединены с тактовым входом узла, введены регистры коэффициентов, преобразователи кодов регистр частичных сумм и блок анализа, причем входы регистров коэффициентов соединены с информационным входом узла, а выходы — с входами соответствующих преобразователей. кодов, выходы «оторых соединены с группой входов многовходового сумматора, выход которого соединен с первым входом регистра частичных сумм, второй вход которого соединен с информационным входом узла, — co входом многовходового сумматора и входом сдвигового регистра, вход блока анализа соединен с выходом сдвигового регистра, а выход — с управляющим выходом узла, тактовые входы регистров коэффициентов, регистра частичных суммм и блока анализа соединены с тактовым входом узла, а управляющие входы преобразователей кодов с управляющим входом узла, а также тем, что блок анализа содер>кит элементы памяти, элементы И, ИЛИ, причем первые входы элементов памяти соединены с тактовым входом блока, вход первого элемента памяти подключен к входу блока, первые выходы элементов памяти соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с .соответствующими входами элемента ИЛИ, выход которого является выходом блока, второй выход первого элемента памяти соединен со входом второго элемента .памяти, вторым входом второго элемента И и с выходом блока, второй выход второго элемента памяти соединен со вторым входом .первого элемента И, а также тем, что преобразователь кодов содержит два элемента НЕ, два элемента И, элемент ИЛИ, причем выходы первого и второго элементов НЕ соединены соответственно с первыми входами первого и второго элементов И, выходы которых подключены к соответствующим входам элемента ИЛИ, выход которого является выходом преобразователя,. вторые входы элементов И, третий вход первого элемента И соединены соответственно с управляющим входом преобразователя, вход которого соединен со входом первого элемента HE и с третьим. входом второго элемента И.

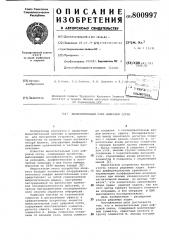

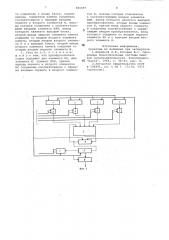

На фиг. 1 изображена блок-схема .Узла> на фиг. 2 — блок анализа; на фиг. 3 — преобразователь кода.

Вычислительный узел цифровой сетки состоит из регистров 1 коэффициентов, входы которых соединены с информационно шиной, а выходы — co

4О

á5 входами преобразователей 2 кодов, выходы которых соединены с входами многовходового сумматора 3, выход которого соединен.с входом регистра

4 частичных сумм, параллельный вход которого соединен с инф>рмационной шиной, а-выход соединен со входом многовходового сумматора 3 и с входом сдвигового регистра 5, выход которого соединен -" входом группы элементов И б, а выход младшего разрядно входом блока 7 анализа, выход «оторого является последовательным выхоцом узла, Выхоц группы элементов

И 6 является параллельным выходом узла. Управляющие входы регистров 1 коэффициентов, регистра 4 частичных сумм,сдвигового регистра 5, группы элементов И б и блока 7 анализа соединены с управляющей шиной, а преобразователей 2 кодов с последовательными входами узла.

Блок 7 анализа предназначен дпя управления режимом работы соответствующих преобразователей 2 кодов соседних узлов.

На фиг. 2 изобра>кена блок-схема блока 7 анализа, который состоит иэ

2 элеме 1ТоВ памяти 8 и 9, двух элементов И 10 и 11, элемента ИЛИ 12.

В цифровом узле применяется алгоритм сокращенного умножения. По этому алгоритму контролируются текущий

P-й и младший (Р+1) -й разряды множителя, которые хранятся в элементах памяти 8 и 9.. На остальных элементах собрана схема сравнения, на выходе которой устанавливается сигнал Х, равный логической единице, если контролируемые разряды неравны и необходимо делать сложение или вычитание. Если сигнал X равен единице, то проводят вычитайие, а если нулю — сложение.

Преобразователь кодов 2 предназначен для формирования прямого или дополнительного кодов содержимого регистров 1 коэффициентов, или пропуска кода тождественного нулю при определенных значениях последовательно выхода соответствующего соседнего узла. На фиг. 3 представлена блок-схема преобразователя 2 кода, который состоит из двух элементов НЕ 13.и 14, элементов И 15 и 16 и элемента ИЛИ 17.

Если сигнал Х< равен О,то на выходе элемента ИЛИ 17 будет тождественный нуль. При Х равном единице на выход элемента ЙЛИ 17 поступает обратный код регистра 1 коэффициентов, а при X равном нулю — прямой код. Рассматриваемый узел предназначен для реализации зависимости

О.. =9" 0..>1> .О.. С 0, . +Н. д, - (л)

f,g +1,g ! к которой сводится решение дифференциальных уравнений с переменными

800997

65 коэффициентами равзностным методом с помощью алгоритма простой итерации.

Здесь i u j-èíäåêñû строки и столбца сеточной области, а,,b„.

С . d. u f. — соответственно

") 3 коэффициенты и правая часть разностных уравнений, U„ „., U, U„

U . — . значений искомой функ1|йи

1, 1+ в соседних узлах на предыдущей итерации, U.: — новое приближение решения. Вся информация.в узле представляется в дополнительном коде целыми числами.

Работа устройства происходит в два этапа. На первом, подготовительном этапе, в регистры 1 коэффициентов заносятся значения соответствующих коэффициентов, которые в общем случае имеют m разрядов, а в регистр 4 — m-разрядное значение а сдвиговый регистр 5 и элеменI ты задержек переноса многовходового сумматора 3 обнуляются. На этом заканчивается подготовка устройства к работе. Собственно решение происходит на втором этапе, который состоит в определении последовательности U.., к .= 0,1,2,... Определе1 > К ние каждого 0„ . при и>-разрядном

1i3 представлении. информации в регистрах

1 коэффициентов и частичных сумм 4 требуется m циклов. Каждый из m циклов выполняется следующим образом: на блоке 7 анализа происходит анализ двух младших разрядов сдвигового регистра 5, и результат анализа поступает на последовательные входы соседних узлов. Преобразователи кодов

2 настраиваются на пропуск прямого или обратного кода регистров 1 коэффициентов. Для получения дополни-. тельного кода в первом такте в соответствующие элементы задержек перено са многовходового сумматора 3 записы0 вается единица. Во втором такте происходит суммирование младших разрядов регистра частичных сумм 4 и регистров 1 коэффициентов на многовходовом сумматоре 3. В следующем такте происходит суммирование следующих разрядов. Таким образом за я тактов (для двухмерных задач) и (я + 2)(для трехкамерных задач) в регистре 4 частичных сумм получается сумма частичных произведений от умножения коэффициентов на младший разряд сдвигового регистра 5, которая поступает на вход данного регистра с выхода многовходового сумматора 3. В (m +2) — такте регистр

4 частичных сумм сдвигается в сторону младших разрядов для уменьшения суммы частичных произведений 4 в два раза, а сдвиговый регистр 5 для умножения на следующий разряд, в старший разряд которого перезаписывается значение младшего разряда регистра частичных сумм 4. На этом заканчивается очередной цикл.

Таким образом, в последнем (m + 2) M такте m-го цикла в сдвиговом регистре 5 получается значение очередного приближения. При необходимости индицировать результат или передать его для дальнейшей обработки, на управляющие входы группы элементов И 6 подается сигнал, по которому на выходе группы элементов И б устанавливается значение сдвигового регистра 5. О Таким образом прохождение очеред(К+ 1) ного приближения 0 к решению

I уравнения происходит за (m +2). m тактов. Если t — время одного такта в секундах,то общее время решения 5 определяется как

Т = (а+2)° . m. с.

Данное устройство, по сравнению с известными, позволяет существенно расширить класс решаемых задач без щ0 увеличения затрат времени íа »х решение за счет обеспечения возможности непосредственного решения задач с переменными коэффициентами.

Формула изобретения

1.Вычислительный узел цифровой сетки, содержащий многовходовый сумматор, сдвиговый регистр и груп— пу элементов И, выходы которых являются группой выходов узла, а входы подключены к группе выходов сдвигового регистра. Тактовые входы сдвигового регистра элементов И группы соединены с тактовым входом узла, отличающийся тем, что, с целью расширения класса решаемых задач в него введены регистры коэффициентов, преобразователи кодов, регистр частичных сумм и блок а»ализа, причем входы регистров коэффициентов соединены с информационным входом узла, а выходы — c входами соответствующих преобразователей кодов, выходы которых соединены с группой входов многовходового сумматора, выход которого соединен с первым входом регистра частичных сумм, второй вход которого соединен с информационным входом узла, а выход — co входом многовходового сумматора и входом сдвигового регистра, вход блока анализа соединен с выходом сдвигового регистра, а выход — с управляющим выходом узла, тактовые входы регистров коэффициентов, регистра частичных сумм и блока анализа соединены с тактовым входом узла, а управляющие входы преобразователей кодов — с управляющим входом узла.

2. Узел по п.1, о т л и ч а ющ.и и с я тем, что блок анализа содержит элементы памяти, элементы И, ИЛИ, причем первые входы элементов памяти соединены с тактовым входом блока, вход первого элемента памя800997 ти подключен к входу блока, первые выходы элементов памяти соединены соответственно с первыми входами первого и второго элементов И, выходы которь.х соединены с соответствующими входами элемента ИЛИ, выход которого является выходом блока, второй. выход первого элемента памяти соединен со входом второго элемента памяти, вторым входом второго элемента И и с выходом блока, второй выход второго элемента памяти соединен со вторым входом первого элемента И.

3. Узел по п.2, о т л и ч а ющ и .й с я тем, что преобразователь кодов содержит два элемента НЕ, два элемента И, элемент ИЛИ, причем выходы первого и второго элементов

HE соединены соответственно с первы-. ми входами первого и второго элементов И, выходы которых подключены к соответствующим входам элемента

ИЛИ, выход которого является выходом преобразователя, вторые входы элементов И, третий вход первого элемента

И соединены соответственно с управ-: ляющим входом преобразователя, вход которого соединен со входом первого элемеита НЕ и с третьим входом второго элемента И.

Источники информации, принятые во внимание при экспертизе

1.Евреинов Э.В., Косарев Ю.Г. Однородные вычислительные системы лицевой производительности. Новосибирск, "Наука", 1966, с. 38-41, рис. 8.

2.Авторское свидетельство СССР

¹ 546891, кл. G 06 F 15/34, 1975 (прототип) .

800997

Ъ

%з ь сз ъ

Риа. Р

Составитель Н.Палеева

Редактор E.Ëóøíèêoâà ТехредМ.Коштура Корректор Н.Швыдкая

Заказ 10430/á5 Тираж 756 Подписное

BHHHIIH 1 осударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП"Патент", г.ужгород,ул.Проектная,4