Перемножитель двух аналоговыхсигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 03. 08. 78 (2() 2610479/18-21 (51) М. Кл. с присоединением заявки М—

G G 7/16

Государственный комитет

СССР по делам изобретений н открытнй (23) Приоритет

Опубликовано 3101.81. Бюллетень М 4

Дата опубликования описания 31.0181 (53) УДК 621. 378.:.> (088.8) (72) А вторы изобретения

Н.П.Алимов, П.H.Лойтер и Л.7. (71) Заявитель (54) ПЕРЕЧНО»!ИТЕЛЬ ДВУХ АНАЛОГОВЫХ СИГНАЛОВ

Изобретение относится к вычисли-. тельной технике.

Известно устройство для перемножения аналоговых сигналов, содержащее,рсновной аналоговый умножитель, выход которого соединен с входом операционного усилителя, охваченного отрицательной обратной связью, и цепь. компенсации нелинейности по первому входу умножителя в предположении, что нелинейность по второму .входу мала (1J.

Недостатком известного устройства является нелинейность.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее аналоговый умножитель, входы которого соединены с входными шинами, а выход через резистор соединен с суммирующим входом операционного усилителя, соединенным через второй резистор с общей шиной, причем выход операционного усилителя соединен с его вычитающим входом через третий резистор и цепь компенсации )2).

Однако такое устройство не обеспечивает достаточной компенсации остаточного напряжения.

Цель изобретения — повышениФ сто пени компенсации остаточного набуря жения.

Поставленная цель достигается те>, что в устроиство перемножения двух аналоговых сигналов содержащее аналоговый умножитель, входы которого соединены с входными шинами, а выход через резистор соединен с суммирующим входом операционного усилителя, соединенного через второй резистор с общей шиной, причем выход операционного усилителя соединен с его вычитающим входом через третий резистор

15 и цепь компенсации введен дополнительный резистор, а цепь компенсации выполнена из двух дополнительных аналоговых умножителей, первые входы которЫх соединены с общей шиной, вто20 рой вход каждого из которых соединен с одной из входных шин, а выход через дополнительный резистор соединен с вычитающим входом операционного усилителя.

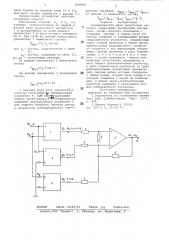

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит аналоговые умножители 1-3, резисторы 4-8, one30 рационный усилитель 9. Входные сиг800999

= U„° 0+dlX+ О, SblX,2 Х -":U 0+0+»1У.

ЬЕ |х.Ь У

ВНИИПИ Закан »О »О»аЬ тираж »на Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Нс1ЛЫ Пот!2Е!Ы Нс\ ВХОДНЫЕ ННIНЫ 10 И 11

Выхадl101 clиГIIB.»I снимс1ется с ВыхОДа 1 2

Предлагаемое устройство работает следующим образом. умна Ecnc;MLIc с1|гналы U u U noх У ступают соответственно на первый и

ВТОРой ВХОД аНаЛаlпОВОГО УМ!!0>!<ИТ(.JEft

1 И О Ц НОВ 1:»ЕМ(Е1ИО kl B 13 ХОД II P PB OI О умна)|(ителя 2 и В?:ОЦ ВтОрОГО ?»е!11ожитеЛЯ 3 ПРИ ЭТОМ IB ВЕ>!ХОДЕ саисЫIО1 ОВОГО умножителя 1 .| ЫХ с- П„U)+ ЬХ еЛУ, Гд<- Ux -" се1 нал» ПОД!<.11к)ч е| 1 llе»|й Ес шине

IJ> сиге!ал, поданный на шину 11, дх ду — ос|таточные сигналы, | йа выхс»де умножителя 2 выделяеTOH сигнал

На Выходе умножителя 3 выделяется

СНГkIBJI ж

0 выходов веех,трех умножителей сигналы посту»1!ают". Q .операционный уckEJlklòå?lü 9. при! саот " ВетcóIIóþùeì выборе резисторов, 3а (? коэффициенты передачи операционного усилителя 9 для каждого Входного сигнала равны, В резульTате алгебраического сум рова!!Е!я Сигналов 08ь „О, и 0

Е1Е»|Х1 9Ь|Х 2 Е3(3> 3

Ilа ВыхОде 12 Выделяется сиГHBJI

O "-U — u

I»,blX, ЬЬ!Х (ЬЫХ2 I»,b(Õ.З Х У

Формула изобретения

Перемнажитель двух аналоговых сигналов, содержаций аналоговый умножитель, входы которого соединены с входными шинами, а выход через резистор соединен с суммирующим Входом

Операционного усилителя, соединенным через второй резистор с общей шиной, причем Выхоц операционного усилителя co(3JXIIEI

ЧТО, С ЦЕЛЬ|О ПОВЫШЕНИЯ ;-.:.ЕПЕНИ КОМпенсации остаточного напряжения в него Введен дополнительный резистор, а цепь компенсации ве>|полнена из двух дополнительных аналоговых умножите"?О лей, первые Вхоцы которых соединены

С Общей шиной,. второй вход кажд<?го из которых соединен с одной из входных шин, а выход через дополнительный резистор соединен с Выеитающим входом операционного усилителя.

Источники информации, принятые во внимание при экспертизе

1. CElpBI3ou k!k!1< Ilo нелинейным схемам.

Под. ред. Д.Шейнгольда. иМирп; 1977, с. 241.

Фо 2.Патент Японии Е1 33309, кл. 110 Н 2, 79.09,71,