Устройство перемножения двуханалоговых сигналов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е

Союз Советских

Социалистических

Республик

<щ8О1 ООО

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИЕДЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 02..02.79 (21) 2722193/18-21 с прмсоединением заявки Ио— (23) Приоритет—

Опубликовано 3021Â1. Бюллетень Йо 4

Дата опубликования описания 31.0181 (5 )щ, ф(л.з

G G 7/16

Государственный комитет

СССР но делам изобретений и открыти и (53) УДК 681. 374. (088.8) (72) Авторы изобретения

П.П.Першенков, Ю.И.Петров, Б.В.Султанов (71) Заявитель

Пензенский политехнический институт (54) УСТРОИСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ДВУХ

АНАЛОГОВЫХ СИГHAJIOB

Изобретение относится к вычислительной технике.

Известно устройстно для аналогового перемножения двух сигналов, содержащер дна канала, суммирующий элемент, усилитель, полевой транзистор в цепи управления второго усилителя (11 .

Недостаток устройства заключается в малой точности умножения переменных сигналов.

Наиболее близким к предлагаемому .по технической сущности является устройство, содержащее дна нходных ключа, входы управления подключены к двум выходам блока управления, а выходы — соответственно к первым входам двух интеграторов, второй вход первого из которых соединен с выходом источника опорных напряжений через третий ключ, вход управления которо- л0

ro соединен.со входом управления первого ключа, нуль-орган и формиро- ватель интервалон времени, выходы ко-, торых подключены ко входам блока управления, и четвертый ключ (2j.

Данное устройство не обеспечивает достаточной. точности.

Цель изобретения — повышение точности. 30

Поставленная цель достигается тем, что в устройство, содержащее первый и второй входные ключи, входы которых соединены с входными шинами, входы управления подключены к первому и второму выходам блока управления, а выходы — соответственно к первым входам первого и второго интеграторов, второй вход первого из которых соединен с выходом источника опорных напряжений через третий ключ, вход управления которого соединен со входом управления первого ключа, первый нуль-орган н формирователь интервалов времени, выходы которых подключены ко входам блока управления и четвертый ключ, введены пятый ключ, аналоговый блок памяти, второй нуль-орган, RS-триггер и дифференциальный усилитель, один вход которого подключен ко второму выходу источника опорных напряжений, второй вход соединен с выходом первого интегратора, входом первого нуль-органа и первым входом аналого.— ного блока памяти, второй вход которого соединен с третьим выходом блока управления, а выход через пятый ключ, вход управления которого соединен со вторым выходом блока управ801000

V0

Ф, = .! н„

{где U — среднее значение напряжения 0 (с) за интервал времени

7 - постоянная времени первого

\ интегратора по первому входу), в течение которого интегратор 1 разрядится до нуля, измеряется формирователем 14. Далее но команде с блока 13 ключ 7 закрывается и открывается ключ 3 на интервал времени t, который задается формирователем 14.

К концу этого интервала времени напряжение на выходе интегратора 1

65 ления, подключен ко второму входу второго интеГратора, выход которого через второй нуль-орган соединен с первым входом RS-триггера, второй вход которого подключен к четвертому выходу блока управления, причем выход дифференциального усилителя соединен через четвертый ключ с дополнительным входом первого интегратора, а вход управления четвертого ключа и вход формирователя интервалов времени подключены к пятому и шестому выходам блока управления.

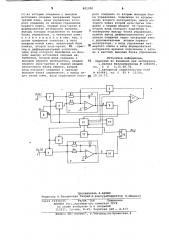

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит интеграторы

1 и 2, ключи 3-7, источник 8 опорных напря>кений,нуль-органы 9 и 10, дифференциальный усилитель 11, аналоговый блок 12 памяти, блок 13 управления формирователь 14 интервалов вре- 20

I мени, RS-триггер 15, входные сигналы подачи на шины 16 и 17.

Предлагаемое устройство работает следующим образом.

В исходном состоянии ключи 3,4,6 25 и 7 закрыты, выходное напряжение интегратора 2 равно нулю, а первый интегратор 1 заряжен до значения опорного напряжения Ug источника

8 опорных напряжений. Йнтегратор 1 устанавливается в это исходное состояние в конце каждого цикла преобразования путем открывания ключа 5, в результате замыкается обратная связь усилителя 11, и интегратор быстро заряжается до 00 выходным т током усилителя.

В первом такте по команде с блока 13 одновременно открываются ключи 4 и 7 и происходит интегрирование входных напряжений. Интегратором 2 40 интегрируется напряжение U<(t) в течение интервала времени с задаваемогО с блока управления, а интегратор 1 разряжается до нуля напряжением U„ {t) .Полярность опорного на-, 45 ряжения U0 задается противоположной полярности напряжения U„(t). Момент. равенства выходного напряжения первого интегратора 1 нуля фиксируется нуль-органом 9. Интервал времени достигнет значения, определяемого выражением

UQ 1

° 1 иь .1 где . — постоянная времени первого интегратора по второму входу, с -с.„/и — интервал времени, и - масштабный коэффициент, или

Ц 1 Ц01 0 2. и„р .ц

Это напряжение запоминается блоком

12. За интервал времени t напряжение на выходе второго интегратора 2 достигнет значения, определяемого выражением и Ч2.

2. где U — среднее значение напряжения 0 (t) за интервал tä

1 — постоянная времени второго интегратора по первому входу.

Интервал времени с выбирается таким образом, чтобы он был несколько больше суммы интервалов с и

1 с (с„,>,с,,- с ), т.е. чтобы к моменту окончания t напряжение на вь!ходе интегратора 1 достигло установившегося значения. Интервал времени задается в и раз меньше, чем с целью уменьшения динамической погрешности.

Во втором такте закрывается ключ

4, открываются ключи 5 и 6, триггер

15 по команде с блока 13 перебрасывается в единичное состояние.

В течение второго такта происходит разряд второго интегратора 2 до нуля напряжением с выхода блока 12.

Нуль-орган 10 фиксирует момент равенства выходного напряжения интегратора 2 нулю и сбрасывает триггер 15

В результате на выходе триггера

15 получим импульс длительность которого определяется выражением где К вЂ” коэффициент преобразования.

Через открытый ключ 5 первый интегратор 1 устанавливается в исходное состояние, т.е. заряжается до напря>кения 00 . Далее цикл преобразования может повторяться.

Формула изобретения

Устройство для перемножения двух аналоговых сигналов, содержащее первый и второй входные ключи, входы которых соединены с входными шинами, входы управления подключены к первому и второму выходам блока управления, а выходы — соответственно к первым входам первого и второго интеграторов, второй вход первс801000

Составитель А.Артюх

Редактор Р.Пчелинская Техред N.ÊîøòóðàÊîððåêòoð Н.Швыдкая

Заказ 10430/65 Тираж 756 Подписное

ВНИИПИ Госy ;, ÷ðñòâåíãого комитета СССР по селам изобьете и и открытий

11303,осква, Ж-35, Раушская наб., д.4/5

Филиал ПП." Патент", г.ужгород,ул.Проектная,4 го из которых соединен с выходом источника опорных напряжений через третий ключ, вход управления которого соединен со входом управления первого ключа, первый нуль-орган и формирователь интервалов времени, выходы которых подключены ко входам блока управления, и четвертый ключ, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены пятый ключ, аналоговый блок памяти, второй нуль-орган, RB -триггер и дифференциальный усилитель, один вход которого подключен ко второму выходу источника опорных напряжений, второй вход соединен с выходом первого интегратора, входом первого нуль-органа и первым входом аналогового блока памяти, второй вход которого соединен с третьим выходом блока управления, а выход через пятый ключ, вход управления которого соединен со вторым выходом блока управления, подключен ко второму входу второго интегратора, выход которого через второй нуль-орган соединен с первым входом Р5-триггера, второй вход которого подключен к .четвертому выходу блока управления, причем выход дифференциального усилителя соединен через четвертый ключ с дополнительным входом первого интегратора, а вход управления четI0 вертого ключа и вход формирователя интервалов времени подключены к пятому и шестому выходам блока управления.

Источники информации, 15 принятые во внимание при экспертизе

1.Заявка Великобритании Р 1446081, кл. G 4 G 11.08.76.

2.Авторское свидетельство СССР

Р 464841, кл. G 01 R 21/00, щ 29.10.73.