Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалнстнческкк

Ресвублкк

«i1801101 (6f) Дополнительное и авт. санд-ву 9 490183 (22) Заявлено 220379 . (21) 2739670/18-24 (51) М. Кл. ) G 11 С 15/00 с присоединением заявим É9

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 30.0 131. Бюллетень ИЯ 4

Ю) ДИ 681 ° 327. .66 (088.8) Дата опубликования описания ЗОО 131,,72) Авторы 1 нзобретення Л. Г. Теницкий, В.Ф. Нестерук и В.И. Потапов ; I (71) Заявитель

Омский политехнический институт (54 ) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано при построении у тройств хранения дискретной информации.

По основному авт.св. 9 490183 известно логическое запоминающее устройство (ЛЗУ), содержащее регистр признаков обращения, числовые линейки, разрядные шины записи, считывания и чтения, линейные шины записи . и считывания которых подключены соответственно через разрядные элементы

ИЛИ и разрядные элементы И к выходам регистра слова, через усилители чтения — к входам регистра регенерации и через адресные формирователи записи и считывания — к выходам адресных элементов И, управляющие входы которых соединены через управляющие элементы ИЛИ с шинами управления, подключенными к управляющим входам разрядных элементов И, и вспомогательных разрядных элементов И, функциональные входы которых соединены с выходами регистра регенерации, выходы подключены к разрядным элементам ИЛИ, шину опроса, линейные элементы "Запрет" по числу разрядов устройства, выходной элемент ИЛИ, входы которого подключены к «ыходам усилителей чтения, а выход — к функциональному входу элемента И, управляющий вход которого соединен с шиной опроса, функциональные входы

i õ (i=1...п) линейного и разрядного элементов "Запрет" и (n+1) — го, (n+

+2) — го линейных элементов "Запрет" псдключены соответственно к выходам

i-х и (и+1)-го, (и+2)-го разрядов регистра признаков обращения, управляющие входы i-x разрядных и линейных элементов "Запрет" н (и+1)-го, (n+2)-го линейных элементов "Запрет" соединены с соответствующими разрядной и линейной шинами управления, выход каждого линейного элемента "Запрет" подключен к выходам двух адресных элементов И соответствующей числовой линейки, выход каждого разрядного элемента "Запрет" соединен со входом соответствующего разрядного лемента ИЛИ (1 ).

Недостатком этого ЛЗУ является его низкое быстродействие.

Бель изобретения — повышение быстродействия ЛЗУ.

Поставленная цель достигается тем, что предлагаемое устройство содержит дэухвходовые переключатели по числу разрядов регистра регенерации, пер801101 вые входы которых соединены с шиной управления,. вторые входы и выходы подключены соответственно- к выходу соответствующего разряда регистра реге, нерации и к дополнительному запрещающему входу разрядных элементов 5

"Запрет".

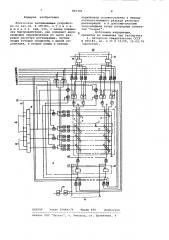

На чертеже изображена структурная схема ЛЗУ.

ЛЗУ содержит накопитель 1, состоящий из числовых линеек 2 на тороидальных сердечниках 3 с прямоугольной петлей гистерезиса, имеющих разрядные шины записи 4, считывания 5 и чтения б и линейные шины записи 7 и считывания 8.

Каждая из разрядных шин записи 4 1% и считывания 5 и каждая из линейных шин записи 7 и считывания 8 подключены к выходам соответствующих разрядных формирователей записи 9 и считывания 10 и адресных формировате- 2О лей записи 11 и считыв-ния 12. Вход каждого адресного формирователя записи и считывания связан с выходом адресного элемента И 13 или 14, управляющие входы которых подключены 2 соответственно к выходам управляющих элементов ИЛИ 15 и 16. Функциональные входы адресных элементов И

13 и 14 цепей записи и считывания каждой числовой линейки 2 соединены с выходом соответствующего линейного элемента "Запрет" 17. Функциональные входы i õ(1=1,n) линейного и разрядного элементов "Запрет" 17 и 18 подключены к выходу i-го разряда регистра 19 признаков обращения, а их управляющие входы соединены соответственно с линейной 20 и разрядной 21 шинами управления.

Функциональные входы (n +1)-ro и (и+2)-ro линейных элементов "Зап- 40 рет" 17 подключены соответственно к выходам (n+1)-го и (и+2)-го разрядов регистра 19 признаков обращения, а их управляющие входы соединены с линейной шиной 22 управления.

У авляющие входы разрядных элементов И 23-26 подсоединены к управляющим шинам 27-30. Функциональные входы i õ разрядных элементов И 23, 25 и 24, 26 связаны соответственно с инверсными и пряьым выходами i-го разряда регистра 31 слова. Выходы

i-х разрядных элементов И 23 и 24, разрядных элементов "Запрет" 18 и вспомогательных разрядных элементов И 32 подключены к входам разрядных элементов ИЛИ 33, а выходы i-x разрядных элементов И 25 и 26 и элементов И 34 соединены со входами элементов ИЛИ 35 i-й разрядной цепи.

Выходы i-x элементов. ИЛИ 33 и 35 подключены соответственно к входам разрядных формирователей считывания

10 и записи 9.

Управляющие входы элементов И 32 соединены с шиной 36 управления, 65 а элементов И 34 — с шиной 37 управления. Функциональные входы i-x элементов И 32 и 34 подключены к выходу i-го разряда регистра 38 регенерации, а вход этого регистра — к выходу i--гс усилителя 39 чтения, подсоеди" ненного к шине б чтения i é разрядной цепи. Управляющие входы усилителей чтения соединены с шиной 40 стробирования, а их выходы — с выходными шинами 41 логического запоминающего устройства и с входами выходного элемента ИЛИ 42, выход которого подключен к функциональному входу элемента И 43. Управляющий вход элемента

И 43 соединен с шиной 44.сброса, входы управляющих элементов ИЛИ 15 и 16соответственно с шинами 29,30,37 и 27, 28, 36 управления.

Регистры 19 и 31 имеют шины 45 и 46 сдвига, регистр 38 регенерациишину 47 сброса, i -e, (и+1) -й и (n+

+2)-й разряды регистра 19 — входные шины 48 и 49, регистр 31 слова— входные шины 50. Первые входы двухвходовых переключателей 51 соединены с шиной управления 52, а второй вход и выход каждого i-ro (i-1, n) переключателя подключены соответственно к выходам i-ro разряда регистра 38 регенерации и к дополнительному запрещающему входу разрядных элементов

"Запрет" 18.

Обозначим значение i-го разряда двоичного кода, хранящегося в числовой линейке У|, значение сигнала в

i-й разрядкой цепи - Х .Результат логической операции t(X, ; Y,) который остается в числовой линейке, Pi, результат логической операции (0(х ° y ), который образуется на

i I

i-ой разрядной шине б чтения, ;.

Логические операции, выполняемые в логическом запоминающем устройстве, приведены в таблице.

Работает устройство следующим образом.

До начала работы в каждую i-ю числовую линейку накопителя 1 записывается двоичный код приоритета А; =2 — 1, à B (п +1)-ой, (n+2) числовых линейках хранится код приоритета А„, а на регистре регенерации запйсан код приоритета A ° i-го ( значащего разряда двоичного числа В,.

В первом такте по входным шинам

48 в регистр признаков обращения поступает код двоичного числа В„

Во втором такте на шины управления

20, 22, 28, 52, стробирования 40 и опроса 44 подаются единичные сигналы.

При этом i-e, (и+1)-й, (n+2)-й линейные элементы "Запрет" закрыты.

Часть из разрядных элементов "Запрет"

18, каждый элемент которой соответствует единичным разрядам кода приоритета А;, хранящегося на регистре 38

801101

Разрядный сигнал возбуждения

Возбужденная шина управления

Значения аргументов и функций

Возбужденные адресные и разрядные формирователи

Вы пол ня емая операция

Х 0 0 1 1

Х1 1 1 0 0

У; 0 1 0 1

Р! 0 1 - 1 1 Р!=Х; УУ1 . Qi 0 0 1 . 0 ф=Х; ьу;

9 и 11

Х- 1!

1 1 0 1 Р; =Х;- У

1 0 0 0 Я;=Х ФУ

X. =1 !

9 и 11

29 р, !

0 1 0 0 Р;=У! дХ

0 0 0 1 Я;=Х ЛУ

Х. =1 !

10и12

0 0 0 1 Р, =Х; ЛУ;

0 1 0 0 1 ; =У аХ;

Х. =1

10 и 12

П р и м е ч а н и е. Символами D — У, 4, Vf A, обозначены соответстf венно операции запрета, импликации, стрелка Пирса, диэъюнкция и конъюнкция. регенерации, закрыты. Оставшаяся часть элементов "Запрет" 18 находится в пров одящем состоя ни и .

Е,"нничные сигналы с выходов

i-x(i k,g,...m) разрядов регистра признаков обращения через соответству- 5 ющие, не закрытые сигналами с переключателей 51, разрядные элементы

"Запрет" 18 и связанные с ними элементы ИЛИ 33 возбуждают i-e разрядные формирователи 10 считывания. На шинах 6 чтения появляется двоичный код, соответствующий результату операции B аА, который подается (!, ."rn на входй у силителей 39 чтения. Выходные сигналы усилителей чтения поступают на входы элемента.ИЛИ 42, сигнал 15 с его выхода — на функциональный вход выходного элемента И 43, на выходе которого формируется значение величины У.

Управляющие работой логического 2О запоминающего устройства в третьем такте организуется в зависимости от значения величины У.

Если У=О, то в третьем такте производится сброс в "0" содержимого регистра 19 и логическое запоминающее устройство переходит в исходное состояние.

Если же величина У, сформированная во втором такте, равна "единице", то в третьем такте формируется признак

A. к-ro разряда числа В g для

К чего на линейные шины 22, 2 управления и на шину 40 стробирования подаются единичные сигналы, а на остальные шины управления — нулевые сигналы. В результате единичные сигналы с выходов i=x(i=k,,...m) разрядов регистра признаков обращения через

i - е (i =1, n) линейные элементы "Запрет" 17 и адресные элементы И 14 поступают на входы соответствующих

i-x(i=k,g,...m) адресных формирователей 12 считывания,, а единичные сигналы с инверсных выходов разрядов регистра слова через открытые элементы И 23 и элементы ИЛИ 33 проходят на входы разрядных формирователей 10 считывания.

В i x(i Ê,f,...m) числовых линейках выполняются операции P = OhY, 4 и Я,. =1 ;ь0, а на разряд!ых шинах 6 чтения образуется код числа A =Q Ai,.

i=wan..m который заносится с выходов усилй телей чтения в регистр 38 регенерации и поступает на выходные шины 41.

В четвертом такте в первый разряд регистра слова и во все разряды регистра признаков обращения заносятся единицы.

В каждом последующем (i+4)-й (i =1, n) такте на шины 45 и 46 сдвига регистров 19 и 31 и на шину 30 управления подаются единичные сигналы.

В результате в каждом (i+4)-м такте в i-e разряды с i-й по (n+2)-ю числовых линеек записываются "единиць ", в (n+4) такте в каждой 1-й (i 1, n) числовой линейке формируется код

A = 21, а в (n+1) é и (n+2) é чис-! ловых линейках 2 - код числа (2 -1) .

В (n+5) такте производится сброс в "0" кода регистров 19, 31 и логическое запоминающее устройство переходит в исходное состояние.

801101

Формула изобретения

ВНИИПИ Эаказ 10440/70 Тираж 656 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Логическое запоминающее устройство по авт.св. Р 490183, о т л и ч а,ю щ е е с я тем, что, с целью повышения быстродействия, .оно содержит двухвходовые переключатели по числу разрядов регистра регенерации, первые входы которых соединены.с шивой управления, а вторые входы и выходы подключены соответственно к выходу соответствующего разряда регистра регенерации и к дополнительному запрещающему входу разрядных элементов "Запрет".

5 Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 490183, кл . 6 11 С 15/00, 15.02.74 (прототип).