Устройство для контроля блоковпамяти

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТИЛЬСТВУ ни801105 (61) Дополнительное к ввт. свид-ву Р 607283 (51)PA. Кл з

G 11 С 29/00 (22) Заявлено 26,0379 (21)2739829/18-24 с присоединением заявки ¹ (23) Приоритет—

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 300181 Бюллетень HB 4

Дата опубликования описания 3001.81 (53) УДК681. 327 (088. 8) (72) Авторы изобретения

О,Н.Фунтиков и Л.А,Колосков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

Изобретение относится к запоминаю.щим устройствам, и может использоваться при проектировании стендовой аппаратуры для контроля блоков памяти.

Ifo основному авт. св. 9 607283 известно устройство, содержащее источник управляющих импульсов, первый выход которого подключен ко входу формирователя опросного тока, регистр числа, входы которого соединены со входами устройства, а выходы — с одними входами блока сравнения, блок индикации, элементы И, дополнительный формирователь опросного тока и счетный триггер, один выход которого подключен к пер- 15 вому входу первого элемента И, а другой — к первым входам второго, третьего и четвертого элементов И, первый и второй выходы источника управляющих импульсов соединены соответственно со 20 вторыми входами второго и третьего элементов И, третий и четвертый выходы источника управления импульсов подключены соответственно ко вторым входам первого и четвертого элементов И и входу счетного триггера, выходы первого, второго и четвертого элементов

И соединены соответственно с управляющим входом регистра числа, входом дополнительного формирователя опросного ЗО тока и одним из входов блока индикации, третий вход третьего элемента И подключен к выходу блока сравнения, другие входы которого соединены со входами устройства, а выход третьего элемента И подключен к другому входу блока индикации (1).

Однако это устройство, обеспечивая контроль ошибок типа прошивка в одно окно, не позволяет обнаруживать ряд технологических дефектов блоков памяти, вызванных замыканиями между отдельными проводами в жгуте, что снижает область применения устройства.

Цель изобретения — расширение области применения устройства за счет обеспечения возможности выявления коротких замыканий между информационными проводами.

Поставленная цель достигается тем, что устройство содержит дополнительный счетный триггер и коммутатор, то ковый вход которого подключен к выхо ду дополнительного формирователя опросного тока, управляющий вход — к первому выходу дополнительного счетного триггера, второй выход которого подсоединен к одним из входов первого элемента И и блока индикации, вход дополнительного счетного триггера со801105, единен с первым выходом счетного триггера, выход блока сравнения подключен к одному иэ входов источника управляющих импульсов.

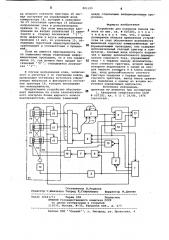

На чертеже представлена функциональная схема устройства.

Устройство содержит источник. 1 управляющих импульсов, счетный триггер 2, формирователь 3 опросного тока, регистр 4 числа, блок 5 сравнения, первый элемент И б, дополнительный формирователь 7.опросного тока, второй 8, третий 9 и четвертый 10 элементы И. Входы и выходы устройства подключены к выходам и входам контролируемого блока 11 памяти. Блок 11 содержит -дешифратор 12, информационные про-13 вода 13, прошивающие разрядные.сердечники 14, однополярные усилители 15 считывания, дополнительный провод 16.В состав устройства для контроля блоков памяти входят также блок 17 индикации, о коммутатор 18 и дополнительный счетный триггер 19.

Один выход триггера 2 подключен к первому входу элемента И б, а другойк первым входам элементов И 8-10, пер-25 вый и второй выходы источника 1 управляющих импульсов соединены соответственно со вторыми. входами элементов И

8 и 9, третий и четвертый выходы источника 1 управляющих импульсов под- ЗО ключены соответственно ко вторым входам элементов И б и х0, выходы элементов И б, 8 и 10 соединены соответственно с управляющим входом регистра

4 числа, входом формирователя 7 и од- gg ним из входов блока 1? индикации, третий вход элемента И 9 подключен к вы-: ходу блока 5 сравнения, другие входы которого соединены со входами устройства, а выход элемента И 9 подключен к другому входу блока 17 индикации.

Токовыи вход коммутатора 18 подключен к выходу дополнительного формирователя 7 опросного тока, управляющий вход — к первому выходу счетного триггера- 19, второй выход которого подсое-45 динен к третьему входу первого элемента И б и к третьему входу блока 17 индикации. Вход счетного триггера 19 соединен с первым выходом счет-:. ного триггера 2. Выход блока 5 50 сравнения подключен ко входу основного источника 1 управляющих: импульсов.

Устройствб работает следующим образом.

С одного иэ выходов . счетного триг- гера 2 подается импульс разрешения на прохождение через элемент И 8 импульсов с первого выхода источника 1 управляющих импульсов, а также через элементы И 9 и 10 соответственно импульсов со второго и третьего выходов бО источника l управляющих импульсов, только в четном цикле работы устройства.

С другого выхода счетного триггера

2 на элемент И б подается импульс раз 65 решения на прохождение импульсов с третьего выхода источника 1 управляющих импульсов только в нечетном цикле.

Импульсы с первого выхода источника 1 управляющих импульсов поступают на вход .формирователя 3, который в каждом цикле формирует ток через дешифратор 12 в информационных проводах

13 блока 11 памяти, прошивающих разрядные сердечники 14 в различных направлениях. Наведенная от этого тока в разрядных обмотках сердечников 14

ЭДС сигналов подается на входы однополярных усилителей 15 считывания, на стробируемые входы которых поступает в каждом цикле строб со второго выхода источника 1 управляющих импульсов.

С выходов усилителей 15 в момент строба считанный информационный код поразрядно подается на входы регистра 4 числа, предварительно в первом и далее в каждом нечетном цикле установленного в 0 импульсом с выхода элемента И б, и на один из входов блока 5 сравнения.

С выхода регистра 4 числа записанный в первом цикле информационный код снимается на другие входы блока 5 сравнения.

Во втором цикле работы устройства с выхода элемента И 8 импульсы подаются на вход дополнительного формирователя 7, который в четные циклы в дополнительном проводе lб, прошивающем все разрядные сердечники в направленин, соответствующем логическому 0, формирует ток .такой полярности, что импульсное напряжение считанных сигналов, формируемых с помощью основного формирователя 3, сдвигается в сторону логического 0 . При этом в тех разрядах, где прошивка выполнена в одно окно, т.е. с ошибкой, сигнал на входе усилителей 15 считывания соответствует логическому 0, тогда как в предыдущем цикле без дополнительного кода, сигнал соответствует логической l . Считанный при этом во время прихода. строба с выходов усилителей 15 код, не изменяя записанной в первом цикле информации в регистре 4 числа, поступает на один из входов блока 5 сравнения кодов.

При появлении в элементе И 9 разрешающего импульса, на вход блока 17 индикации,предварительно установленного в 0 импульсом с выхода элемента

И 10,проходит сигнал сравнения информационного кода, записанного в регистр

4 числа в первом цикле,с кодом, снятым с однополярных усилителей 15 во втором цикле, Несравнение кодов высвечивается блоком 17 индикации,что соответствует ошибке типа, прошивка в одно окно . Сигнал с первого выхода счетного триггера 2 поступает на вход второго счетного триггера 19. С первого выхо801105

Составитель В.Рудаков

Редактор С.Шевченко Техред Е.Гаврилешко Корректор М,демчик

Заказ 10441/71 Тираж 656 Подписное.

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 да второго счетного триггера 19 сигнал поступает на управляющий вход коммутатора 18, который в зависимос ти от состояния триггера 19 изменяет направление тока в дополнительном . приводе 16. При этом импульсное напряжение на входах усилителей 15 сдви- гается в сторону логической 1 .

Если дефектов в жгуте информационных проводов 13 нет, то усилители 15, обладающие пороговой характеристикой, срабатывают в соответствии с прошивкой.

Если же имеется неисправность типа замыкания между отдельными информационными проводами, то в тех сердечниках 14, где должен быть прошит ло- !5 гический 0, считывается логическая 1 .

В случае несравнения кода, записанного в регистре 4 со считанным кодом, щ происходит остановка источника управляющих импульсов и фиксируется состояние триггера 19, которое показывает тип неисправности.

Предлагаемое устройство обеспечивает выявление на этапе технологического контроля. более широкого класса неисправностей, например замыканий между отдельными информационными про водами.

I формула изобретения

Устройство для контроля блоков памяти по авт. св; М 607283, о т л ич а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности выявления коротких эамыканиймежду информационными проводами",- оно содержит дополнительный счетный триггер и коммутатор, токовый вход которого подключен к выходу дополнительного формирователя опросного тока, управляющий вход - к первому выходу дополнительного счетного триггера, второй выход которого подсоединен к одним из входов первого элемента И и блока индикации, вход дополнительного счетного триггера соединен с первым выходом счетного триггера, выход блока сравнения подключен к одному из входов источника управляющих импульсов.

Источники информации, принятые во,внимание при экспертизе

1. Авторское свидетельство СССР

Р 607283, кл. G 11 С 29/00, 1976 (прототип) .