Регулируемое устройство для усилениясигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ

Союз Советских

Социал>к тнчеекнх

Республик

Опубликовано 30.01.81. Бюллетень М 4

Дата опубликования описания 31,01.81 (5l)M. Кл.

Н 03 G 3/20

ГовудврвтввнныИ квинтет

СССР во делан изобретений и открытий (53) УДК621.396..666 (088.8) Е. ll. Романов, А. П, Голубков, A. П. Лукощкин, В. А. Фомченко, В. Я. Бухалко и В. О. Тихонов (72) Авторы изобретения Ъ"

Ленинградский институт авиационного приборостроения (7() Заявитель (54) РЕГУЛИРУЕМОЕ УСТРОЙСТВО ДЛЯ УСИЛЕНИЯ

СИГНАЛОВ

Изобретение относится к радиотехнике и может использоваться в приемных акустических, гидролокационных, сейсмических устр ойствах.

Известно регулируемое устройство для усиления сигналов, содержащее поспедова5 тельно соединенные усипительные каскады, выход каждого из которых подкпючен к соответствующему входу многоканального блока сравнения, и блок автоматической регулировки усипения (АРУ} $1$.

Однако данное устройство имеет низкую скорость изменении коэффициента усипения и не имеет переменного коэффициента сжатия динамического диапазона ам15 плитуд входных сигналов.

Бель изобретения — увеличение скорости изменения коэффициента усиления и получение переменного коэффициента сжатия динамического диапазона амплитуд входных сигналов.

Указанная цель достигается тем, что в регулируемое устройство для усиления сигналов, содержащее последовательно соединенные усилительные каскады, выход каждого из которых. подключен к соответствующему входу многоканального блока сравнения, и блок автоматической регулировки усиления (АРУ), между выходом многоканального блока сравнения и входом блока АРУ включены последовательно логический анализатор уровня, первый весовой сумматор и бпок коммутации, а между выходом логического анализатора уровня и другим входом блока коммутации включен второй весовой сумматор, а управляющие входы обоих весовых сумматоров подключены к выходу блока АРУ.

Логический анализатор уровня содержит элементы совпадения, число которых равно числу каскадов многокаскадного усилителя, первые входы которых подключены к соответствующим единичным выходам многоканального блока сравнения, вторые входы второго и последующих we ментов совпадения объединены и подключены к первому нулевому выходу много3 ЯЭ канального блока сравнения, третьи входы третьего и последующих элементов совпадения также объединены и подключены ко второму нулевому выходу и т.д. до последнего входа последнего элемента совпадения, подключенного к предпоследнему нулевому выходу многоканального блока сравнения, а выходами логического анализатора уровня являются выходы элементов совпадения. Логический ана» лизатор уровня также содержит логические элементы совпадения с инвертированием, первые входы которых подключены к соответствующим единичным выходам многоканального блока сравнения, а выходы каждого логического элемента совпадения с инвертированием соединены с соответствующими входами всех последующих логических элементов совпадения с инвертированием. Кроме того, блок коммутации содержит две линии задержки и два ключевых каскада, входы которых подключены к соответствующим выходам линий задержки, а выходы объединены, s также последовательно соединенные дифференцируюшую цепь и триггер, выходы . которого подключены к управляющим входам соответствующих ключевых каскадов, а вход дифференцирующей цепи соединен со входом одной иэ пиний задержки.

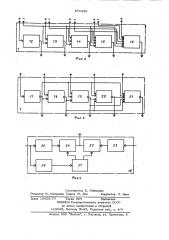

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 и 3 — схемы логического анализатора уровня, 1-й и 2-й варианты выполнения; на фиг. 4 - схема блока коммутации.

Регулируемое устройство для усиления сигналов содержит усилительные каскады 1-5, многоканальный блок 6 сравнения, логический анализатор 7 уровня,пер-, вый и второй весовые сумматоры 8 и 9, блок 10 коммутации и блок 11 автомати ческой регулировки.усиления (АРУ), причем логический анализатор 7 уровня со» стоит иэ элементов 12-16 совпадения или логических элементов 17-21 совпадения с инвертированием, а блок 10 коммутации состоит из двух линий задержки 22 и 23, двух ключевых каскадов 24 и 25, дифференцирующей цепи 26 и триггера 27.

Устройство работает следующим образом.

Входной сигнал поступает на последовательно соединенные усилительные каскады 1-8, где усиливается и ограничивается, если имеет достаточно большую ам плитуду. С выхода каждого усилительного каскада 1-5 сигналы с разной амплитудой поступают на детекторы многоканаль-

50 ного блока 6 сравнения. Продетектированный сигнал усиливается до величины, равной величине напряжения источника литания. Этим сигналом управляются элементы 12-16 совпадения логического анализатора 7 уровня. Сигнал на выходе любого элемента 12-16 совпадения появляется только тогда, когда на всех его входах находится высокий уровень напряжения. Поэтому в любой момент времени сигнал позволяется на выходе только одного элемента совпадения, соединенного с тем каналом многоканального блока 6 сравнения, который расположен ближе ко входу многокаскадного усилителя и на котором сигнал превышает порог. Во втором варианте схемы логического анализатора 7 уровня выходной сигнал каждого логического элемента 17-21 поступает на входы последующих логических элементов 17-21 и закрывает их. далее сигнал поступает на два идентичных весовых сумматора 8 и 9, регулируемых блоком 11 АРУ.

С обоих весовых сумматоров 8 и 9 сигналы поступают на блок 10 коммутации, который пропускает на выход либо сигнал от первого весового сумматора 8, либо от второго весового сумматора 9 в зависимости от характера входного напряжения многокаскадного усилителя: если оно нарастает, т.е. его производная во времени положительна, то к выходу подключается первый весовой сумматор 8, если производная отрицательна, т.е, сигнал спадает, то подключается второй ве- совой сумматор 9.

Чтобы при подаче на вход последовательно сильного и слабого сигнала коэффициент усиления многоканального усилителя успел восстановиться к приходу слабого сигнала, благодаря блоку 10 коммутации задний фронт сильного сигнала воспроизводится меньшей величины, чем он есть на самом деле. Кроме того, можно менять крутизну заднего фронта и сделать

его черезвычайно крутым. Все это способствует скоростному изменению коэффициента усиления усилителя в целом и обеспечивает переменный коэффициент сжатия амплитуд входных сигналов, который оказывается зависящим не только от мгновенного значения огибающей входных сигналов, но и от направления ее изменения.

Формула изобретения

1. Регулируемое устройство для уси-

I пения сигналов, содержащее последователь5 8012 но соединенные усилительные каскады, выход каждого из которых подключен к соответствующему входу многоканального блока сравнения, и блок автоматической ре гупировки усиления (АРУ), о т л и ч аю щ е е с я тем, что, с целью увеличения скорости изменения коэффициента усипения и получения переменного коэффициента сжатия динамического диапазона амплитуд входных сигналов, между выходом lO многоканального блока сравнения и входом блока АРУ вкпючеиы последовательно логический анализатор уровня, первый весовой сумматор и блок коммутации, а между выходом логического анализатора 1% уровня и другим входом блока коммутации включен второй весовой сумматор, а управляющие входы обоих весовых сумматоров подключены к выходу блока АРУ.

2. Устройство по п. 1, о т и и ч а - щ ю щ е е с я тем, что логический анапиэатор уровня содержит элементы совпадения, число которых равно числу каскадов многокаскадного усилителя, первые входы которых подключены к соответствующим единичным выходам многоканапьного блока сравнения, вторые входы второго и последующих элементов совпадения объединены и подключены к первому нулевому выходу многоканального блока срав- Зо нения, третьи входы третьего и поспедующих элементов совпадения также объединены и подключены ко второму нулевому выходу и т.д. до последнего входа последнего элемента совпадения, подключенного к предпоследнему нулевому выходу много» канапьного блока сравнения, а выходами логического анализатора уровня. явпяются выходы элементов совпадения.

3. Устройство по п. 1 о т л и ч аю щ е е с я тем, что логический . анализатор уровня содержит логические элементы совпадения с инвертированием, первые входы которых подключены к соотг ветствующим единичным выходам многока напьного блока сравнения, а выходы каж дого логического элемента совпадения с инвертированием соединены с соответстчу. ющими входами всех последующих логичео кнх элементов совпадения с инвертированием.

4. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок коммутации содержит две линии задержки и два кпючевых каскада, входы которых подключены к соответствующим выходам линий задержки, а выходы объединены, а также последовательно соединенные днфференцирующую цепь и триггер, выходы которого подключены к управпяющим входам соответствующих ключевых каскадов, а вход днфференцируквцей цепи соединен со входом одной иэ линий задержки.

Источники информации, принятые во внимание при экспертизе

1. Патент США % 3813609, кл. Н 03 Q 3/22, 1974 (прототип).

8 11229

Составитель Е. Любимова

Редактор М. Митровка Техред М. Лоя Корректор Л. Иван

Заказ 10455/77 Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фипиал ППП "Патент", г. Ужгород, ул. Проектная, 4