Делитель частоты следованияимпульсов c автоматически изменяющимсякоэффициентом деления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТИЛЬСТВУ

:б

Ф г (61) Дополнительное к авт, саид-ву (22) Заявлено 11.10.78 (21) 2672760/18-21 с присоединением заявки № (23) Приоритет—

Опубликовано 3Q0131. Бюллетень ¹ 4

Дата опубликования описания 01.0281 (51)М. Кл.3

Н 03 К 23/00

Государственный комитет

СССР по делам изобретений и открытии (53) УДК621. 374. .4 (088.8) с—

А, А. Шайков .. ЮЗ».:.:.

1

Институт технической кибернетики АН ВелоруССкОй ССР;,. (72) Автор изобретения (71) Заявитель (54 ) ДЕЛИТЕЛЪ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

С АВТОМАТИЧЕСКИ ИЭМЕНЯЮЩИМСЯ КОЭФФИЦИЕНТОМ

ДЕЛЕНИЯ

Изобретение относится к импульсной технике и автоматике и может быть использовано в управляющих устройствах чертежно-графических автоматов, в частности для разгона и торможения шаговых двигателей.

Известен делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления, содержащий двоичный делитель частоты, блок записи параллельного кода, реверсивный счетчик импульсов, дешифратор и два элемента И f1l.

Недостатком данного устройства asляется невозможность его применения для схем управления шаговыми двигателями при отработке последними количества шагов не кратных удвоенному значению максимального числа в ре" версивном счетчике, например в чертежно-графических автоматах.

Наиболее близок к изобретению по технической сущности делитель частоты с автоматически изменяющимся коэффициентом деления, содержащий двоичный делитель частоты, блок записи параллельного кода, реверсивный счетчик импульсов, вычитающий счетчик импульсов, два элемента И, блок сравнения, дешифратор, коммутатор. с двумя триггерами и двумя элемента ми И и кодовую шину, при этом выходы двух элементов H подключены к соот-. ветствующим входам реверсивного счетчика импульсов, первый выход которого (импульс переполнения реверсивного счетчика) подключен к четвертому входу коммутатора, а второй выход — к первому входу блока сравнения и через первый вход блока записи параллельного кода — к первому входу двоичного делителя частоты, второй вход которого подключен к входной шине, а выход — ко второму входу блока записи параллельного кода, к первым входам двух элементов И и к пер" вому входу вычитакщего счетчика импульсов, второй вход которого подключен к кодовой шине, а выход - ко второму входу блока сравнения и через дешифратор — ко второму входу коююутатора, первый вход которого подключен к входной шине, третий вход — к выходу блока сравнения, а выходы — ко вторым входам элементов И (2).

Недостаток данного устройства заключается в том, что изменение частогы на его выходе, соответствующее участкам увеличения и уменьшения частоты, происходит только по линейному

801253 закону, монотонно увеличиваясь и счетчика 3 в двоичный делитель 1,. уменьшаясь. Устройство не может функ- поступает на вход счетчика 4 и через ционировать при занесении в вычитаю- элемент 5 поступает на суммирующий щий счетчик нечетного двоичного кода, вход счетчика 3. Частота Рщ,„на выходе по абсолютной величине меньшего уд- двоичного делителя 1 остается постоянсенного значения максимального кода 5 ной до тех пор, пока не заполнятся еверсивного счетчика импульсов ° Кроме 1...К разряды счетчика 3. С приходом того, в данном делителе частоты вход- следующего импульса на "+" вход ная частота максимально может быть по- 1...К разряды счетчика 3 установятся делена на число, равное максималь- в "0", а (К+1) разряд — в "1" и в реному коду РевеРсивного счетчика, т.е. 10 зультате увеличится частота рн,ц,кократному числу н двоичной системе ис- торая останется постоянной до слечисления. Это ограничивает .сФеРУ при- дующего импульса переполнения 1...К менения такого делителя частоты. разрядов счетчика 3. Таким образом цель изобретения — расширение функ- частота Г,,будет ступенчато возрасциональных возможностей. тать по мере увеличения кода и счетПоставленная цель достигается тем, 13 чике 3 и установится максимальной что в делитель частоты следования им при равенстве значений кода в счетпульсов с автоматически изменяющимс чике 3 и числа в дешифраторе 14. коэффициентом деления, содержащий Если значение кода в счетчике 4 двоичный делитель частоты, первый больше удвоенного значения числа н вход которого подключен к входной шинЩ} дешифраторе 14, то сигнал с его выи первому входу коммутатора, второй хода после достижения равенства кода вход — к ныходу блока записи парал- счетчика 3 и числа н дешифраторе 14 лельного кода, а выход — к первым нхо устанавливает триггер 11 в единичное дам элементов И, входу блока записи состояние и снимает тем самым разрепараллельного кода и входу вычитаю yg шающий потенциал с нулевого выхода щего счетчика импульсов, разрядные триггера 11 на вход элемента 5, завходы которого подключены к кодовой прещая прохождение импульсов на сумшине, а выход — к входу дешифратора мирующий вход счетчика 3. С этого нуля и первому входу блока сравне- момента установившаяся максимальная ния, второй вход которого соединен частота импульсов Fesixc выхода двос разрядными выходами реверсивного ичного делителя 1 сохраняется до счетчика импульсов, а выход — со тех пор, пока код счетчика 4 не сраввторым входом коммутатора, третий няется с кодом н счетчике 3. После вход которого подключен к выходу де- сравнения кодов блок 7 выдает разрешифратора нуля, а выходы коммутато- шающий потенциал на элемент 12, имра — ко вторым входам элементов И, З пульс с выхода которого устанавливает выходы которых соединены со входами триггеры 10 и 11 в единичное состояреверсивного счетчика импульсов. вве- ние, в результате чего с единичного .ден дешифратор максимального кода, выхода триггера 10 поступает разревход которого соединен со вторым шающий потенциал на элемент б. Имвходом блока сравнения, а выход — с 49 пульсы с выхода двоичного делителя 1 четвертым входом коммутатора, при через элемент б начинают поступать на этом выходы старших разрядов ревер- вычитакнций вход счетчика 3 и уменьсивного счетчика импульсов соединены шать в нем значение кода, что привос разрядными входами блока записи дит соответственно к ступенчатому параллельного кода, а установочный 4 снижению выходной частоты F,дделивход первого разряда — с входом пер теля. ного разряда вычитающего счетчика им- Когда код в счетчике 4 станет пульсон. Рав ым нулю, дешифратор 8 подаст

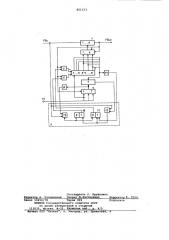

На чертеже представлено устройст- разрешающий потенциал на элемент 13 во, структурная электрическая схема. О для прохождения импульсов Гве на сброс

Схема содержит двоичный делитеЛь 1 триггеров 10 и 11 в нулевое частоты, блок 2 записи параллельного состояние и возвращения делитекода, реверсивный счетчик 3 импульсов ля частоты в исходное состояние.Для вь итающий счетчик 4 импульсов эле, выполнения следующего цикла работы мцнты 5 и б И, блок 7 сравнения. me устройства подается новый код по шишифратор 8 нуля, коммутатоР 9ю триг не 15 в счетчик 4 и одновременно знагеры 10 и 11 коммутатора элементы 12 .чение первого разряда этого кода на и 13 И коммутатора, дешифратор 14 установочный вход первого разряда максимального кода, кодовая шина 15. счетчика 3, что всегда создает четДелитель частоты следования ии ную разность между кодами в счетчипульсов работает следующим образом. фО ках 4 и 3 à выполнения условия

Импульсы с частотой Fa поступают сравнения кодов в блоке 7. на вход двоичного делителя 1. Импульс Если значение кода в счетчике 4 переполнения с в ода двоичного дели- меньше удвоенного значения числа ля 1 через блок 2 переписывает в дешифраторе 14, то частота импрямой код старших (м -1)...в РазРЯдов 4 Я пульсов Г с выхода двоичного де801253 лителя 1 увеличивается до такой величины, пока увеличивающееся значение кода счетчика 3 не станет равным уменьшающемуся значению кода счет.чика 4. После сравнения кодов блок 7 выдает разрешающий потенциал на элемент 12 для прохождения импульса входной частоты Гвк на установку триггеров 10 и 11 в единичное состояние.

Разрешающий потенциал с нулевого выхода триггера 11 снимается с элемен- © та 5, а разрешающий потенциал с единичного выхода триггера 10 подается на элемент 6. С этого момента счетчик 3 начинает работать на уменьшение кода в нем, тем самым ступенчато уменьшая частоту импульсов Гинкас выхо ъ да двоичного делителя 1.

Цикл работы делителя частоты заканчивается аналогично описанному выше при появлении нулевого значення кода в счетчике 4. 26

Частота на выходе двоичного делителя 1 равна во всех случаях

F вх их = 276=3. где m — общее число разрядов счетчика 3;

К вЂ” число младших 1... К разрядов счетчика 3;

М вЂ” число в старших (К+1)...m разрядах счетчика 3.

Данный делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления обеспечивает фу ц р с и нечетными кодами деление входной частоты на произвольное целое число в пределах разрядности реверсивного счетчика не только по линейному, но и по ступенчатому закону на участках увеличения и уменьшения выходной час-40 тоты.

Формула изобретения

Делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления, содержащий двоичный делитель частоты, первый вход которого подключен к входной шине и первому входу коммутатора, второй вход — к выходу блока записи параллельного кода, а выход — к первым входам элементов И, входу блока записи параллельного кода и входу вычитающего счетчика импульсов, разрядные входы которого подключены к кодовой шине, а выход — к входу дешифратора нуля и первому входу блока сравнения, второй вход которого соединен с разрядными выходами реверсивного счетчика импульсов, а выход — со вторым входом коммутатора, третий вход которого подключен к .выходу дешифратора нуля, а выходы коммутатора — ко вторым входам элементов И, выходы которых соединены со входами реверсивного счетчика импульсов, о т л и ч аю шийся тем, что, с целью расширения функциональных возможностей, него введен дешифратор максималь ного кода, вход которого соединен со вторым входом блока сравнения, а выход — с четвертью входом коммутатора, при этом выходы старших разрядов реверсивного счетчика импульсов соединены с разрядными входами блока записи параллельного кода, а установочный вход первого разряда - с входом первого разряда вычитающего счетчика импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 451199, кл. Н 03 К 23/00, 19.01.72.

2. Авторское свидетельство СССР . М 552704, кл. 8 23/00, 24.02.76.

801253

Заказ 10456/78 Тираж 999

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 москва, Ж-35, Раушская наб., д. 4 5

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель О. Кружилина

Ре акто А. Пчолинская Тех .Ж.Кастелевич Ко екто Н Стец