Делитель частоты с переменнымкоэффициентом деления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЖИТЕЛЬСТВУ

Союз Соаетскик

Социалистических республик

<п 801254 (61) Дополнительное к авт. свид-ву (51)М. Кл 3 (22) Заявлено 10 ° 01. 79(21) 2715799/18-21 с присоединением заявки Hо (23) Приоритет

Опубликовано 300181.Бюллетень МЗ 4

Н 03 К 23/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621.374 ° .44 (088.8 ) Дата опубликования описания 0102,81

А. А. Борисевич, А. A. Кулик, Б. И. Мака енк6;. й,: ф"..;.Ц ;.„Маслий

1," .. (72) Авторы изобретения (71) Заявитель (54 ) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ

ДЕЛЕНИЯ

Изобретение относится к .радио технике и может быть использовано в цифровых синтезаторах частоты приемно-передающей аппаратуры, В устрой-н ствах дискретной автоматики и вычислительной техники.

Известен делитель с переменным коэффициентом деления, содержащий несколько счетчиков с переменным коэффициентом деления и элементами совпадения на входе, триггеры коммутации, логические элементы И, ИЛИ и НЕ (1).

Однако известное устройство имеет сложный процесс установки требуемого коэффициента деления или задержку выходного сигнала, зависящую от коэффициента деления.

Известен также делитель частоты с переменным коэффициентом деления, содержащий счетчик с постоянным коэффициентом пересчета, первый счетчик с переменным коэффициентом пересчета с первой схемой установки, вхо-2н ды которых через элементы совпадения связаны с источником входного сигнала и с выходами триггера коммутации, а также триггер управления, иивертор, логические элементы И и ИЛИ, второй счетчик с переменным коэффициентом пересчета и со второй схемой установки 523.

Б известном делителе многоэлементная суммарная задержка выходного сиг. нала затягивает время переключения триггера коммутации в конце каждого цикла деления, в связи с чем неполностью используется быстродействие счетчиков и в результате чего известный делитель с н коэффициентом деления имеет пониженное быстродействие.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что-в делитель частоты с переменным коэффициентом деления, содержащий счетчики с постоянным н переменным коэффициентом счета, триггер коммутации, запоминающий триггер, инвертор, элементы ИЛИ и И, первые входы двух первых из которых подключены к входной шине, вторые входы — к выходам запоминающего триггера, а первый вход третьего элемента И соединен с единичным выходом триггера коммутации, введены арифметические устройства, дополнительный запоминающий триггер, дополнительные элементы ИЛИ и И и дополнительный инвертор, причем выход

801254 первого арифметического устройства подключен к третьим входам двух первых элементов И, к первому входу

:четвертого элемента И, к первому входу первого дополнительного элемента и через инвертор к первому входу торого дополнительного элемента И, выход второго арифметического устройства подключен к четвертым входам двух первых элементов И, к первому входу пятого элемента И, ко второму входу второго дополнительного элемен та И и через инвертор ко второму входу первого дополнительного элемента И

/ третьи входы дополнительных элементов И и второй вход третьего элемента И подключены к входной шине, выходы ; первого элемента И и первого дополнительного элемента И через элемент

ИЛИ подключены ко входу первого счетчика с переменным коэффициентом счета, выход которого соединен с нулевым 20 входом запоминающего триггера и с единичным входом дополнительного запоминающего триггера, выходы второго элемента И и второго дополнительного элемента И через последовательно соединенные дополнительный элемент ИЛИ и счетчик с постоянным коэффициентом счета подключены ко входу второго счетчика с переменным коэффициентом деления, выход которого подключен к единичному входу запоминающего триггера и к единичному входу триггера коммутации, нулевой вход которого подключен к выходу пятого элемента И, при этом нулевой вход дополнительного запоминающего триггера соединен с выходом четвертого элемента И, а единичный выход — с третьим входом третьего элемента И, выход которого подключен ко вторым входам четвертого и пятого элементов И. 40

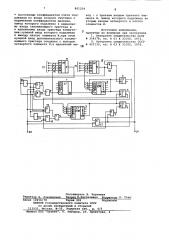

На чертеже представлен делитель частоты с переменным коэффициентом деления, структурная электрическая схема.

Устройство содержит счетчик 1 с 4 постоянным коэффициентом счета с логическим элементом 2 ИЛИ на входе, первый счетчик 3 с переменным коэффициентом счета с логическим эле" ментом 4 ИЛИ на входе, второй счетчик 5 с переменным коэффициентом счета, выход которого подключен к единичному входу триггера б коммутации, первый 7 и второй 8 запоминаз1цие триггеры, нулевые входы кото-, рых подключены соответственно к элементам 9 и 10 И, первое арифметическое устройство 11, информационные входы которого подключены к шинам 12 сигналов двойного кода коэффициен- - тов деления "единицы", второе ариф- Щ метическое устройство 13, информационные входы которого подключены к шинам 14 сигналов двоичного кода коэффициентов деления "десятки", элементы 15-19 И, каждый второй вход, которых подключен к шине 20 источнн ка входного сигнала, шину 21 выходного сигнала, инверторы 22 и 23.

Выход счетчика 1 подключен непосредственно к входу счетчика 5, выход которого подключен к единичным входам триггеров 6 и 8. Единичный выход триггера 8 подключен к первому входу элемента 17 И. Выход счетчика 3 подключен к нулевому входу триггера б и к единичному входу триггера 7, единичный выход которого подключен к третьему входу элемента 17 И, выход которого подключен к шине 21 и к перным входам элементов 9 и 10 И. Второй нход элемента И 9 подключен к выходу первого арифметического устройства 11 и к каждому третьему входу элементов 15, 16 и 19 И и к входу инвертора 23, выход которого подключен к первому входу элемента 18 И, выход последнего подключен к первому входу элемента 2 ИЛИ. Второй вход элемента 10 И подключен ко второму арифметическому устройству 13, к третьему входу элемента 18 И, к первому входу элемента 19 И, к третьему входу элемента 15 И и ко входу инвертора 22, выход которого подключен ко второму входу элемента 16 И, выход последнего подключен ко второму входу элемента ИЛИ 4. Единичный выход. триггера б подключен к четвертому входу элемента 19 И, выход которого подключен ко второму входу элемента 2

ИЛИ. Нулевой выход триггера б подключен к первому входу элемента 15 И, выход которого подключен к первому входу элемента 4 ИЛИ.

Устройство работает следующим образом.

Счетчик 1 имеет постоянный коэффициент счета N< = 10. Счетчики 3 и 5 имеют переменные коэффициенты счета соответственно и = 1-10 и N =1-10, которые устанавлйнаются с помощью сигналов двоичного кода на соответствующих шинах 14 и 12. 06а счетчика с переменным коэффициентом счета работают в режиме автономного сброса и перезаписи, установленного на шинах 14 и 12, а следовательно, и на информационных входах. общий коэффициент деления делителя определяется из выражения

N М1 МБ+ йз ОМ5 +N3 = йдвс+йеь где N c l 0Ng Мяд - йз .

Таким образом, последовательно включенные счетчики 1 и 5 обеспечивают получение слагаемого и,,а счетчик 3-получение слагаемого N в общем коэффициенте деления N. Поочередная работа счетчикон 1, 5 и 3 обеспечивается триггером б, первым арифметическим устройством 11 совместно с элементами 15 и 16 И, эле- ментом 4 ИЛИ, иннертором 22 и вторым арифметическим устройством 13 сонместно с элементами 18 и 19 И, 2 ИЛИ

801254 и инвертором 23. Арифметические устройства 11 и 13 обеспечивают выполнение операции, определяемой выражением

Ч=Х„.Х, Х Х4.

В случае, когда М = О, на обоих выходах арифметических устройств 11 и 13 появляется запрещающий сигнал, блокирующий элементы 15, 16, 18 и

19 И и сигнал со входа 20 не проходит на счетчики 1 и 3.

16

Если и = й, + и = О, то на выхо дах арифметических устройств 11 и

13 присутствует сигнал логической единицы (разрешающий сигнал). В этом случае, в зависимости от сигналов на выходах триггера 6, входной сигнал с шины 20 будет поступать либо на вход счетчика 1 через элементы

19 И и 2 ИЛИ, либо на вход счетчика

3 через элементы 15 И и 4 ИЛИ. Выходные сигналы счетчиков 3 и 5 ме- Щ няют состояние триггера 7 и одновременно переключают триггеры 7 и 8 в единичное состояние, при котором появляются разрешающие сигналы на втором и третьем входе элемента 17 И.

На этом первый цикл подсчета первого числа входных импульсов, равного й, оканчивается. В следующем цикле повто ряется поочередная работа счетчиков 1, 5 и 3. При этом каждый первый импульс серии цикла проходит через элемент 17 И на выходную шину 21 делителя и на элементы 9 и 10, которые возвращают триггеры 7 и 8 в исходное состояние.

В случае, когда и N qr.,а и д О, запрещающий сигнал с выхода арифметического устройства 11 блокирует элементы 15, 16 и 19 И, а элемент

9 И удерживает триггер 7 в единичном состоянии, подготавливая элемент 17 И 40 к прохождению входного импульса на выход делителя. Одновременно через инвертор 23 подается разрешающий сигнал на элемент 18 И, и входные им- пульсы IIocT IIèþT через элементы 18 И щ и 2 ИЛИ на вход счетчика.1, с выхода которого — на вход счетчика 5 и далее иа триггер 8. После прохождения числа импульсов, равного Npgg,триггер 8 опрокидывается в единичное состояние, и иа выходе элемента 17 И, а следовательно, на выходе 21 делителя, появляется выходной импульс, который является первым по счету в следующей серии подсчитываемых импульсов. Таким образом, триггер 8 ус- >5 танавливается в нулевое состояние, а счетчики 1 и 5 работают независимо от состояния выходов триггера 6, ибо элементы 15 и 19 И находятся в заблокированном состоянии. 60

В случае, когда N = и д Нас О, запрещающий сигнал с выхода арифметического устройства 13 блокирует элементы 18, 19 и 15 И и элемент 10 И который удерживает триггер 8 в еди- 65 ничком состоянии, подготавливая тем I сарж элемент 17 И к прохождению входного импульса на выход делителя.

Одновременно через инвертор 22 подается разрешающий сигнал на элемент

16 И, и входные импульсы через элементы 16 И и 4 ИЛИ поступают на вход счетчика 3, который подсчитывает число импульсов, равное N< и после окончания счета опрокидывает триггер 7 в единичное состояние. На выходе элемента 17 И, а следовательно, и на выходе 21 делителя, появляется выходной импульс, который устанавливает триггер 7 в исходное состояние, а счетчик 3 работает независимо от состояния выходов триггера 6, ибо элементы 15 и 19 И находятся в заблокированном состоянии.

Формула изобретения

Делитель частоты с переменным коэффициентом деления, содержащий счетчики с постоянным и переменным коэффициентом счета, триггер коммутации, запоминакщий триггер, инвертор, элементы ИЛИ и И, первые вхо, ды двух первых из которых подключе ны к входной шине, вторые входы .— к выходам запоминающего триггера, а первый вход третьего элемента И соединен с единичныа выходом триггера

,коммутации, отличающийся тем, что, с целью повышения быстродействия, з него введены арифметические устройства, дополнительный запоминающий триггер, дополнительные элементы ИЛИ и И и дополнительный инвертор, причем выход первого арифметического устройства подключен к третьим входаМ двух первых элементов И, к первому входу четвертого элемента И, к первому входу первого дополнительного элемента И и через инвертор к.первому входу второго дополнительного элемента И, выход второго арифметического устройства подключен к четвертым входам двух первых элементов И, к первому входу пятого элемента И, ко второму входу второго дополнительного элемента И и чере=инвертор ко второму входу первого дополнительного элемента И, третьи входы дополнительных элементов И и второй вход третьего элемента И подключены к входной шине, выходы первого элемента И и первого дополнительного элемента И через элемент ИЛИ подключены ко входу первого счетчика с переменным коэффициентом счета, выход которого соединен с нулевым входом запоминающего триггера и с единичным входом дОполнительного запоминающего триггера, выходы второго элемента И и второго дополнительного элемента И через последовательно соединенные допблнительный элемент ИЛИ и счетчик

801254

Составитель В. Черныаев

Редакто Л. Пчелинская Тех ед K.Кастелевич Ко кто Н. Стец

Заказ 10456/78 Тираж 999

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35 Раущская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Подписное

4- постоянным коэффициентом счета под

Ключены ко входу второго счетчика с переменным коэффициентом деления, выход которого подключен к единичному входу запоминающего триггера и к единичному входу триггера коммутации,нулевой вход которого подключен к выходу пятого элемента И,при этом нулевой вход дополнительного запоминающего триггера соединен с выходом четвертого элемента И,а единичный выход — с третьим входом третьего элемента И, выход которого подключен ко вторым входам четвертого и пятого элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство. СССР

М 354578, кл. Н 03 К 23/00, 1972.

2. Авторское свидетельство СССР

М 421132, кл. Н 03 К 23/00, 1974.