Делитель частоты на 44

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Ф +

„,,7 -" г г

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 26. 01. 79 (21) 2717856/18-21. (51)М. Кл.3

Н 03 К 23/02 с присоединением заявки М (23) Приоритет—

Государс1оенный комитет

СССР по делам изобретений н открытий

Опубликовано 30.01„8). Бюллетень.- Мо 4

Дата опубликования описания 010281 (53) УДК 621. 374. . 44 (088. 8) (72) Авторы изобретения

f .влюче н к Ьв" 1,-

В. А. Грехнев, В. Н. Гиленок и Н. П. П (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ HA 11

Изобретение относится к автоматике и вычислительной технике н может быть использовано для деления последовательности входных импульсов на 11

Известен делитель частоты, который содержит в каждом разряде триггер памяти и два коммутационных триггера (1f .

Однако устройство требует большого11) количества оборудования, что ведет к увеличению его габаритов, веса, потребляемой мощности. Кроме того, оно не осуществляет деление входной последовательности импульсов на 11.

Наиболее близким к предлагаемому является устройство, содержащее четыре разряда, каждый иэ которых состоит из триггера памяти и коммутационного триггера, а три первых разряда и из элемента И-НЕ, причем в первых двух разрядах единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный вы" ход которого соединен со входом эле-25 мента И-НЕ, а нулевой выход соединен с единичным входом триггера памяти, в третьем разряде нулевой выход триггера памяти соединен с единичным входом коммутационного триггера, а в четвертом разряде нулевой выход триггера памяти соединен с нулевым входом коммутационного триггера, нулевой выход коммутационного триггера второго разряда соединен с нулевыми входами триггера памяти и коммутационного триггера первого разряда и со входом элемента И-НЕ этого разряда, выход элемента И-НЕ третьего разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами коммутационных триггеров, триггеров памяти и со входами элементов И-HE

scex предыдущих разрядов, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом триггера памяти четвертого разряда, с нулевыки входами триггеров памяти и коммутационных триггеров всех младших разрядов и со входом элемента И-НЕ второго разряда, единичный выход коммутационного триггера четвертого разряда соединен с нулевыми входами всех триггеров делителя,выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда и со входом элемента И-НЕ третьего разряда, выход элемента И-HE второго разряда соединен с нулевым входом коммутационного триггера и со

801256 входом элемента И-НЕ третьего разряда, а тактовая шина подключена к нулевым входам коммутационных триггеров первого, второго и третьего разрядов, к единичному входу коммутациониого триггера четвертого разряда и

ko входу элемента И-НЕ второго разряда 2) .

Однако известное устройство выполнено на большом количестве оборудования и обладает низкой надежностью.

Цель изобретения — повышение надежности работы устройства.

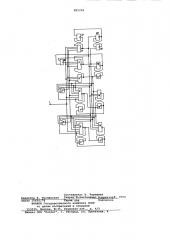

Поставленная цель достигается тем, что в делителе частоты на 11, содержащем четыре разряда, каждый из которых состоит из триггера памяти и коммутационного триггера, а три первых разряда и из элемента И-НЕ, выходы элементов И-HE первого и второго разрядов соединены с единичными вхотого разряда, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом коммутационного триггера первого разряда, а единичный выход коммутационного триггера четвертого разряда соединен со входами элементов И-HE первого, второго и третьего разрядов, На чертеже представлен делитель частоты на 11, функциональная схема.

Устройство содержит шину 1 тактового импульса, элементы 2-4 И-НЕ первого-третьего разрядов, элементы

5-12 И-НЕ попарно образующие коммутационные триггеры первого-.четвертого разрядов, элементы 13-20 И-НЕ, попарно образующие триггеры памяти этих же разрядов.

Устройство работает следующим образом.

В начале работы все триггеры памяти находятся в нулевом состоянии, 25

40 а тактовый сигнал, поступающий по шине 1, отсутствует равен логическому нулю . В этом случае на выходах элементов 2,3, 10, 12, 13, 15, 17 и 19 тактовый сигнал равен логическому нулю на выходах остальных элементов логической единице, поэтому с при45 ходом первого тактового импульса срабатывает только элемент 6 И-НЕ, устанавливая триггер памяти первого разряда в единичное состояние. После окончания действия тактового импфьса на выходе элемента 2 И-НЕ поя 4тяется логическая единица. С приходом следующего тактового импульса срабатывает элемент 8 И-НЕ, устанавливая триггер памяти второго разряда в единичное состояние, а триггер . памяти первого разряда — в нулевое

50 состояние. С приходом третьего такто- gp вого импульса снова срабатывает элемент 6 И-НЕ, устанавливая триггер памяти первого разряда в единичное состояние. По окончании действия тактового импульса на выходе элемента 2 дами коммутационного триггера четвер-- Щ

И-HE появляется логическая единица, а поскольку и триггер памяти второго разряда находится в единичном состоянии, то на выходе элементы 3 И-НЕ также логическая единица. Следова,тельно, с приходом четвертого тактового импульса сРабатывает элемент 4

И-НЕ, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов — в нулевое. Наличие связи с выхо.. дом элемента И-НЕ входов элементов

2,3,6 и 8 И-НЕ препятствует неправиль. ной работе делителя.

Аналогичным образом с приходом пятого тактового импульса триггер памяти первого Разряда устанавливается в единичное состояние, с приходом шестого тактового импульса он возвращается в нулевое состояние, а в единичное состояние устанавливается триггер второго разряда. После окончания действия шестого тактового импульса на выходе элемента 3 И-HE появляется сигнал, равный логической единице.

Поскольку на выходе элемента 10 И-НЕ появляется сигнал, равный логической единице, то с приходом седьмого тактового импульса срабатывает элемент 9

И-НЕ, устанавливая триггер памяти четвертого разряда в единичное состояние, а триггеры памяти остальных разрядов — в нулевое состояние. Далее счет продолжается аналогичным образом до тех пор, пока после прихода десятого тактового импульса в делителе не установится код 1011. Поскольку иа выходах элементов 1, 3 и 12 будут сигналы, равные логической единице, то с приходом одиннадцатого тактового импульса срабатывает элемент 11 И-НЕ, устанавливая делитель в исходное состояние.

Таким образом, в делителе осуществляется деление последовательности входных импульсов на 11, причем происходит следующая последовательность смены состояний.

0 0000 6 0110

1 0001 7 1000

2 0010 8 1001

3 0011 9 1010

4 0100 10 1011

5 0101 11 0000

Введение новых связей позволяет сократить количество оборудования, уменьшить габариты, вес, потребляемую мощность, повысить. надежность работы устройства.

Формула изобретения

Делитель частоты на 11, содержащий четыре разряда, каждый из которых состоит из триггера памяти и коммутационного триггера, а три первых разряда и иэ элемента И-НЕ, причем в первых двух разрядах единич80125б ный выход триггера памяти соединен с единичным входом коммутационного

1 риггера, единичный выход которого оединен со входом элемента И-НЕ, а нулевой выход соединен с единичнымвходом триггера памяти, в. третьем разряде нулевой выход триггера памяти соединен с единичным входом коммутационного триггера, а в четвертом разряде нулевой выход триггера памяти соединен с нулевым входом коммутационного триггера, нулевой выход коммутационного триггера второго разряда соединен с нулевыми входами триггера памяти и коммутационного триггера первого разряда и со входом элемента И-НЕ этого разряда, 1З выход элемента И-НЕ третьего разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами коммутационных триггеров, триггеров памяти и со входами элемеи- Щ тов И-НЕ всех предыдущих разрядов, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом триггера памяти четвертого разряда, с нулевыми входами триг-р геров памяти и коммутационных триггеров всех младших разрядов и со входом элемента И-НЕ второго:разряда, единичный выход коммутационного триг гера четвертого разряда оединен с нулевыми входами всех триггеров делителя, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго раз" ряда и со входом элемента И-НЕ третьего разряда, выход элемента И-НЕ второго разряда соединен с нулевым входом коммутационного триггера и со входом элемента И-HE третьего разряда, а тактовая шина подключена к нулевым входам коммутационных триггеров первого, второго и третьего разрядов, к единичному входу коммутационного триггера четвертого разряда и ко входу элемента И-НЕ второго раз" ряда, отличающийся тем, что, с целью повышения надежности работы устройства, выходы элементов

И-НЕ первого и второго разрядов соединены с единичными входами коммутационного триггера четвертого разряда, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом коммутационного триггера первого разряда, а единичный выход коммутационного триггера четвертого разряда соединен со входами элементов И-НЕ первого, второго и третьего разрядов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 444330, кл. Н 03 К 23/00, 1971

2. Авторское свидетельство СССР по заявке В 2528043, кл. Н 03 К 23/02, 1977.

801256

Составитель В. Чернышев ре акто Л, Пчолинская Техред З.Кастелевич Ко екто Н. Стец

3 акаэ 0 б Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва Ж-35 Ра ская наб. . 4 5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4