Устройство для обнаружения иисправления ошибок b кодовойкомбинации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву @ 540389 (22) Заявлено 050379 (21) 2732140/18-09 (51)М. КЛ.

Н 04 L 1/10 с присоединением заявки М (23) Приоритет

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 30.0131. Бюллетень Н9 4

Дата опубликования описания 300181 (53) УДК 621. 394. .14(088.8) (72) Автор изобретения

A. Л. Юфа (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ

ОШИБОК В КОДОВОЙ КОМБИНАЦИИ

Изобретение относится к технике связи и может использоваться для за" щиты от ошибок аппаратуры передачи .ранных.

По основному авт. св. 9 540389 известно устройство для обнаружения и исправления ошибок в кодовой комбинации, содержащее однопороговый и двухпороговый блоки, входы которых соединены с входом устройства, причем выход двухпорогового блока через счетчик подключен к управляющему

Ьходу первого ключа и через последовательно соединенные первый ключ и 15 блок формирования полиномов ошибок соединен с первым входом сумматора по модулю два, выход однопорогового блока через последовательно соединенные буферный и основной накопители — с 20 вторым входом сумматора по модулю два, выход которого подключен к информационному входу второго ключа, управляющий вход которого связан с выходом блока обнаружения ошибок, при этом выход сумматора по модулю два подключен к входу блока обнаружения ошибок, выход которого соединен с вторым входом блока формирования полиномов ошибок )1 J. 30

Однако известное устройство имеет, недостаточную помехоустойчивость и достоверность кодовых комбинаций во времени при значительных частотах передачи данных и при наличии полиноминальных ошибок.

Цель изобретения — повышение помехоустойчивости и достоверности кодовых комбинаций во времени.

Указанная цель достигается тем, что в устройство для обнаружения и исправления ошибок в кодовой комбинации, содержащее однопороговый и двухпороговый блоки, входы которых соединены с входом устройства, причем выход двухпорогового блока через счетчик подключен к управляющему входу первого ключа и через последовательно соединенные первый ключ и блок формирования IIoJIHHQMQB ошибок соединен с первым входом сумматора по модулю два, выход однопорогового блока через последовательно соединенные буферный и основной накопители — с вторым входом сумматора по модулю два, выход которого подключен к информационному входу второго ключа, управляющий вход которого связан с выходом блока обнаружения ошибок, при этом выход сумматора по модулю

801283 два подключен к входу блока обнаружения ошибок, выход которого соединен с вторым входом блока формирования полиномов ошибок, дополнительно введен блок обнаружения и восстановления синхронизирующих импульсов, выход которого подключен к дополнительным входам однопорогового и двухпорогового блоков, а вход блока обнаружения и восстановления синхронизирующих импульсов является вторым входом устройства.

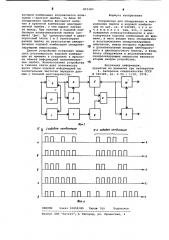

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства) на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит однопороговый i5 блок 1, двухпороговый блок 2, счетчик 3, первый ключ 4, блок 5 формирования полиномов ошибок, сумматор 6 по модулю два, буферный накопитель 7, основной накопитель 8, второй щ ключ 9, блок 10 обнаружения ошибок, блок 11 обнаружения и восстановления синхронизирующих импульсов.

Устройство для обнаружения и исправления ошибок в кодовой комбина25 ции работает следующим образом.

Принятая на входе устройства кодовая комбинация (фиг. 2а) одновременно поступает на входы однопорогового и двухпорогового блоков 1 и 2, Поступившие на второй вход уст- З® ройства синхронизирующие импульсы (фиг. 26) подаются на блок 11 обнаружения и восстановления синхронизирующих импульсов и проверяются им на отсутствие возможных сбоев. При наличии сбоев синхронизирующих импульсов в синхропачке (фиг. 2в) блок

11 обнаружения и восстановления синхронизирующих импульсов формирует отсутствующие синхронизирующие импульсы ф) и восстанавливает их на штатном месте во времени (фиг. 2г) . Принятая без ошибок или восстановленная синхросерия с выхода блока 11 обнаружения и восстановления синхронизирующих импульсов поступает для синхронизации принятой кодовой комбинации на рднопороговый и двухпороговый блоки 1 и 2.

С выхода однопорогового блока 1 засинхронизированная кодовая комбинация, состоящая из последовательности "0" и "1"; через буферный накопйтель 7 вводится в основной накопитель 8. В результате анализа каждого принимаемого элемента кодовой H комбинации на выходе двухпорогового блока 2 появляется сигнал "стирания" в том случае, если принятый элемент не может быть отождествлен ни с "1", ни с "0". Эти ненадежные элементы @д через открытый первый ключ 4 подаются,в блок 5 формирования полиномов ошибок и подсчитываются счетчиком 3.

Устройство рассчитано на исправление

t-кратных ошибок, поэтому емкость счетчика 3 равна t. При появлении

"стираний" в количестве r 0 t импульс переноса со счетчика 3 закрывает первый ключ 4, прекращая ввод "стираний" в блоке 5 формирования полиномов ошибок. После приема и элементов комбинации корректирующего кода последняя из основного накопителя 8 подается на вход сумматора б по модулю два, на другой вход которого одновременно поступает нулевой полином из блока 5 формирования полиномов ошибок.

С выхода сумматора б по модулю два элементы комбинации, соответствующие принятой кодовой комбинации, подаются на вход блока 10 обнаружения ошибок.

На выход устройства элементы не поступают, так как второй ключ 9 находится в закрытом состоянии. При необнаружении ошибок блок 10 обнаружения ошибок выдает сигнал в блок 5 формирования полиномов ошибок и на управляющий вход второго ключа 9, открывая его. Блок 5 формирования по:Э линомов ошибок, восприняв сигнал необнаружения ошибки, в очередном цикле формирует полином ошибки, аналогичный предыдущему, т.е. нулевой.

Кодовая комбинация второй раз поступает из основного накопителя 8 через сумматор б по модулю два и открытый второй ключ 9 непосредственно на выход устройства. Если при первом цикле проверки блок 10 обнаружения ошибок обнаруживает ошибку, то комбинация из основного накопителя 8 выдается на проверку второй раз и при этом блок 5 формирования полиномов ошибок формирует полином однократной ошибки, который на сумматоре б по модулю два осуществляет первое исправление принятой комбинации.

Исправленная комбинация проверяется блоком 10 обнаружения ошибок, который при необнаружении ошибки выдает сигнал в блок 5 формирования полиномов ошибок и на управляющий вход второго ключа 9, открывая его. Блок 5 формирования полиномов ошибок формирует полином однократной ошибки, аналогичный предыдущему, и исправленная комбинация в очередном цикле через открытый второй ключ 9 поступает на выход устройства. Если блок 10 обнаружения ошибок обнаружит ошибку в первом варианте исправленной комбинации, то проверки продолжаются. При этом блэк 5 формирования полиномов ошибок формирует очередной ,полином ошибки и т.д. до первого необнаружения ошибки в каком-либо из вариантов исправленной комбинации. В этом случае исправленная комбинация в очередном цикле работы через открытый второй ключ 9 поступает на вход устройства. Если ошибка будет обнаружена во всех циклах йроверки, включая и последний, при

801283

Формула изобретения

Pvc,1 и-р «одобряя комбинация

ВНИИПИ Заказ 10459/80 Тираж 709 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 котором комбинация исправляется поли-. номом t-кратной ошибки, то блок 10 обнаружения ошибок фиксирует наличие в принятой комбинации неисправленной ошибки, о чем выдает сигнал на выход. При наличии в кодовой комбинации полиноминальной ошибки (помехи) (фиг. 2д) однопороговый и двухпороговый блоки 1 и 2 селектируют данную ошибку по результатам синхронизации кодовой комбинации синхронизируюцими импульсами.

Данное устройство позволяет повысить достоверность кодовой комбинации во времени и устранить в процессе обмена информацией полиноминальные ошибки. Использование устройства в технике связи дает возможность вести обмен кодовой информацией на значительных частотах передачи данных с большой достоверностью.

Устройство для обнаружения и исп- .равления ошибок в кодовой комбинации по авт. св. Р 540389, о т л ич а ю ш е е с я тем, что, с целью повышения помехоустойчивости и достоверности кодовых комбинаций во времени, в него введен блок обнаружения и восстановления синхронизирующих импульсов, выход которого подключен О к дополнительным входам однопорогового и двухпорогового блоков, а вход, блока обнаружения и восстановления .синхронизирукацих импульсов является вторым входом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 540389, кл. Н 04 L 1/10, 1974.