Устройство для контроля и коррек-ции распределителя

Иллюстрации

Показать всеРеферат

Саюз Советских

Социалистических

Ресну

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОУСКОМУ Сви ИТИЛЬСТВУ

<щ 801291 (61) Дополнительное к авт. свид-ву— (22) Заявлено 050379 (2l) 2733577/18-09 с присоединением заявки йо (23) Приоритет

Опубликовано 300181.Бюллетень Н9 4

Дата опубликования описания 3ц0181 р1)м. к.

Н 04 L 11/08

ГоеударствЕнный комитет

СССР по .делам изобретений и открытий (53) УДК 621. 394.

;65(088.8} (72) Авторы изобретения

Н.П. Сергеев, В.Н. Попов, В.A. Лазарев и С.Н. Катков

Пензенский политехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И КОРРЕКЦИИ

РАСПРЕДЕЛИТЕЛЯ

Изобретение относится к автоматй-ческим системам обработки информации и может использоваться для сбора и передачи информации с датчиков.

Известно устройство для контроля и коррекции распределителя, содержащее основной элемент И и счетчик, выходы которого подключены к входам декодера, выход которого подключен к входу дифференцирующего блока и первому. входу блока совпадения, второй вход и выход которого соединены, соответственно, с выходом источника опорного сигнала и первым входом основного элемента ИЛИ, к второму входу которого подключен выход элемента ЗАПРЕТ (1).

Однако данное устройство обладает малым быстродействием.

Цель изобретения — повышение быст- 2О родействия.

Указанная цель достигается тем, что в устройство для контроля и кор рекции распределителя, содержащее ,основной элемент И и счетчик, выхо ды которого подключены к входам декодера, выход которого подключен к входу дифференцирующего блока и первому входу блока совпадения,. второй вход и выход которого соединены, соответственно, с выходом источника опорного сигнала и первым входом основного элемента ИЛИ, к второму входу которого подключен выход элемента ЗАПРЕТ, введены дополнительный элемент И, блок управления, дополнительный элемент ИЛИ и последовательно соединенные элемент задержки и ключ, второй вход и выход которого соединены, соответственно, с выходом декодера и входом источника опорного сигнала, при этом выход основного элемента И подключен к первому входу дополнительного элемента ИЛИ, второй вход которого соединен с входом элемента задержки и первыМ входом элемента ЗАПРЕТ, к второму входу которого подключен выход элемента задержки, а выходы дифферен цирующего блока, блока совпадения и основного элемента ИЛИ соединены с входами блока управления, выходы которого подключены к первым входам основного и дополнительного элементов И, вторые входы которых соединены с выходом элемента ЗАПРЕТ, а третьи входы обьединены, причем выход дополнительнога элемента ИЛИ подключен к первому входу счетчика, 801291 второй вход которого соединен с выходом дополнительного элемента И.

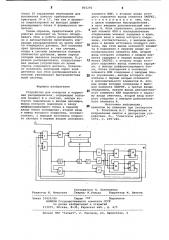

Яа чертеже изображена структурная электрическая схема устройства для контроля и коррекции распределителя.

У тройство содержит основной элемент 1 И, счетчик 2, декодер 3, диф5 ференцирующий блок 4, блок 5 совпа цения, источник 6 опорного сигнала, основной элемент 7 ИЛИ, элемент 8 ЗАПРЕТ, а также дополнительный элемент 9 И, блок 10 управления, дополнительный элемент 11 ИЛИ, элемент

12 задержки и ключ 13. При этом блок

10 управления содержит элементы 14 и 15 И и триггеры 16 и 17.

Устройство для контроля и коррек- !5 ции распределителя работает следующим образом.

В исходном состоянии триггеры 16 и 17 блока 10 управления сброшены в 20 состояние "0". При этом основной элемент 1 И и дополнительный элемент9 И, а также элементы 14 и 15 И блока 10 управления блокируются сигналами с прямых выходов триггеров 16 и 17. В момент прихода импульса частоты F содержимое счетчика 2 увеличивается на единицу. Одновременно уровень напряжения на выходе декодера 3 увеличивается на величину ЬП

Для исключения ложного срабатывания устройства в моменты поступления импульсов частоты F устройство содержит схему блокировки, состоящую .из элемента 12 задержки и элемента 8 ЗАПРЕТ. Время задержки, обеспечиваемое элементом 12 задержки, равно наибольшеМУ времени переходного процесса в счетчике 2. Элемент 8 ЗАПРЕТ включается передним фронтом импульса частоты Fo, а выключается задним 40 фронтом импульса на выходе элемента

12 задержки. Сигнал с выхода элемента 8 ЗАПРЕТ закрывает основной элемент 1 И и дополнительный элемент 9 И, а через основной элемент 4

7 ИЛИ удерживает триггеры 16 и 17 блока 10 управления в исходном состоянии.

Таким образом, переходные процессы счетчика 2 и декодера 3 не нару- р шают работы устройства. К моменту формирования сигнала на выходе элеь ента 12 задержки переходные процессы в счетчике 2 заканчиваются, и на выходе декодера 3 устанавливается новое значение напряжения. Сигналом с элемента 12 задержки включается ключ

13. При этом источник 6 опорного сигнала (в качестве которого может быть взято аналоговое запоминающее ,устройство) запоминает уровень напря- 60 жения, устанавливающийся на выходе декодера 3. В момент окончания импульса на выходе элемента 12 задержки источник 6 опорного сигнала отключается от декодера 3, а элемент Я

8 ЗАПРЕТ устанавливается в исходное состояние.

При сбое счетчика 2 коррекция осуществляется следующим образом.

Предположим, что содержимое счетчика 2 увеличивается. Декодер 3 выдает новое значение напряжения. При этом срабатывает блок 5 совпадения и на его выходе формируется сигнал рассогласования, который подается на входы элементов 14 и 15 И блока 10 управления. На вторые входы элементов 14 и 15 И подаются разрешающие сигналы с инверсных выходов триггеров 16 и 17. Так как напряжением на выходе декодера 3 получается положительное приращение, то появляется сйгнал на первом выходе дифференцирующего блока 4, который проходит через открытый элемент 15 И и опрокидывает триггер 17. Сигнал низкого уровня с инверсного выхода триггера 17 блокирует элемент 14 И, а сигнал высокого уровня с его прямого выхода открывает дополнительный элемент:9 И. Импульсы высокой частоты f начинают поступать через дополнительный элемент 9 И на вычитающий вход счетчика 2. Вычитание продолжается до момента, когда нап ряжение на выходе декодера 3 не становится равным напряжению с выхода источника 6 опорного сигнала.

При равенстве сигналов на выходе блока 5 совпадения вырабатывается сигнал, который через основной элемент

7 ИЛИ устанавливает триггер 17 блока 10 управления в исходное состояние. Дополнительный элемент 9 И закрывается, а код в счетчике 2 равен коду, который был в нем до сбоя.

Таким образом, коррекция произведена.

При уменьшении содержимого,счетчика 2 процесс коррекции происходит аналогичным образом. Сигнал рассогласования с выхода блока 5 совпадения открывает элементы 14 и 15 И, а дифференцирующий блок 4, выделяя отрицательное приращение напряжения на выходе декодера 3, вырабатывает импульс на его втором выходе, который через элемент 14 И поступает на установочный вход триггера 16. Тригrep 16 опрокидывается. Сигнал низкого уровня блокирует основной элемент

1 И. Импульс высокой частоты f через основной элемент 1 И и дополнительный элемент 11 ИЛИ поступает на вход сложения счетчика 2. Код счетчика 2 начинает возрастать до момента равенства сигналов на входе блока 5 совпадения. В момент равенства сигнал, формируемый на выходе блока 5 совпадения, через основной элемент 7 ИЛИ устанавливает триггер

16 в исходное состояние, после чего устройство вновь подготовлено к работе. Блокировка элементов 14 и 15 И

801291

Формула изобретения

Составитель Н. Пантелеева

Редактор М. Митровка Техред М.Рейвес Корректор М. Вигула

Заказ 10459/80 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 блока 10 управления необходима для йсключения ложного срабатывания триггеров 16 и 17, так как в процессе корректировки на выходах дифференцирующего блока 4 формируются импульсы.

Таким образом, предлагаемое устройство позволяет не только обнаруживать сбои в работе распределителя, но и автоматически производить Кор- рекцию распределителя во время опроса очередного датчика. Это особенно ярко проявляется в тех случаях, когда в систему включается большое количество датчиков, время опроса которых является значительным. К .ррекция распределителя, осуществляемая данным" устройством во время опроса очередного датчика, позволяет исключать повторный опрос всех датчиков при сбое распределителя и поэтому увеличивает быстродействие всей системы.

Устройство для контроля и коррекции распределителя, содержащее основной элемент И и счетчик, выходы которого подключены к входам декодера, выход которого подключен к входу дифференцирующего блока и первому входу блока совпадения, второй вход и выход которого соединены, соответственно, с выходом источника опорного сигнала и первым входом основного

Fg элемента ИЛИ, к второму входу которого подключен выход элемента ЗАПРЕТ, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены дополнительный элемент И, блок управления, дополнительный элемент ИЛИ и последовательно соединенные элемент задержки и ключ, второй вход и выход которого соединены, соответственно, с выходом декодера и входом источника опорного сиг нала, при этом выход основного элемента И подключен к первому входу дополнительного элемента ИЛИ, второй вход которого соединен с входом элемента задержки и первым входом эле15 мента ЗАПРЕТ, к второму входу которого подключен выход элемента задержки., а выходы дифференцирующего блока, блока совпадения -и основного элемента ИЛИ соединены с входами блоЯ ка управления, выходы которого подключены к первым входам основного и дополнительного элементов И, вторые входы которых соединены с выходом элемента ЗАПРЕТ, а третьи входы объединены, причем выход дополнительного элемента ИЛИ подключен к перво му входу счетчика, второй вход которого соединен с выходом дополнительного элемента И.

Источники информации, принятые во внимание при экспертизе

1. Толстяков В.С. Обнаружение и исправление ошибок в дискретных устройствах. M., "Советское радио", 1972, с. 239-240.