Устройство для регенерации синхроим-пульсов полей

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик («)801308

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное н авт. свид-ву (22) Заявлено 020479 (2! ) 2749218/18-09 (51)М. Кл.

Н 04 К 5/04 с присоединением заявки N9 .(23) Приоритет

Государственный комитет

СССР но делам изобретений н открытий

Опубликовано 30,0181 Бюллетень No 4

{53) УДК 621.397 (088.8) Дата опубликования описания 300181 (72) Автор изобретения у5

E.Í.Äèêàðeâ (71) Заявитель (54) УСТРОЙСТВО РЕГЕНЕРАЦИИ СИНХРОИМПУЛЬСОВ

ПОЛЕЙ

Изобретение относится к радио-. технике и может использоваться в приемниках совмещенного телевизион .ного сигнала и синхрогенераторах.

Известно устройство регенерации синхроимпульсов полей, состоящее из последовательно соединенных селектора кадровых синхроимпульсов, блока фазирования, счетчика и формирователя импульсов (1 .

Однако известное устройство недостаточно помехоустойчиво, так как не имеет средств защиты от появления ложных и искаженных импульсов.

Цель изобретения — повышение по- 15 мехоустойчивости путем устранения ложных и искаженных импульсов в режиме быстрого фазирования.

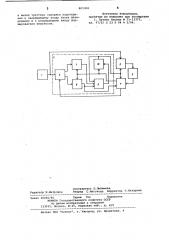

Укаэанная цель достигается тем, что в устройство введен анализатор 20 синхронизма, содержащий коммутатор, неинвертирующий и инвертирующий элементы памяти, триггер задержки и блок совпадения, при этом первый сравнивающий вход коммутатора подключен к выходу селектора кадровых синхроимпульсов, второй сравнивающий вход — к выходу формирователя импульсов, первый и второй выходы коммутатора подключены, соответственно, ЗО к информационным входам неинвертирующего и инвертирующего элементов памяти, выходы которых, а также выход триггера задержки подключены ко входам блока совпадения, выходом соединенного .с информационным входом триггера задержки, причем обнуляющие входы каждого элемента памяти и тактовый вход триггера задержки подключены к тактовому выходу формирователя импульсов, выход инвертирующего элемента памяти подключен к запрещающему входу формирователя импульсов, а выход триггера задержки подсоединен к запрещающему входу блока фазирования и к разрешающему входу формирователя импульсов., На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство регенерации синхроимлульсов полей содержит селектор 1 кадровых синхроимпульсов, блок 2 фазирования, счетчик 3, формирователь.

4 импульсов, анализатор 5 синхронизма, содержзщМй коммутатор б, неинвертирующий и инвертирующий элементы

7 и 8 памяти, блок 9 совпадения н триггер 10 задержки.

80130Å

Формула изобретения

Устройство работает следующим образом.

Действующий на выходе селектора

1 импульс установки, соответствующий моменту появления кадрового синхроимпульса входного телевизионного сиг- 5 нала, поступает на первый сравнивающий вход анализатора 5 и вход блока

2. Йри наличии нулевого сигнала на запрещающем входе блока 2 импульс установки фиксирует такое состояние, 10 счетчика 3, при котором импульс, вырабатываемый формирователем 4 на втором сравнивающем входе анализатора 5, занимает ту же временную позицию в цикле работы счетчика 3, что и )5 импульс установки. Таким образом, достигается быстрое совпадение по фазе между входным телевизионным сигналом и регенерированными импуль. сами частоты полей, которые вырабатываются формирователем 4.

Формирователь 4 наряду с обычными входами, которые подключены к разрядам счетчика 3, имеет дополнительный разрешающий вход. При подаче на этот вход нулевого сигнала запрещается формирование импульсов частоты полей на соответствующих выходах формирователя 4. На тактовом выходе формирователя 4, соединенном с такто- ЗО вым входом анализатора 5, импульс, соответствующий началу цикла работы счетчика 3, вырабатывается независимо от состояния сигнала на разрешающем входе формирователя 4. Этот им- 35 пульс является тактовым для анализатора 5, и только при появлении его происходит изменение сигнала на запрещающем входе блока 2 и разрешающем входе формирователя 4.

Таким образом достигается согласованное изменение сигнала на всех входах формирователя 4, что исключает воэможность возникновения каких- ф либо ложных импульсов в момент изменения сигнала на разрешающем входе.

При этом в каждом цикле работы счетчика 3, охватывающем интервал времени между двумя соседними тактовыми у импульсами, имеются только две возможности, соответствующие определенному уровню сигнала на разрешающем входе формирователя 4 и соединенном с ним запрещающем входе блока 2.

Если в данном .цикле работы счетчика

3 этот сигнал имеет единичный уровень, то блок 2 блокируется, импульсы установки не поступают на счетчик 3 и возможность появления ложных и искаженных импульсов из-за наруше- Я ния последовательности переключения разрядов счетчика 3 исключается.

Если же сигнал на разрешающем входе формирователя 4 имеет нулевой уровень, то происходит перефазировка

Г счетчика 3, однако ложные и искажен-, ные импульсы, которые могут позникнуть вследствие нарушения последовательности срабатывания разрядов счетчика 3, устраняются благодаря действию на разрешающем входе формирователя 4 нулевого сигнала, который блокирует соответствующие выходы формирователя 4.

В первом из. рассматриваемых случаев устройство работает в режиме формирования, а во втором — в режиме фазирования. Перевод устройства из одного режима в другой производится анализатором 5, который в каждом цикле работы счетчика 3 оценивает временное положение импульсов установки. С этой целью в каждом цикле с помощью коммутатора б производится распределение импульсов установки селектора 1 на неинвертирующий и инвертирующий элементы 7 и 8 памяти, причем если импульс установки совпадает по времени с импульсом на втором сравнивающем входе анализатора

5, то он попадает на инвертирующий элемент 8 памяти, если же такого совпадения нет, то импульс установки подается на неинвертирующий элемент

7 памяти.

Устройство регенерации синхроимпульсов полей, состоящее из последовательно соединенных селектора кадровых синхроимпульсов, блока фазирования, счетчика и формирователя импульсов,, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости путем устранения ложных и искаженных импульсов в режиме быстрого фазирования, в него введен анализатор синхронизма, содержащий коммутатор, неинвертирующий и инвертирующий элементы памяти, три"гер задер>кки и блок совпадения, при ,этом первый сравнивающий вход коммутатора подключен к выходу селектора кадровых синхроимпульсов, второй сравнивающий вход — к выходу формирователя импульсов, первый и второй выходы коммутатора подключены, соответственно, к информационным входам неинвертирующего и инвертирующего элементов памяти, выходы которых, а также выход триггера задержки подключены ко входам блока совпадения, выходом соединенного с информационным входом триггера задержки, причем обнуляющие входы каждого элемента памяти и тактовый вход триггера задержки подключены к тактовому выходу формирователя импульсов, выход инвертирующего элемента памяти подключен к запрещающему входу формирователя импульсов, 801308

Составитель Е.Любимова

Техред .С.Мигунова Корректор Г.Назарова

Редактор М.Митровка

Заказ 10460/81 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Óæãîðoä, ул. Проектная, 4 а выход триггера задержки подсоединен к запрещающему входу блока фаэирования и к разрешающему входу формирователя импульсов.

Источники информации, принятые во внимание при экспертиэе

1. Патент Японии Р 51-13373, кл. 97/5/ С 23 Н 04 М 5/04.