Запоминающее устройство с замещениемдефектных ячеек

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социвлистических

Республик

803009

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (51)М. Кл. (22) Заявлено 26. 01. 78 (21) 2573193/18-24 с присоединением заявки Мо (23) Приоритет

Опубликовано 070281, Бюллетень й9 5

Дата опубликования описания 07. 02. 81

G 11 С 11/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681 ° 327. 66 (088.8) (В.Я. Контарев, В.Я. Литуев, A.A. /Мйслоу4

Ю.В. Храмов и Ю.H. Щетинин (72) Авторы изобретения

Московский ордена Ленина а иацио им. Серго Орджоникидзе (71) Заявитель (54) ЗАПОМИНАК(ЦЕЕ УСТРОЙСТВО С ЗАМЕ ЦЕНИЕМ

ДЕФЕКТНЫХ ЯЧЕЕК

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах различного класса.

Известны оперативные и постоянные запоминающие устройства (Зу) с замещением дефектных ячеек (1) (2j.

Одно из известных ЗУ (1) реализовано в двух вариантах. B одном

10 варианте приведен а быстродействующая схема восстановления информации.

Время восстановления в ней не зависит от количества дефектов и общего числа разрядов в слове. Однако сложность таких схем возрастает с количеством дефектов не пропорционально, а по логарифмическому закону. Причем с возникновением новых дефектов в процессе анормального функционирования в блоках памяти информация не мо- 2и жет быть восстановлена в связи с тем, что структурная схема блока восстановления разрабатывается под конкретные известные дефекты и не может быть применена для другой вновь возникшей конфигурации отказов. Поэтому такие схемы применимы только на стадии разработки устройств с дефектными ячейками и неприменимы в ненадежных Зу. ЗО

В другом варианте ЗУ разработана медленно действующая схема восстановления информации при относительно минимальной сложности.

Наиболее близким техническим решением к изобретению является ЗУ, содержащее блоки памяти, один из которых подключен к регистру отказов, другой через реверсивный регистр сдвига — к основным элементам ИЛИ и блок управления, подключенный к генератору импульсов и блоку индикации (21 .

К недостаткам устройства относятся недостаточно высокая надежность и медленное время восстановления информации вследствие использования блоков линий задержек с задержкой в каждом разряде на

Ц=иС где n — номер разряда от 1 до и;

n — общее число разрядов в слове; (су — время одного сдвига.

Если п = 30, сл. = 0 05 мксек. то время, необходимое для сдвига вправо или влево, равно 1,5 мксек. Естественно, что такая .задержка при приеме и выдаче информации может быть допу80 3009 стима только в ЗУ с малым быстродей-. ствием.

Целью изобретения является повышение надежности.и быстродействия устройства.

Поставленная цель достигается тем, что ЗУ, содержащее блоки памяти, один из которых подключен к регистру отказов, другой через реверсквный регистр сдвига — к основным элементам ИЛИ, блок управления, подключенный к генератору импульсов и блоку индикации, введены дополнительные элементы ИЛИ и блоки приоритета, первые входы которых соединены с соответствующими выходами блока управления, вторые — с входом блока индикации и одним из выходов регистра отказов, а третьи — с другими выходами регистра отказов, выходы блоков приоритета подключены к входам основных и дополнительных элементов

ИЛИ. Выходы дополнительных элементов ИЛИ соединены с соответствующим входом регистра отказов.

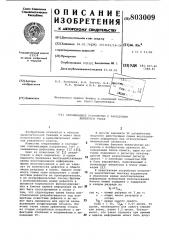

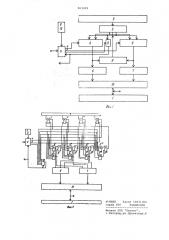

На фиг. 1 дана структурная схема ЗУ;на фиг. 2 — подробная схема

Зу на 4 разряда.

ЗУ содержит блоки памяти 1,2, регистр отказов 3, блоки приоритета

4,5, осуществляющие соответственно приоритетный сдвиг вправо для поразрядного сдвига прк записи к приоритетный сдвиг влево для поразрядного сдвига при считынанки, основные элементы 6,7 ИЛИ и дополнительный элемент 8 ИЛИ, блок индикации 9,реверсквный регистр сдвига (PPC) 10,блок управления 11 и генератор 12 импульсов.

ЗУ работает в режимах записи и считывания информации.

25

Режим записи информации. Вначале записываемое число фиксируется в

РРС 10, по установленному адресу считывается код отказов иэ блока памяти 2 и заносится в регистр отказов 3, а в блоке памяти 1 соответ- 4 ствующая адресу числовая линейка обнуляется. Затем в соответствии с кодом отказов блок приоритета 4 осуществляет сдвиг информационного кода по исправным разрядам в PPC 10 с 50 помощью генератора 12. По окончании сдвига блок 5 выдает сигнал об окончании сдвига, и число заносится н блок памяти 1. Блок приоритета 4 работает так, что управляющие сигналЫ сдвига, следующие с генератора 12 через блок управления, 11 поступают параллельно на все разряды блока 4, но сдвиг осущестнлятся н соответствии с приоритетом от старших разрядов к младшим,.причем количество тактов 60 сдвига определяется числом дефектов.

Режим считывания информации. По заданному адресу считываются информа ционный код из блока памяти 1 и код отказон из блока памяти 2. Код отка- 65 зов поступает в регистр отказов и блок приоритета 5. В соотнетствии с кодом отказов сдвигается информационный код влево по частям в зависимости от приоритетов отказов так же как и в режиме записи, но с приоритетом от младших разрядов к старшим. При этом число тактов сдвига равно числу дефектов. По окончании процесса свертки блок индикации

9 выдает сигнал об окончании свертки и число из PPC передается но ннешние блоки. Таким образом, как в процессе считывания, так и в процессе записи число тактов сдвига строго соответствует числу дефектов, что позволяет значительно повысить быстродействие ЗУ. В этом случае время задержки

) ) ) где и;, — число дефектных разрядов.

Ec))H и 30 и> 5, 9 — 0 05 мксек, то Г„= 0 25 мксек.

Отсюда видно, что при н аличии 5 дефектов н 30-разрядном слове выигрыш во времени увеличится в

6 раз. При уменьшении дефектов этот выигрыш будет увеличиваться, а прк увеличении — уменьшаться. Кроме того, возникновение дефектов в процессе функционирования приводит только к увеличению задержкк восстановления, а наличие блока сигнализации окончания сдвигов позволяет упорядочить поток приема-выдачи кнформацкк с дополнительным выкгрышем во времени.

Блоки приоритета состоят из нентклей 4 -4, Число входов вентилей увеличивается вправо пропорционально месту, занимаемому каждым конкретным разрядом в числовой линейке.

Так, третий вентиль 4 имеет 4 входа, из которых 3 входа соответствуют месту (третий), а четвертый управляющий. Блок приоритетного сдвига влево состоит из вентилей

5 -5 " ° Число входов вентилей увеличивается влево и определяется так же как в предыдущем случае. Блок индикации (сигнализации окончания сдвига)

9 выполнен на многовходоном элементе И.

При записи информации управляющая частота через блок управления с генератора 12 поступает на вход шины

"а", а при считывании — на вход "б".

В режиме записи работает блок приоритетного сдвига вправо, а при считывании — блок приоритетного сдвига влево.

Допустим, что н режиме записи посл: выведения кода отказов из блока памяти 2 триггеры 3 и 3 регистра отказов устанавлинаются в нулевое состояние. Это свидетельствует î том, что первый и третий разряды информационного кода дефектны. Вентиль 4 открывается, а вентили 4 и 4 закры803009 ваются сигналом с единичного выход триггера 3 . Первый импульс, посту/ пивший на шину "а" с генератора 12 через блок управления проходит только через вентиль 4. В результате информационный код PPC сдвигается на один разряд вправо, а триггер 3 устанавливается в единичное состояние через элемент 8 ИЛИ. Вентиль 4 закрывается сигналом с нулевого выхода триггера 3, а вентиль 4" открывается единичными выходами триг!

1 И геров 3 и 3 и нулевым выходом триггера 3 регистра отказов. Второй импульс, поступивший на вход "а" с генератора, проходит только через венр тиль 4 . В результате часть информационного кода, начиная с третьего разряда, сдвигается PPC вправо один !

И разряд, а триггер 3 через элемент

8 ИЛИ устанавливается в "единичное" состояние. Все вентили 4 -4 " з акры- 20 ваются, а. следующий импульс, поступая на шину "а" проходит только блок индикации 9, так как на других входах этого блока устанавливаются положительные потенциалы, поступающие с 5 единичных плеч триггеров регистра отказов 3..

Сигнал с выхода блока 9 проходит на вход блока управления и во внешние блоки ЗУ. В результате импульсы с генератора 12 на вход "а" не проходят, и число, рассредоточенное по исправным разрядам, записывается из PPC в блок памяти 1.

В режиме считывания осуществляется обратный процесс свертки числа при наличии кода отказов в регистре отказов 3. В этом случае приоритет устанавливается от младших разрядов к старшим. Разряды информационного кода сдвигаются по частям влево в за- 40 висимости от кода отказов так же, как и в режиме записи, причем уг равляющая частота с генератора 12 проходит через блок управления 11 на шину "б".

Формула изобретения

Запоминающее устройство с замещением дефектных ячеек, содержащее блоки памяти, один из которых под-. ключен к регистру отказов, другой через реверсивный регистр сдвига к основным элементам ИЛИ, блок управления, подключенный к генератору импульсов и блоку индикации, о т л ич а ю щ е е с я тем, что, с целью повышения надежности и быстродействия устройства, оно содержит дополнительные элементы ИЛИ и блоки приоритета, первые входы которых соединены с соответствующими выходами блока управления, вторые — с входом блока индикации и одним из выходов регистра отказов, а третьи — с другими выходами регистра отказов,выходы блоков приоритета подключены к вх >дам основных и дополнительных элементов ИЛИ, выходы дополнительных элементов ИЛИ соединены с соответствующим входом регистра отказов °

Источники информации, принятые во внимание при экспертизе

1. Надежная работа БИС вЂ” ЗУ с относительно большим числом дефектных элементов. И. Нilberg, "Еlekгroni—

sche Rechen anlagen." 1969 Bol 11, 9 6 5 321-329.

2. Р.вторское свидетельство СССР

9 515159, кл. 6 11 С 11/00, 15.01.75 (прототип).