Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнапистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

<1>803010

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву р )м. кл. (22) Заявлено 23.10.78 (23) 2687688/18-24 с присоединением заявки ¹ (23) Приоритет

G 11 С 11/00

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 0702.81. Бюллетень Н9 5

Дата опубликования описания 07. 02. 81 (53) УДК 681. 327. 6 (088. 8) (72) Авторы изобретения

Н.Н. Журавский, П.Г. Таран и Д.С. Тростян цкий

1,, Киевский ордена Трудового Красного Знамен завод вычислительных и управляющих машин и Киевский научно-исследовательский и конструкторский институт периферийного рудоааКи8 (73) Заявители (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и автоматике и может быть использовано в запоминающих устройствах.

Известны запоминающие устройства, выходные элементы которых в каждом разряде всех чисел объединены и через элемент согласования, например резистор, подключены к шине питания (11 . Повышение быстродействия в известных устройствах связано не только с увеличением потребляемой мощности и с установкой более мощных резисторов, но и с необходимостью применения более мощных выходных каскадов накопителей, способных коммутировать большой ток нагрузки и ток разряда паразиткой емкости разрядной шины.

Наиболее близким техническим решением к данному является запоминающее устройство, содержащее накопители памяти, дешифратор номера накопителя, шину разрешения выдачи и выходные разрядные шины (2). Недостатком известного запоминающего устройства является большая потребляемая мощность и относительно низкое быстродействие.

Цельч изобретения является уменьшение потребляемой мощности и повышение быстродействия устройства.

5 Достигается это тем, что в запоминающем устройстве, содержащем накопители, входы которых соединены с соответствующими адресными шинами и с шиной управления выдачей информации, а выходы с соответствующими разрядными шинами, дешифратор номера накопителя, выходы которого соединены с соответствующими входами накопителей, управляемые ключи, согласующие элементы, включенные между шиной питания и разрядными шинами и шунтированные соответствующими управляемыми ключами, входы управляемых ключей подключены к шине управления выдачей информации.

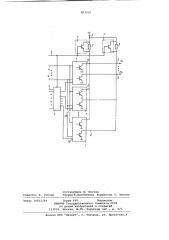

На чертеже дано запоминающее устройство (простейший случай),когда разрядность запоминакицего устройства совпадает с разрядностью накопителя.

23 ЗаПоминающее устройство содержит накопители 1, дешифратор 2 номера накопителя, согласующие элементы— (разрядные резисторы) 3, адресные шины 4, шину управления 5, выходные разрядные шины 6 и управляемые клю803010

40 чи 7. Шина управления 5 соединена с входом дешифратора 2 номера накопителя и с управляющими входами ключей 7, два других вывода каждого ключа 7 подключены параллельно разрядным резисторам 3. Ключи 7 установлены в каждом разряде устройства.

Выходы 8 одноименных разрядов накопителей 1 объединены и подключены к выходным разрядным шинам б и к первым выводам разрядных резисторов 3, другие выводы которых подключены к шине 9 питания. Адресные входы накопителей 1 соединены с адресными шинами 4, с которыми соединены также адресные входы дешифратора 2. Выходы дешифратора 2 соединены с входами 10 накопителей.

По адресным шинам 4 поступает код адреса. Старшие разряды адреса, поступающие на дешифратор 2, а также отрицательный импульс на шине 20 управления 5 обеспечивают появление отрицательного импульса на одном из выходов дешифратора 2. При этом срабатывает один из накопителей 1, соединенный по входу 10 с возбужденным выходом дешифратора 2. Выдача информации на выходные разрядные шины 6 осуществляется во время действия отрицательного импульса на шине 5 управления, этим же сигналом запираются ключи 7. Если в разряде читается "1", то выходной транзистор накопителя 1 заперт, на выходной разрядной шине б сохраняется высокий уровень, который установился на ней до начат,а обращения к запоминающему устройству. Если в разряде читается "0", то выходной транзистор накопителя 1 открыт,через резистор 3 течет ток, а íà соответствующей выходной разрядной шине 6 устанавливается низкий уровень. Резистор 3 может быть выбран достаточно большой величины (он должен обеспечить уровень логической. "1" на входах подключаемых к раз- 4 рядной шине б элементов, принимающих информацию из запоминающих устройств

После окончания отрицательного сигнала на шине управления 5 на всех выходах дешифратора 2 устанавливаются высокие уровни, открываются все ключи 7 и начинают закрываться открытые выходные транзисторы накопителей

1 (в разрядах, в которых читались

"0"). Постоянная времени выходной разрядной шины б существенно уменьшается благодаря тому, что сопротивление открытого ключа 7 намного меньше, чем сопротивление резистора

3. Поэтому высокий уровень на выходной разрядной шине б устанавливается за значительно меньший промежуток времени, чем в прототипе. Таким образом, в описанном устройстве повышение быстродействия достигается при одновременном уменьшении потребляемой мощности.

Формула изобретения

Запоминающее устройство, содержащее накопители, входы которых соединены с соответствующими адресными шинами, а выходы с соответствующими разрядными шинами, дешифратор номера накопителя, входы которого соединены с соответствующими адресными шинами и с шиной управления выдачей информации, выходы с соответствующими входами накопителей, управляемые ключи, согласующие элементы, включенные между шиной питания и разрядными шинами и шунтированные соответствующими управляемыми ключами, о т л и ч а ю щ е ес я тем, что, с целью снижения потребляемой мощности и повышения быстродействия устройства, входы управляемых ключей подключены к шине управления выдачей информации.

Источники информации, принятые во внимание при экспертизе

1. Брик Е.A. "Техника ПЗУ".

M. "Сов.радио", 1973, с. 36.

2. Сборник "Микроэлектроника и полупроводниковые приборы". М., "Сов.радио", вып.1, 1976 с. 50-58 (прототип).

803010

Тираж 656 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 10631/64

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Составитель В. Костин

Редактор Е. Гончар Техред Ж.Кастелевич Корректор С. Шекмар