Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

О П И С А Н H Е (ii) 803112

ИЗО6РЕТЕН ИЯ

Союз Советскик

Социалистическик

Республик

Ф г

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.! 1.78 (21) 2683657/18-09 с присоединением заявки №вЂ”! (i)

Н 04 L 7/02

Государстеенный комитет (23) Приоритет— ао делам изобретений и открытий

Опубликовано 07.02.81. Бюллетень № 5

Дата опубликования описания 17.02.81 (53) УДК 621.394. .662.2 (088.8) (72) Авторы изобретения

А. E. Красковский и Е.

Ленинградский ордена Ленина инсти железнодорожного транспорта им (71) Заявитель (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к радиотехнике и может использоваться в аппаратуре передачи данных, в частности в регенераторах радиоканала.

Известно устройство тактовой синхронизации, содержащее последовательно соединенные опорный генератор, первый блок управления, блок дискретной автоподстройки, блок тсреднения и астатическое звено регулирования, выход которого подключен к входам блоков выделения чередующихся и нечередующихся импульсов, причем второй выход опорного генератора подключен к другому входу астатического звена регулирования, другой выход которого подключен ко второму входу первого блока управления, третий вход которого соединен с другим выходом блока усреднения, второй вход которого соединен с первым выходом анализатора и первым входом второго блока управления, первый выход которого через элемент

ИЛИ подключен к другому входу блока дис- 20 кретной автоподстройки, выход которого подключен к входу формирователя зоны, выход которого подключен к первому входу анализатора и второму входу второго блока управления, второй выход которого подключен к другому входу элемента ИЛИ, при этом выход выделителя фронтов подключен ко второму входу анализатора и к третьему входу второго блока управления, а его входы соединены соответственно с третьим выходом опорного генератора и выходом блока дискретной автоподстройки (1).

Однако известное устройство имеет низкую точность.

Цель изобретения — повышение точности.

Для этого в устройство тактовой синхронизации, содержащее последовательно соединенные опорный генератор, первый блок управления, блок дискретной автоподстройки, блок усреднения и астатическое звено регулирования, выход которого подключен к входам блоков выделения чередующихся и нечередующихся импульсов, причем второй выход опорного генератора подключен к другому входу астатического звена регулирования, другой выход которого подключен ко второму входу первого блока управления, третий вход которого соединен с другим выходом блока усреднения, второй вход

803112 которого соединен с первым выходом анализатора и входом второго блока управления, первый выход которого через элемент ИЛИ подключен к другому входу блока дискретной автоподстройки, выход которого подключен к входу формирователя зоны, выход которого подключен к первому входу анализатора и второму входу второго блока управления, второй выход которого подключен к другому входу элемента ИЛИ, при этом выход выделителя фронтов подключен к второму входу анализатора и третьему входу второго блока управления, а его входы соединены соответственно с третьим выходом опорного генератора и выходом блока дискретной автоподстройки, введены первый, второй интеграторы и блок распознавания, причем выходы блоков выделения чередующихся и нечередующихся импульсов через первый интегратор подключены к четвертому входу второго блока управления, а второй выход выделителя фронтов через блок распознавания — к пятому входу второго

3 ю н

20 блока управления, причем выход формирователя зоны подключен к второму входу блока распознавания, выход которого подключен к шестому входу второго блока управления и через второй интегратор — к 2 третьему входу анализатора, второй выход которого подключен к другому входу второго интегратора.

При этом блок распознавания выполнен в виде элементов И, ИЛИ, счетчиков и триггеров, причем выход первого элемента Зо

И через последовательно соединенные первый, второй счетчики и триггер подключен к входу второго элемента И, а выход третьего элемента И через третий счетчик подключен к входу элемента ИЛИ, другой вход которого соединен с выходом второго счетчика, причем выход четвертого счетчика подключен к вторым входам первого, второго, третьего счетчиков и другому входу второго элемента И, при этом выход первого счетчика подключен к другому входу триг- 40 гера, причем входы первого и третьего элементов И и выходы второго элемента И и элемента ИЛИ являются соответственно входами и выходами блока распознавания.

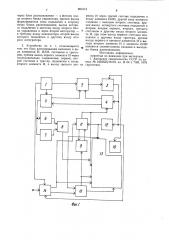

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 — вариант выполнения блока распознавания.

Устройство тактовой синхронизации содержит опорный генератор 1, первый блок 2 управления, блок 3 дискретной автоподстрой- ы ки, блок 4 усреднения, астатическое звено 5 регулирования, блок 6 выделения чередующихся импульсов, блок 7 выделения нечередующихся импульсов, первый и второй интеграторы 8 и 9 соответственно, элемент

ИЛИ 10, анализатор 11, формирователь 12 зоны, второй блок 13 управления, выделитель 14 фронтов, блок 15 распознавания, блок 15, состоящий из (см. фиг. 2) перво\ го, второго, третьего элементов И 16, 17, 18 соответственно, первого, второго, третьего, четвертого счетчиков 19, 20, 21 и 22 соответственно, элемента ИЛИ 23 и триггера 24.

Устройство работает следующим образом.

В выделителе 14 фронтов осуществляется дискретизация временного положения фронтов входного сигнала, для чего на один из входов выделителя фронтов поступает сигнал с выхода опорного генератора 1.

Выделенные фронты попадают на вход блоков 15 и 13.

Если на вход устройства тактовой синхронизации (УТС) поступает шум или сильнозашумленный полезный сигнал, то блок

15 формирует сигнал на отключение с помощью второго блока управления 13 цепи фазовой подстройки, Если на вход УТС поступает полезный сигнал, то блок 15 формирует сигнал на включение второго блока

13 управления цепи подстройки.

Выделенные фронты входного сигнала поступают на вход блока 3 дискретной автоподстройки опорного генератора 1 косвенным способом. Подстройку осуществляют с помощью второго блока 2 управления, на вход которого через блок 4 усреднения поступает сигнал с выхода блока 3.

Астатическое звено 5 регулирования выполняет операцию компенсации расстройки частоты генератора 1 относительно частоты входного сигнала. Для этого на вход астатического звена 5 поступает сигнал с выхода опорного генератора 1, а также с выхода блока 4 усреднения. Компенсацию расстройки осуществляет первый блок 2 управления.

В синхронном режиме работы формирователь 12 и второй блок 13 управления осуществляют селекцию фронтов входного сигнала по величине временных искажений.

Критерием наступления синхронизма служит результат интегрирования числа импульсов в первом интеграторе 8, на вход которого поступают чередующиеся и нечередующиеся импульсы с блоков 6 и 7. При этом сигнал с выхода формирователя 12 поступает на второй блок 13 управления, в результате чего этот блок начинает выполнять операцию селекции фронтов. Одновременно второй блок 13 управления разрывает прямую цепь (без временной зоны) прохождения фронтов на вход блока 3. Эта цепь является действующей только при переходных процессах, т. е. во время установления состояния синхронизма.

Признаком отсутствия состояния синхронизма является результат интегрирования числа импульсов, попадающих за пределы временной зоны, при условии, что на вход

УТС поступает информационный сигнал.

При этом сигнал на выходе блока 15, который осуществляет установку «0» второго интегратора 9, отсутствует. Следова803112 тельно, интегратор 9 будет заполняться и формировать сигнал отсутствия состояния синхронизма. Сигнал с выхода анализатора 11 включает малый коэффициент усреднения в блоке 4. При этом УТС переходит в режим быстрого поиска состояния синхронизма.

На фиг. 2 приведена схема блока 15 распознавания. Схема работает следующим образом.

Сигналы с выхода формирователя 12 зоны поступают на элементы 16 и 18. Одновре о менно на другие входы этих же элементов подаются импульсы фронтов входного сигнала с выделителя 14 фронтов. Так как на один из входов элемента И 16 подаются импульсы зоны с прямого выхода формирова-

Счетчик 22 определяет объем выработки числа фронтов, поступающих в блок, т. е. каждый раз при заполнении емкости счет- п чика 22 импульсами фронтов, на выходе счетчика 22 появляется сигнал обнуления счетчиков 19, 21 и 22.

Счетчик 21 и последовательно соединенные счетчики 19 и 20 определяют соответственно число фронтов (из общего объема выборки), попавших за пределы зоны и в интервал зоны. Если будет заполнен импульсами фронтов либо счетчик 21, либо счетчики 19 и 20, сигнал с одного из выходов указанных счетчиков через элемент ИЛИ 23 э откроет второй блок 13 управления, и фронты входного сигнала с выхода выделителя

14 начнут поступать на второй блок 13 управления. Такая ситуация возникает только в том случае, если основная часть анализируемой выборки фронтов находится либо в интервале зоны, либо за ее пределами.

Одновременно с открытием второго блока 13 управления триггер 24 переводится в «О», элемент И 17 закрывается и тем самым запрещает выключение второго блока 4з

13 управления по окончании анализа объема выборки.

Если число фронтов, попавших в зону, оказалось таким, что заполнилась только емкость счетчика 19, то тогда триггер 24 перейдет в «1», элемент И 17 откроется и, в момент окончания анализа выборки, второй блок 13 управления закроется, т. е. поступление фронтов с выхода выделителя 14 на вход второго блока 13 управления пре- 5 кратится. Отмеченная ситуация характерна при действии на входе УТС импульсов шума, либо сильно защумленного полезного сигнала.

Счетчик 19 заполняется и при действии на входе УТС информационных посылок, что всякий раз переводит триггер 24 в «1». Однако в этих случаях, когда основная часть объема выработки фронтов находится либо в зоне, либо за ее пределами, заполняется соответственно счетчик 20 или счетчик 21.

g результате триггер 24 возвращается в «0», второй блок 13 управления остается открытым, т. е. подстройка разрешается. Так протекает операция распознавания информационного сигнала и шума.

Предложенное устройство обеспечивает время удержания состояния синхронизма при перерывах связи и действии шума на входе УТС порядка 15 — 30 мин, сохраняет высокую цикловую устойчивость тактовой синхронизации при любых интенсивностях мультипликативной и аддитивной помех; обеспечивает минимальный эффект накопления фазовых сдвигов, обусловленных многолучевостью и качанием времени распространения сигнала.

Формула изобретения

1. Устройство тактовой синхронизации, содержащее последовательно соединенные опорный генератор, первый блок управления, блок дискретной автоподстройки, блок усреднения и астатическое звено регулирования, выход которого подключен к входам блоков выделения чередующихся и нечередующихся импульсов, причем второй выход опорного генератора подключен к другому входу астатического звена регулирования, другой выход которого подключен к второму входу первого блока управления, третий вход которого соединен с другим выходом блока усреднения, второй вход которого соединен с первым выходом анализатора и первым входом второго блока управления, первый выход которого через элемент ИЛИ подключен к другому входу блока дискретной автоподстройки, выход которого подключен к входу формирователя зоны, выход которого подключен к первому входу анализатора и второму входу второго блока управления, второй выход которого подключен к другому входу элемента ИЛИ, при этом выход выделителя фронтов подключен к второму входу анализатора и третьему входу второго блока управления, а его входы соединены соответственно с третьим выходом опорного генератора и выходом блока дискретной автоподстройки, отличающееся тем, что, с целью повышения точности, введены первый, второй интеграторы и блок распознавания, причем выходы блоков выделения чередующихся и нечередующихся импульсов через первый интегратор подключены к четвертому входу второго блока управления, а второй выход выделителя фронтов

803112 через блок распознавания — к иятому входу второго блока управления, причем выход формирователя зоны подключен к второму входу блока распознавания, выход которого подключен к шестому входу второго блока управления и через второй интегратор— к третьему входу анализатора, второй выход которого подключен к другому входу вто. рого интегратора.

2. Устройство по п. 1, отличающееся тем, что блок распознавания выполнен в виде элементов И, ИЛИ, счетчиков и триггеров, причем выход первого элемента И через последовательно соединенные первый, второй счетчики и триггер, подключен к входу второго элемента И, а выход третьего эле-

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2423655/18-09, кл. Н 04 L 7/08, 1976 (прототип) .

803112

Составитель E. Голуб

Редактор О. Филиппова Техред А. Бойкас Корректор М. Демчик

Заказ 10276I69 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4