Устройство для измерения частоты

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВЙЖСК©МУ СВИ ИТИЗЬСТВУ

Союз Советских

Социалистических т всяублии

Q 01 к 23/02 с присоединением заявки Их—

tÚñóäàðñòâåííûé комитет

СССР . ио делам иаобретеиий и открытий (23) Приоритет

Опубликовано 1Ы281. Ькичютеиь 89 6 (53} УДК 621. 317. .3(088.8) Дата опубликования описания 17. О 2. 81 (72) Авторы изобретения

Ю

B.E. CeMQMQQ и Д.H. Соболев (71) Заявитель.(54) УСТРОЙСТВО ДЯЯ ИВ)ЯРЕЯИЯ ЧАСУОЙЯ

1 ., 2

Изобретение относится к раиИОизме Дниоэ нОДКтнвЧЕНи к вмиодам блока уаренням. . : : равлеиия частотой гетеродинов Я .

: Известно устройство для ивмереиня : : 4@ниаФ устройство не.обеспечивает частоты, содержащее генератор а : Пе» добтатсйэей то%нести измерений е рестройкой частоты, преобразователь ..- .Мель ивебуетеиия - повьхяеиие точчастоты, счетчик, фазовый детектор, . н@сти измерений. генератор стандартных. сигналов, пре-" образователь частоты,.дополнительиый ;,, в,,й ., е ее ие генератор. В устройстве частота меат» 1 и и и,Ьл- иаерФ вх ко„ ного гетероднна определяется путем. . : о, и,,,н и. в

:измерения номера высщей гарж ндки 1) . рЫ@ sx перво.о и в М юго cR%âНедостатком данного ycTpoacTçà яв.- лей содинеНЫ с ызи ва34и гетеродинов, ляется недостаточный частотный диа- а выходы йодклМеиы к иервнщ входам .f5 @азовых детекторов втоРые. входы ко

Наиболее близким по теииической . торых соедйнены е Виходами .вяектрои,сущности к.заявленному является.уст- ., :но-счетного частотомера, два входа ройство, содержащее два смесителя, " которого соединены с выходайи. упомипервыФвходы которых соедимемы .co : . нутых- гетеродииов и первым и вторым

-входной щиной, вторые.входы:еоедине- ;р; входами .третьего смеси;&витя, выход ны с выходами гетеродинов,- а выходы . -.которого подключен к третьему входу подключены .к первым входам Фазовых . электронно-счетного частотомера, .детекторов, вторые входы которых - - . причем верные входы управления гетесоединены с выходами электронно-счет.-, родинов, подключены к выходам блока . ного частотомера два входа которого 2$ управления частотой гетеродинов, ввесоединены с выходами гетеродинов.и : -дены два диковин детектора элемент . входами третьего смесителя, выход .,- задержки .и два логических элемента которого подключен к третьему входу И, первый вход первого из которых электронно-счетного частотомера, при- . соединен через элемент задержки с чем первые входы управления гетеро- ..щ одним выходом первого пикового детек805193 тора, второй вход первого логического элемента И соединен с первым выходом второго пикового детектора, второй выход которого соединен с первым входом второго логического элемента И, второй вход которого соединен с первым выходом первого логического элемента И, выход второго логического элемента И соединен со вторым входом управления второго гетеродина, а второй выход первого логического эле- 0 мента И соединен со входом блока управления частотой гетеродинов, причем входы пиковых детекторов, соединены с выходами фазовых детекторов, а выход первого пикового детектора соединен со вторым входом управления первого гетеродина.

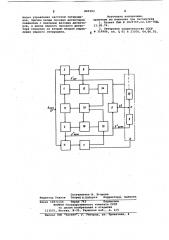

На чертеже .приведена структурная электрическая схема описываемого устройства.

Устройство содержит гетеродины 1 20 и 2, смесители 3-5, фазовые детекторы

6 и 7, электронносчетный частотомер

8, содержащий два делителя 9 и 10, блок 11 управления частотой гетеродинов, пиковые детекторы 12 и 13, эле- 25 мент задержки 14, логические элементы И 15 и 16. Входной сигнал подан на входную шину 17.

Принцип работы устройства заключается в следующем. 30

При подаче на входную шину 17 сигнала неизвестной частоты перестройкой гетеродина 1, смеситель 3, фазовый детектор б, пиковый детектор

12 вводят в. синхронизм с фазовым детектором б, (причем блоки 1,3,6,12 представляют собой цепь фазовой автбподстройки частоты, на чертеже не показано) характеризующийся соотношением между частотами

40 иьи-" fuBN 1 где h - номер гармоники гетеродина 1;

fче„- частота гетеродина;

1 опорная частота.

Одновременно перестраивается гете- 45 родин 2 (идентичный гетеродину 1).

При установлении соотношения

11

"ц и "чен он где fuz„-частота гетеродина 2 50 на логический элемент И 15 поступает сигнал только с пикового детектора 13, блок 11 управления частотой гетеродинов продолжает пе1рестраивать гетеродин 2. Время задержки элемента задерж- 5 ки 14 примерно равно времени расстройки гетеродина 2. Гетеродин 2 перестраивается до установления соотношения

If иЗи 60

На логический элемент И 16 поступает вновь сигнал с пикового детектора 13, а так как на другом входе имеется сигнал с пикового детектора 12, то не выходе логического элемента И 15 поя- 65 вится сигнал, который отключит блок

11 управления частотой гетеродинов и включает цепь фазовой автоподстройки частоты гетеродина 2 (на чертеже не показано),. в которую включены гетеродин 2, смеситель 4, фазовый детектор

7, пиковый детектор 13 и логический элемент И 16.

Номер гармоник о;1ределяется по е чеи яе f! чен чен

Смеситель 5 выделяет разность частот гетеродинов 1 и 2

II ° ="чеи "чен а делитель, работающий в режиме измерения отношения частот, выделяет номер гармоник "и". Значение измеряемой частоты равно

fegg= ueH" + он

Делитель 9 умножает время измерения частоты электронно-счетным частотомером на номер гармоники "и". Значение частоты равное 1 „ добавляется в самом частотомере.

Формула изобретения

Устройство для измерения частоты, содержащее первый и второй смесители, первые входы которых соединены со входной шиной, вторые входы первого и второго смесителей соединены с выходами гетеродинов, а выходы первого и второго смесителей подключены к первым входам фазовых детекторов, вторые входы которых соединены с выходами электронно-счетного частотомера, два входа которого соединены с выходами упомянутых гетеродинов и первым и вторым входами третьего смесителя, выход которого подключен к третьему входу электронно-счетного частотомера, причем первые входы управления гетеродинов подключены к выходам блока управления частотой гетеродинов, о тл и ч а ю щ е е с я тем, что, с целью повышения точности измерений, в него введены два пиковых детектора, элемент задержки и два логических элемента И, первый вход первого из которых соединен через элемент задержки с одним выходом первого пикового детектора, второй вход первого логического элемента И соединен с первым выходом второго пикового детектора, второй выход которого соединен с первым входом второго логического элемента И, второй вход которого соединен с первым выходом первого логического элемента И, выход второго логического элемента И соединен со вторым входом управления второго гетеродина, а второй выход первого логического элемента И соединен со входом

805193 Составитель В. Егорова

Редактор Павлов Техред И.вабурка Корректорц. Бабинец

Заказ 0 72 66 Тираж Подписное

ВНИИПИ ГосударстВенного комитета СССР по делам изобретений и открытйй

113035, Москва, Ж-35, Раушская наб, д. 4/5

Филиал ППП Патент, г ° Ужгород, ул. Проектная, блока управления частотой гетеродинов, причем входы пиковых детекторов соединены с выходами фазовых детекторов, а выход первого пикового детектора соединен со вторым входом управления первого гетеродина.

Источники информации, принятые во внимание прн экспертизе

1. Патент США В 3829769,кл.324-70Д, 13.08.74.

2. Авторское свидетельство СССР

9 319906, кл. Я 01 В 23/00, 04.06.70.