Устройство для программного управления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (11)805256

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.04.79 (21) 2753175/18-24 (51) М. Кл з с присоединением заявки №вЂ”

G 05 В 19/08

Геаударствеииый комитет (23) Приоритет— по делам изооретеиий и открытий (53) УДК 621.503..55 (088.8) Опубликовано 15.02.81. Бюллетень № 6

Дата опубликования описания 25.02.81 . .аврило ва;," э

Agog -.-- у . -., = 0., . .т ", т

/ (72) А вторы изобретения

1О. Н. Бутик, Л. А. Бородина, Л.

О. Л. Макове ев и В. С. М (71) Заявитель (54) УСТРОИСТВО ДЛЯ ПРОГРАММНОГО

УПРАВЛЕНИЯ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах программного логического управления в качестве времязадающего устройства.

Известен автоматический программатор временных интервалов, содержащий генератор импульсов, управляемый делитель частоты, счетчики, схемы совпадения, запоминающее устройство такта, входные и выходные ключи, регистр адреса временных интервалов (1). 1О

Использование данного программатора в случае организации большого количества временных задержек приведет к значительным аппаратурным затратам, так как он позволяет отрабатывать ограниченное число временных интервалов последовательно во времени.

Наиболее близким к предлагаемому по техническому решению является программное реле времени, содержащее исполнительный блок, дешифраторы, схемы совпадения, импульсную ячейку, пересчетный блок, генератор импульсов, блок выбора режимов и линию задержки, в котором входы схемы совпадения соединены с первым дешифратором и импульсной ячейкой, подключенной ко входу генератора импульсов, выходу блока выбора режимов и входу линии задержки, а выход схемь1 совпадения связан с пересчетным блоком, подключенным к выходам генератора импульсов, блоку выбора режимов и входу второго дешифратора, соединенного выходами через исполнительный блок с первым дешифратором (2) .

Использование этого устройства для реализации большого числа временных задержек приводит к снижению надежности систем программного и логического управления вследствие значительного увеличения аппаратурных затрат на реле времени. Например удвоение числа задержек, время работы которых может перекрываться, практически приводит к удвоению оборудования, что значительно снизит надежность. Кроме того, к недостаткам рассматриваемого устройства следует отнести отсутствие гибкости изменения количества и длительности временных интервалов.

Цель изобретения — расширение функциональных возможностей при повышении надежности за счет снижения аппаратурных затрат при реализации большого числа вре805256 менных задержек в сравнительно широком диапазоне и обеспечение возможности изменения числа и длительности временных интервалов.

Указанная цель достигается тем, что устройство для программного управления, содержащее блок синхронизации, последовательно соединенные первый элемент И, первый счетчик импульсов, подключенный первыми выходами к первым входам вторых элементов И, третий элемент И, первый элемент НЕ и четвертый элемент И, подКлюченный выходом ко вторым входам вторых элементов И, последовательно соединенные генератор импульсов, второй счетчик импульсов, группу пятых. элементов И и первый элемент

ИЛИ, и последовательно соединенные блок выбора режимов и дешифратор, выходы которого соединены со вторыми входами группы пятых элементов И, содержит шестые элементы И, второй элемент НЕ, седьмой элемент И и последовательно соединенные восьмой элемент И, девятый элемент И, группу десятых элементов И и вторые элементы

ИЛИ, вторые входы которых соединены с выходами шестых элементов И, выходы — со вторыми входами первого счетчика импульсов, подключенного вторыми выходами через последовательно соединенные восьмой элемент И и второй элемент НЕ к первому входу первого элемента И, второй вход которого соединен с выходом первого элемента

ИЛИ, третий вход — с первым выходом блока синхронизации, подключенного вторым выходом к первым входам шесть1х элементов И, третьим выходом — ко второму входу девятого элемента И, четвертым выходом — ко второму входу четвертого элемента И и к первому входу седьмого элемента И, второй вход которого соединен с выходом третьего элемента И, а вторые выходы блока выбора режимов подключены ко вторым входам группы десятых элементов И.

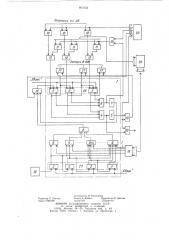

На чертеже представлена функциональнаясхема устройства.

Устройство содержит пересчетный блок 1, в который входят триггеры 2 и 3, третий элемент И 4, первый элемент НЕ 5, восьмой элемент И 6, второй элемент НЕ 7, первый элемент ИЛИ 8 и пятые элементы И 9, шестые элементы И 10, десятые элементы И 11, вторые элементы ИЛИ 12, девятый элемент

И 13, первый элемент И 14, четвертый элемент И 15, седьмой элемент И 16, вторые элементы И 17, дешифратор 18, генератор 19 импульсов, блок 20 синхронизации, имеющий второй 21, третий 22, первый 23, и четвертый 24 выходы и блок 25 выбора режимов, а триггеры 2 и 3 образуют соответственно первый 26 и второй 27 счетчики импульсов.

Устройство работает следующим образок

Для вычисления временной задержки используется одна команда. Комбинация в разрядах первой части команды соответствует коду временной операции, разрешающей вы4 работку сигналов на выходах блока 20 синхронизации. Разряды второй части команды задают код начального установа счетчика 26.

Разряды третьей части команды задают шаг отсчета величины временных интервалов, за5 датчиков которых является счетчик 27 и генератор 19. Оставшиеся разряды команды определяют адрес, по которому производится запись и считывание промежуточных результатов отсчета временных интервалов.

Рассматриваемое устройство может ра О ботать как синхронно с запоминающим устройством (ЗУ), в котором хранится программа работы, так и асинхронно. В первом случае генератор 19 должен быть засинхронизирован циклом обращения к ЗУ, а программа может быть либо линейной, либо разница во времени прохождения ее по различным ветвям не должна превышать допустимой погрешНости. В случае асинхронности ошибки отсчета можно избежать использованием прерывания по окончании временного интервала или программными изменениями значений полей команды и промежуточного результата. В связи с этим для анализа . приндипа работы устройства достаточно рассмотреть случай синхронной работы.

Перед началом работы по сигналу «Сброс» триггеры 2 и 3 счетчиков блока 17 и соот- ветствующий массив в ЗУ устанавливаются в нулевое состояние. Работой устройства управляют тактовые импульсы, возникающие на выходах блока 20 синхронизации по

30 команде указанного выше формата.

Рассмотрим некоторый J-ый цикл работы, связанный с подсчетом i-го временного интервала.

При подаче первого тактового импульса с выхода блока 20 на входы элементов И 10, код промежуточного результата в соответствии с адресом через входы элементов ИЛИ

12 из ЗУ попадает на установочные входы триггеров 2. Если эти триггеры установлены в нулевое состояние, что фиксирует выход

40 элемента 6, то по второму тактовому импульсу с выхода блока 20, на выходе элемента 13 будет сигнал разрешения установки начального кода из ЗУ блока 25 (разряды A+1-В).

Этот сигнал подается на входы элементов 11, другие входы которых связаны с соответст4> вующими шинами ЗУ блока 25. Код начального установа через элементы 11. и входы элементов ИЛИ 12 попадает на установочные входы триггеров 2. Если хотя бы один триггер 2 счетчика 26 находится в единичном состоянии, что фиксирует выход элемента НЕ 7, то по третьему тактовому импульсу с выхода блока 20 и сигналу с выхода элементов ИЛИ 8 элемент 14 разрешает добавление единицы по счетному входу младшего разряда этого счетчика. При этом сигнал на выходе элемента ИЛИ 8 будет иметь место при совпадении на одном из элементов 9 информации, поступающей с триггеров

3 и кода шага отсчета временных интервалов, который подается с ЗУ блока 25 (раз805256 ряды В1-С) через дешифратор 18 таким образом, что выполняются определенные логические условия.

Процесс отсчета временных интервалов заканчивается, если к моменту появления четвертого тактового импульса с выхода блока 20 все триггеры 2 находятся в единичном состоянии. Этот факт фиксирует элемент И 4, выход которого вместе с четвертым тактовым импульсом с выхода блока 20 подается на входы элемента И 16. С выхода этого элемента снимаетсп сигнал временной задержки, соответствующий коду начального установа и величине шага отсчета временного интервала. Процесс отсчета временного интервала не заканчивается, если к моменту появления четвертого тактового импульса хотя бы один из триггеров 2 находится в нулевом состоянии. Этот факт фиксирует элемент И 15, на,входы которого подаются четвертый тактовый импульс с выхода блока 20, сигнал с выхода элемента НЕ 5 Для продолжения отсчета временных интервалов в дальнейшем промежуточные результаты (состояние триггеров 2) через элементы И 17, управляемые элементом И 15, засылаются в

ЗУ по адресу, задаваемому соответствующими разрядами команды, содержимое счетчика 27 увеличивается на единицу. Наступает следующий цикл и процесс работы устройства повторяется. После обработки всех временных интервалов происходит возврат к первому и процесс работы зацикливается.

Использование данного устройства для автоматизации судовых технических средств обеспечивает повышение надежности этих систем управления за счет снижения аппаратурных затрат при реализации большого количества временных задержек в сравнительно широком диапазоне.

Формула изобретения

Устройство для программного управления, содержащее блок синхронизации, последовательно соединенные первый элемент И, первый счетчик импульсов, подключенный первыми выходами к первым входам вторых элементов И, третий элемент И, первый элемент НЕ и четвертый элементИ, подключенный выходом ко вторым входам вторых элементов И, последовательно соединенные генератор импульсов, второй счетчик импульсов группы пятых элементов И и первый элемент ИЛИ, и последовательно соединенные блок выбора режимов и дешифратор, выходы которого соединены со вторыми входами группы пятых элементов И, отличаю щееся, тем, что, с целью расширения функциональных возможностей устройства, оно содержит шестые элементы И, второй элемент НЕ, седьмой элемент И и последовательно соединенные восьмой элемент И, девятый элемент И. группу десятых элементов

И и вторые элементы ИЛИ, вторые входы которых соединены с выходами шестых элементов И, выходы — со вторыми входами о первого счетчика импульсов, подключенного вторыми выходами через последовательно соединенные восьмой элемент И и второй элемент НЕ к первому входу первого элемента

И, второй вход которого соединен с выходом 5 первого элемента ИЛИ, третий вход — спервым выходом блока синхронизации, подключенного вторым выходом к первым входам шестых элементов И, третьим выходом — ко второму входу девятого элемента И, четвеотым выходом — ко второму входу четверто30 го элемента И и к первому входу седьмого элемента И, второй вход которого соединен с выходом третьего элемента И, а вторые выходы блока выбора режимов подключены ко вторым входам группы десятых элементов И.

35 Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР № 443386, кл. G 06 F 9/00, 1973.

2. Авторское свидетельство СССР .№ 327575, кл. Н 03 К 3/00, 1971 (прототип).

80525б

ПеРепись т з 35

Составитель Н. Белинкова

Редактор Л. Повхан Техред A. Бойкас Корректор М. Демчик

Заказ 0642/69 Тираж 951 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и оз крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4