Цифровое устройство для потенцирования

Иллюстрации

Показать всеРеферат

Союз Севетскик

Социалистическик

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТИЗЬСТВУ

<щ805303 (61) Дополнительное к авт. свид-ву— (22) Заявлено 190279 (21) 2755838/18-24 с присоединением заявки Йо (23) Приоритет

Опубликовано 15,02.81. Бюллетень Н9 6

Дата опубликования описания 180281 (51) М. Кл.

6 06 Г 7/38

Государственный комитет

СССР но дмам нзобретеннй н открытнй (53) УДК 681 З (088. 8) А.Н. Флоренсов, В.И. Потапов и N.I0. Плотник

I

Омский политехнический институт (72) Авторы изобретения (71) Заявитель (54) ЦИФРОВОЕ УСТРОИСТВО ДЛЯ HOTEHUHPOBAHHR

Изобретение относится к вычислительной технике и может быть исполь. зовано как цифровой генератор функции экспоненты е" и для построения специализированных и универсальных быстродействующих вычислительных устройств.

Известно устройство для функционального преобразования, содержащее регистр аргумента, блоки памяти, умножители и сумматор "„11 .

Недостатком устройства является большой объем оборудования.

Наиболее. близким по технической сущности к изобретению является устройство для потенцирования, содержащее регистр аргумента, последовательно соединенные блок памяти, сумматор и регистр результата f2) .

Недостатком данного устройства является низкая точность вычисления функции е".

Цель изобретения — повышение точности.

Поставленная цель достигается тем, что в устройство, содержащее регистр аргумента, блок памяти и последовательно включенные сумматор и регистр результата, причем выход блока памяти соединен с первым входом сумматора,,ЗО дополнительно введены блок деления и два блока сравнения, причем выходы с первого по (К-1)-й и с (К+1)-го до и (где n — количество разрядов регистра аргумента) разрядов регистра аргумента подключены ко входам соответственно первого и второго блоков сравнения, выход К-ro .разряда регистра аргумента подключен к управляющим входам первого и второго блоков сравнения, выходы которых подключены соответственно к адресному входу блока

I памяти и входу делителя блока деления, вход делимого которого подключен к выходу блока памяти, выход блока деления подключен ко второму входу сумматбра.

Значение функции е вычисляется по приближенной формуле

<4 4 е "Д PXq (i)

2 -ах где x = х„+ах

При этом погрешность gR/ .— (Ьх)

Если значение параметра к, определяющее старшие К разрядов х, т.е. величину х, фиксированно, то формула (1) дает 3К верных разрядов после запятой.

805303

Положим

1О формула изобретения

exp„ если.х< = o { )

0 х + 2"", если хК = 1

Гдх, если хх = О дх - 2, если х, = 1, тогда х = zp + д z, /дг/(2 и полученные выше оц. нки точности формулы (1) остаются поэтому справедливыми при одновременной замене х на и дх на дz. В это же время промежуточный аргумент zp принимает значительно меньше различных значений, а именно (2" " + l) значений вместо

2 в случае аргумента хр. Для расчетов получаем окончательную формулу

2. x4 О о (3)

Для вычисления по формуле (3) можно воспользоваться таблицей значений е 0, 1 асположив ее в соответствующем блоке памяти.

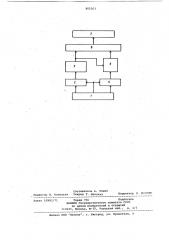

Блок-схема предлагаемого устройства изображена на чертеже.

Устройство содержит регистр 1 аргумента, первый блок 2 сравнения, 25 блок 3 памяти, второй блок 4 сравнения, блок 5 деления, сумматор 6 и регистр 7 результата.

Устройство работает следующим образом. 30

Выход К-ro разряда регистра 1 аргумента дает значение К-го разряда аргумента х, именно х, в зависимости от которого в соответствии с соотношениями (2 ) блоками сравнения 2 и 4 образуются значения zp и д z, Блок 2 принимает с выхода регистра 1 аргумента значение промежуточного, аргумента х и в зависимости от значе- 0 ния сигнала на управляющем входе передает значение х без изменений (x = 0), либо добавляет к коду х> единицу К-го разряда (х< = 1). Блок

4, на вход которого поступает .значением х, формирует значение кода 2 - . дх {в случае хк = О) и код величины 45

{2 + 2 ) - дх (в случае х, = 1) .

Иэ блока 3 памяти по поступающему на его вход аргументу zp, используемому как адрес константы в блоке, выбирается соответствующее значение

Ф е О. Это значение, смещенное на два разряда влево, подается на вход делимого блока 5 деления, что соответствует величине 4e î, а на вход делителя поступает значение 2 — дг. Сумматор 6 выполняет вычитание константы е о с выхода блока 3 памяти из значения выхода блока деления, равного

4 Р го /(2 — Ь z ), образуя в соответствии с формулой (3} занимаемое на регистре 7 результата искомое значение функции е".

Объем. блока памяти предлагаемого устройства составляет. величину (2 + 1) констант, а точность результата потенцирования при этом равна 3К двоичных разрядов дробной части результата.

Цифровое устройство для потенцирования, содержащее регистр аргумента, блок памяти и последовательно соединенные сумматор и регистр результата причем выход блока памяти соединен с первым входом сумматора, о т л и ч а ю щ е е с я тем, что, с целью увеличения точности, в него дополнительно введены блок деления и два блока сравнения, причем выходы с первого по (K-1)-й и с (К+1)-го дО и (где л — количество разрядов регистра аргумента) разрядов регистра аргумента подключены ко входам соответственно первого и второго блоков сравнения, выход К-ro разряда регистра аргумента подключен к управляющим. входам первого и второго блоков сравнения, выходы которых подключены соответственно к адресному входу блока памяти и входу делителя блока деления, вход делимого которого подключен к выходу блока памяти, выход бло. ка деления подключен ко второму входу сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 575647, кл. G 06 F 7/38, 1977.

2. Авторское свидетельство СССР по заявке 9 2401420/18-24, кл. G 06 F 7/38, 1977 {прототип).

805303

Составитель A. Зорин

Редактор Л. Копецкая Техред T Яаточка Корректор И, И ро аи

Заказ 10903/71

Тираж 75á Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и Открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.. Ужгород, ул. Проектная, 4