Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

< н805487 (61) Дополнительное к авт. саид-ву(22) Завалено 05 ° 02. 79 (21) 272 234 4/18-21 с прнсоедннвннем заявки М— (23) Г3риорнтет (5!)М. Кл.з

Н 03 К 13/17

Государственный комитет

СССР по делам изобретений и, открытий

Опубликовано 1502 81. Болл®tera 6 (53) УДК ее1.325 (088.8) Дата опубликования описанию 18,0281

В.Н.Махов, A,В.Жуков, О.В.Игнатьев, Н.Ф.ШкЬла,, .ЩЦ:,Щ®ккк и Б.С.Новисов нитинол.:

АЛЕХИ :: - " Д д;.Д,.t Я тЕИА

Уральский ордена Трудового Красного ЭнамеМо цацитехнический институт им. С.М.Кирова (72) Авторы изобретения (71) Заюантель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к радиотехнике и предназначено для использования в спектрометрии ионизирующих излучений.

Известен аналого-цифровой преобразователь, содержащий дискриминатор уровня, генератор эталона, устройство выборки хранения (1).

Недостатком устройства является низкое быстродействие.

Известен аналого-цифровой преобразователь, содержащий входное Устройство, соединенное с первым входом коммутатора, выход которого через 15 последовательно соединенные сумматор и две ячейки памяти соединен со своим вторым входом, второй вход сумматора через генератор эталонов и блок управления генератором эталонов соеди- 20 нен с выходом задающего генератора„ выход сумматора через дискриминатор уровня соединен с входом регистра сдвига, вйход которого соединен с входом блока вывода кода, логические входы и выходы входного устройства, коммутатора, ячеек памяти, дискриминатора уровня, регистр сдвига, блока вывода кода и задающего генератора соединены с блоком управления 21 . Зы

Недостатком устройства является низкое быстродействие.

Цель изобретения — повышение быстродействия.

Указанная цель достигается тем, что в аналого-цифровой преобразователь, содержащий входное устройство, коммутатор, ячейку памяти, дискриминатор уровня, блок синхронизации, блок распределения импульсов, счетчик импульсов, арифметическое устройство, блок вывода кода, задающий генератор, блок управления, генератор эталонного тока, введены дополнительный дискриминатор уровня, интегратор, два блока эталонной длительности, разрядное устройство, два резистора, причем выход входного устройства через первый реэис тор соединен с входом интегратора, выходами разрядного устройства и генератора эталонного тока, вход которого через первый блок эталонной длительности соединен с выходом блока синхронизации, выход интегратора соединен с входом разрядного уст- ройства и входом дискриминатора уровня, выход коммутатора через второй резистор соединен е входом .интегратора, управляющий вход комму805487 татора через второй блок эталонной длительности соединен с шестым выходом блока управления, второй вход которого через дополнительный дискриминатор уровня соединен с входом входного устройства, а седьмой выход блока управления соединен с управляющим входом разрядного устройства.

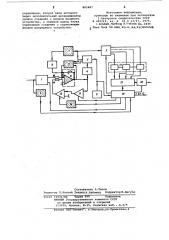

На чертеже приведена структурная электрическая схема устройства.

Преобразователь содержит входное устройство 1, дискриминатор 2 уровня, интегратор .3, дискриминатор 4 уровня, блок 5 синхронизации, задающий генератор 6, блок 7 эталонной длительности, генератор 8 эталонного тока, блок

9 распределения импульсов, счетчик

10 импульсов, ячейку 11 памяти, коммутатор 12, блок 13 управления, блок

14 эталонной длительности, арифметическое устройство 15, блок 16 вывода кода, разрядное устройство 17, резисторы 18 и 19.

Устройство предназначено для преобразования в код площади импульса (заряда) и работает следующим образом.

В исходном состоянии входное устройство 1 закрыто, разрядное устройство 17 замкнуто, создавая на выходе интегратора 3 нулевой уровень, ячейка 11 открыта по входу, коммутатор

12 подает на вход интегратора 3 нулевой потенциал, счетчик . 10 обнулен, Измеряемый сигнал Ux поступает на вход входного устройства 1 и на вход дискриминатора 2. Последний вырабатывает логический сигнал (по длительности равный или несколько больший длительности измеряемого сигнала 01 ), который запускает все устройство в целом. Входное устройство

1 открывается, закрываетея разрядное устройство 17 и входной сигнал

Uq поступает через входное устройство 1, интегратор 3 на вход дискриминатора 4. Логический сигнал с выхода дискриминатора 4 через блок 5 поступает синхронно с сигналом задающего генератора 6 через блок 7 на вход генератора 8, эталонные импульсы которого подаются на вход интегратора 3. Генератор 8 вырабатывает импульсы до тех пор, пока разность U» -U> (где и чис о эталонных импульсов) на выхо интегратора 3 не будет меньше ну Полученные и импульсов компенсации через блок 9 записываются в секцию старших разрядов счетчика

10. Остаток Uq-U@ . . с выхода интегратора 3 записывается в ячейку

11, с выхода которой он подается на вход коммутатора 12. После окончания логического сигнала с выхода дискриминатора 2. блок 13 закрывает ячейку 11 и входное устройство 1 н на . фиксированное время At .через комзвутатор 12 и резистор 19 подключает выход ячейки 11 ко входу интегратора

3. Время .Ы задается вторым блоком

14. Величина де, коэффициенты передачи ячейки 11 и коммутатора 12 и согласующий резистор 19 выбираются такими, чтобы общий коэффициент пе5 редачи кодиру щего кольца (co входа ячейки памяти 11 до выхода интегратора 3) был равен К=2", где m — число двойных разрядов, получаемых в одном цикле кодирования. С момента срабатывания коммутатора 12 начинается второй цикл кодирования, в котором все повторяется аналогичным образом, с той лишь разницей, что сигнал для измерения (остаток U - U>z. g) ..: подается

15 с выхода коммутатора 12, а результат кодирования записывается в секцию более младших разрядов счетчика 10.

После окончания всех циклов кодирования полученный код через арифме;щ тическае устройство 15, которое приводит код к нормальному виду, и блок

16 выводится из устройства. При этом блок 13 приводит все устройство в исходное состояние.

Формула изобретения

Аналого-цифровой преобразователь, содержащий входное устройство, коммуgg татор, вход которого через ячейку памяти и дискриминатор уровня и блок синхронизации соединен со входом блока распределения импульсов, выходы которого через счетчик импульсов соединены с выходами арифметического устройства, выход которого соединен с входом блока вывода кода, выход задающего генератора соединен со вторым входом блока синхронизации и первым входом блока управления, пять т

40 выходов которого соединены соответственно с управляющими входами входного устройства ячейки памяти, блока распределения импульсов, арифметического устройства и блока вывода кода, генератор эталонного тока о т л ич а ю шийся тем, что, с целью увеличения быстродействия, в преобразователь введены дополнительный дискриминатор уровня, интегратор, ур два блока эталонной длительности, разрядное устройство, два резистора, причем выход входного устройства через первый резистор соединен с входом интегратора, выходами разряд ного устройства и генератора эталонного тока; вход которого через первый блок эталонной длительности соединен с выходом блока синхронизации, выход интегратора соединен с входом разрядного устройства и

40 входом дискриминатора уровня, выход коммутатора через второй резистор соединен с входом интегратора, управляющий вход коммутатора через второй блок эталонной длительности соединен с шестым выходом блока

805487

Составитель A.Òèòîâ

Редактор П.Коссей Техред A.Áàáèíåö КорректорМ.Вигула

Эаказ 10931/80 Тираж 999 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП"Патент, r.Óæãoðîä,ул.Проектная,4 управления, второй вход которого через дополнительный дискриминатор уровня соединен с входом входного: устройства, а седьмой выход блока управления соединен с управляющим входом разрядного устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

М 489219, кл. Н 03 К 13/17, 1975.

z, Конюшен, Stirling А.>roima D,Ü..ZEEE.

Эта& Nuak Sei 1969, Й Ъ-<Е, ИЬ,РЪ(ПРОТОТИП