Одноразрядный десятичный сумматор- вычитатель

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистинеских

- Республик

И АВТОИЖОМУ СВИДИТИДЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 13,0677 (21) 2495414/18-24 с присоединением заявки йо (23) Приоритет—

Опубликовано 23.02.81.Бюллетень Н9 7 р )м. кл.з

G 06 F, 7/50

Государственный комитет

СССР по делам изобретений и откРытий (53) УДК 681.325.5 (088.8) Дата опубликования описания 25.02,81

P2) Автор изобретения

A. И.. Дубовец (7 1) заявитель

Изобретение относится к вычислительной технике и предназначено для арифметического суммирования-вычитания двоично-десятичных кодов чисел.

Известен десятичный одноразрядный сумматор, содержащий двоичный сумматор для получения нескорректированной суммы, а также корректирующий двоичный сумматор и схему обра- ® зования переноса (1 .

Недостатком такого сумматора является то, что в нем невозможно производить прямое вычитание. Для.воэможности получения результата вычитания необходимо дополнительное пре- 15 образование одного нз операндов в дополнительный код, что снижает быстродействие устройства.

Наиболее близким по техническОй сущности к предлагаемому являетая 20 одноразрядный десятичный сумматорвычитатель, содержащий двоичный сумматор-вычитатель для получения не.скорректированного значения суммы или разности„ .блок коррекции, в качестве.которого используется двоичный сумматор, блок формирования переноса, управляющие шины и логические элементы, служащие для управле- .ния коррекцией f2) . 30

Недостатком такого сумматора является сравнительно большое количе-. ство оборудования, используемое, в частности, для построения блока коррекции.

Цель изобретения — уменьшение количества оборудования.

Поставленная цель достигается тем, что одноразрядный десятичный сумматор-вычитатель, содержан,ий четырехразрядный сумматор-вычитатель, блок формирования десятичного переноса и блок коррекции, причем информационные входы двоичного сумматора-вычитателя подключены к входам первого и второго операндов, переноса и заема десятичного сумматора-вычитателя, управляющие входы двоичного сумматора-вычитателя и блока Формирования десятичного переноса подключены к управляющим шинам сложения и вычитания, выход первого разряда двоичного сумматора-вычитателя подключен к первому разряду выхода суммы десятичного сумматора-вычитателя, второй,.третий и четвертый разряды выхода суммы десятичного сумматора-вычитателя подключены к первому, второму и третьему выходам блока коррекции соответственно, входы блока Аор(54 ) ОднОРАЗРядный десятичный суимАтОР-3ычитАтель

807275 мирования десятичного переноса. сое,,инены с выходом переноса двоичного сумматора-вычитателя и выходами его второго, третьего и четвертого разрядов, а выход подключен к выходу переноса десятичного сумматора, первый, второй, третий и четвертый входы блока коррекции подключены к выходам второго, третьего, четвертого разрядов двоичного сумматора.-вычитателя и выходу переноса двоичного сумматора-вычитателя, при этом блок кор- 1. рекции содержит первый полусумматор и одноразрядный двоичный сумматор, первый вход первого полусумматора подключен к первому входу блока коррекции, второй вход которого подклю- 15 чен к первому входу одноразрядного двоичного сумматора, второй вход которого подключен к выходу переноса полусумматора, выход суммы которого подключен к первому выходу блока кор-; О рекции, второй выход которого подключен к входу суммы одноразрядного двоичного сумматора, пятый и шестой входы блока коррекции подключены к выхо— дам заема и инверсии заема из четвер-25 того разряда двоичного сумматора-.вычитателя, а первый и второй управляющие входы — к шинам сложения и вычитания соответственно, выход заема из четвертого разряда двоичного сумматора-вычитателя подключен к выходу заема десятичного сумматора, при этом блок коррекции содержит второй полусумматор, два элемента И-ИЛИ-НЕ и элемент ИЛИ, входы второго полусумматора подключены к третьему входу блока коррекции и выходу переноса одноразрядного сумматора блока коррекции, входы первой группы входов первого элемента И-ИЛИ-НЕ подключены к третьему и шестому входам блока коррек- gp .ции, входы второй группы входов первого элемента И-ИЛИ-НЕ подключены к третьему и пятому входам блока коррекции и выходу переноса одноразрядного сумматора, первая группа входов второго элемента И-ИЛИ-НЕ подключена к выходу инверсии суммы второго полусумматора и первому управляющему входу блока коррекции, вторая груп-. па входов второго элемента И-ИЛИ-НЕ подключена к выходу первого элемента

И-ИЛИ-,НЕ к второму управляющему входу блока коррекции, входы элемента

ИЛИ блока коррекции соединены с четвертым и пятым входами первого полусумматора блока коррекции, выход второго элемента И-ИЛИ-НЕ подключен к третьему выходу блока коррекции.

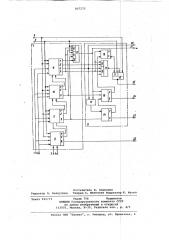

На чертеже.ноказана функциональная схема одноразрядного десятичного сумматора-вычитателя. d0

Входы первого и второго операндов

1 и 2 и входы переноса..3 и заема. 4 десятичного сумматора-вычитателя подключены к информационным входам, а управляющие шины 5 и б — к управляю(4 (! щим входам двоичного сумматора-вычитателя 7, выполненного на четырех одноразрядных сумматораХ-вычитателях

8-11. Входы блока. 12 формирования десятичного переноса, выполненного на элементе И-ИЛИ, соЕдинены с выходом переноса сумматора-вычитателя 7 и с выходами трех его старших разрядов. Влок 13 коррекци содержит полусумматор 14, элемент ЛИ 15, одноразрядный сумматор 16, э емент И-ИЛИ-НЕ .

17, полусумматор 18 и элемент,ф-ИЛИНЕ 19. Выход заема двЬичного сумматора-вычитателя 7 соединен с выходом заема 20, а выход бло а 12 Аормирования десятичного перен са с выходом переноса 21 десятично о сумматоравычитателя.

Выходы первого, вт рого, третьего и четвертого разрядов суммы 22-25 десятичного сумматора вычитателя соединены соответственно с выходом младшего аз я а воичного с ато а-выр р умм р читателя 7, полусумматора 14, одноразрядного сумматора 16 элемента

И-ИЛИ-HE 19 (выходы и усумматора 14, одноразрядного суммат ра 16 и элемента И-ИЛИ-HK 19 образу т соответственно первый, второй и третий выходы блока 13 коррекции).

Сумматор-вычитател работает следующим образом.

Два числа в параллельном коде

8-4-2-1 поступают на ходы 1 и 2, а сигналы переноса и за ма на входы 3 и 4. Dpa выполнении с ожения на управляющей шине 5 устанавливается уровень "1", а при вы олнении вычитания уровень "1" устанавливается на управляющей шине б.

Результат двоичного сумматора-вы1 читателя 7, полученны на выходах одноразрядных сумматоро -вычитателей

8-11 подается на вход блока формирования десятичного переноса 12 и блока 13 коррекции, значение суммы одноразрядного сумматора- ычитателя 8 поступает непосредственно на выход 22 десятичного сумматора вычитателя.

При сложении и вычитании чисел может иметь место нарушение кода на выходе двоичного сумматора-в итателя 7, например, при получен и на его выходе числа более "9". Нарушение кода наблюдается также при возникновении сигнала заема или переноса из одноразрядного сумматора-выч тателя 11. Во всех этих случаях нар ения кода на выходе двоичного сумматора-вычитателя 7 устраняются с.помощью блока 13 коррекции. Например, ри выполнении операции сложения в этом случае блоком 12 формирования десятичного переноса вырабатывается коц 0110 б), Который прибавляется блоком коррекции к значению кода двоичного сумматора-вычитателя 7. Есл выполняется операция вычитания и иМеется сигнал заема из одноразрядного сумматора1 (807275 вычитателя 11, то блоком 13 коррекции в этом случае прибавляется к полученной разности код 1010(10). Если нет нарушения кода на выходе двоичного сумматора-вычитателя 7, то блок 13 коррекции во всех случаях к значению кода двоичного сумматора-вычитателя 7 прибавляет код 0000(0). Результат вычисления выдается на выходах 22-25.

Путем простых соединений входных и выходных цепей заема. и переноса можно строить многоразрядные десятичние сумматоры-вычитатели.

Основнйм отличием предлагаемого десятичного сумматора-вычитателя от известного является иное построение старшего разряда блока 13 коррекции 15 (на полусумматоре 18 и двух элементах И-ИЛИ-HE 17 и 19), что приводит к некоторой экономии оборудования.

Формула изобретения

Одноразрядный десятичный сумматорвычитатель, содержащий четырехразрядный сумматор-вычитатель, блок формирования десятичного переноса и блок коррекции, причем инАормрционные входы двоичного сумматора-вычитателя подключены к входам первого и второго операндов, переноса и заема десятичного сумматора-вычитателя, управ- . ляющие входы двоичного сумматоравычитателя и блока формирОвания десятичного переноса подключены к управляющим шинам сложения и вычитания, выход первого разряда двоичного сумматора-вычитателя подключен к пер- N вому разряду выхода. суммы десятичного сумматора-вычитателя, второй, третий и четвертый разряды выхода суммы десятичного сумматора-вычитателя подключены к первому, второму и третьему выходам блока коррекции соответственно, входы блока формирования десятичного переноса соединены с выходом переноса двоичного сумматоравычитателя и выходами его второго, третьего и четвертого разрядов, а выход подключен к выходу переноса десятичного сумматора, первый, второй третий и четвертый входы блока коррекции подключены к выходам второго, третьего, четвертого разрядов двоичного сумматора-вычитателя и выходу переноса двоичного сумматора-вычитателя, при этом блок коррекции содержит первМй полусумматор и одноразрядный двоичный сумматор, первый вход первого полусумматора подключен к первому входу блока коррекции, второй вход которого подклю ген к первому входу одноразрядного двоичного сумматора, второй вход которого подключен к выходу переноса полусумматора, выход суюаю которого подключен к первому выходу блока кор:рекции, второй выход которого подключен к входу суммы одноразрядного двоичного сумматора, о т л и ч а ю— щ и Й с я тем, что, с целью уменьшения количества оборудования, пятый и шестой входы блока коррекции подключены к выходам заема и инверсии заема из четвертого разряда .двоичного сумматора-вычитателя, а первый и второй управляющие входы — к шинам сложения и вычитания соответственно, выход заема из четвертого разряда двоичного сумматора-вычитателя подключен к выходу заема десятичного сумматбра, при этом блок коррекции содержит второй полусумматор, два. элемента И-ИЛИ-НЕ и элемент ИЛИ, входы второго полусумматора подключены к гретьему входу блока коррекции и выходу переноса одноразрядного сумматора блока коррекции, входы первой группы входов первого элемента

И--ИЛИ-НЕ подключены к третьему и шестому входам блока коррекции, входы второй группы входов первого элемента И-ИЛИ-НЕ подключены к третьему и пятому входам блока коррекции и выходу переноса одноразрядного сум- матора, первая группа входов второго элемента И-ИЛИ-ЯЕ подключена к выходу инверсии суммы второго полусумиатора и первому управляющему входу блока коррекции, вторая группа входов второго элемента И-ИЛИ-НЕ подключена к выходу перэого элемента И-ИЛИНЕ и в орому управляющему входу блока коррекции, входы элемента ИЛИ блока коррекции соединены с четвертым и пятым входами первого полусумматора блока коррекции, выход второго элемента И-ИЛИ-НЕ подключен к третьему выходу блока коррекции.

Источники информации, принятые во внимание при экспертизе

1. Карцев N. A. Арифметика цифровых машин. N., "Наука", 1968, с. 168170, рис. 2-16 °

2. Авторское свидетельство СССР по заявке 9 2159947/18-24, кл. G 06 F 7/50, 1975 (прототип).

Составитель В. Березкин (Редактор Л. Белоусова Техред С. Мигунова Корректо И. Муска

Заказ 292/73 Тираж 756 Подписно

ВНИИПИ Государственного комитета СС Р по делам изобретений и открытий

11

Филиа