Суммирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз СоветскихСоциалистических

Республик н1>807276

К АВТОРСКОМУ СВИ ИТВЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 110479 (21) 2766763/18-24 (51)М. К .з

G 08 F +50 с присоединением заявки Ho—

Государственный комитет

СССР ио делам изобретений и открытий

{23) Приоритет—

Опубликовано 2 302.81.Бюллетень 89 7 (53) УДК 681. 325

,088.8) Дата опубликования описания 250281 а (72) Автор. изобретения

В. В. Ромадин (71) Заявитель (54) СУММИРУЮЩЕЕ УСТРОЙСТВО

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе арифметических устройств ЦВИ.

Известно суммирующее устройство со сдвигом, содержащее суммирующий регистр, сумматор-вычислитель и промежуточный регистр. В суммирующем регистре применен триггер типа RST, у которого счетный вход используется только при сдвиге информации, а установочные входы с помощью логической схемы типа 2И-4ИЛИ служат для записи информации с промежуточного регистра 15 при организации кольца, с кодовых шин при приеме внешней информации, со смежных разрядов суммирующего регистра при выполнении сдвигов влево или вправо. Таким образом, сам ре- 20 гистр служит для приема, хранения, накопления информации и сдвига накопленной суммы. Суммирование (вычитание) производится сумматором-вычитателем. Накопленная сумма со сдвигом влево или вправо получена путем соединения суммирующего регистра с сумматором-вычитателем, включенным в цепь, идущую с выхода регистра на его вход (11 . 30

Однако такая схема замкнутой петли . предполагает наличие в ней дополнительного регистра, служащего для сохранения сигналов на входах суммирующего регистра на время перезаписи суммы, что уменьшает скорость вычислений.

Наиболее близким по технической сущности к предлагаемому является суммирующее устройство, содержащее в каждом разряде одноразрядный сумматор и счетный триггер. Кроме того устройство содержит установочные вентили, элементы И, ИЛИ, НЕ (2 .

Однако известное устройство отличается низким быстродействием.

Цель изобретения †.повышение быстродействия устройства.

Поставленная цель достигается тем, что в суммирующее устройство, содержащее в каждом разряде одноразрядный сумматор и счетный триггер введены элемент неравноэначности и элемент

2И-ЗИЛИ, причем первый вход элемента неравнозначности соединен с прямым ,выходом счетного триггера, а второй вход — с выходом (n + 1) разряда суммирующего устройства (где п — число разрядов суммирующего устройства), выход элемента неравнозначности соеди4

807276 ементов апиажениями:

+ дС„,„д0 +

+ В„ П °

8»q» +

+ А-А„+„ ерандов А и В, вует логичес— "С", выки схемой слоТ Е 0 А +1 А А„ -1

О О

1 О

0 1

1 1

О 1

1 0

1 0

О 1

Сдвиг влево 1

0 О

1 О

0 1

1 1

О !

О

О 0

1 0

1 1

О 1

1

О О

1 0

1 1

О 1 нен со входом (n + 1) разряда суммирующего устройства и с первым инфо — мационным входом элемента 2И-ЗИЛИ, второй и третий информационные входы которого подключены соответственно к выходу (и-1) ра3рара суммирующего устройства и к выходу одноразрядного сумматора, выход переноса которого соединен с одноименным входом (п + 1) разряда суммирующего устройства, а вход подключен ко входу i-го разряда первого операнда суммирующего устройства, управляющие входы элемента 2ИЗИЛИ подключены соответственно ко входам управления сложением, сдвигом вправо, сдвигом влево суммирующего устройства, а выход соединен со счет- 5 ным входом счетного триггера, установочные. входы. которого подключены ко входу i-ro разряда второго операнда суммирующего устройства.

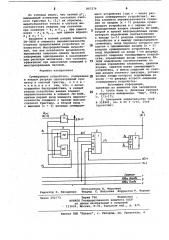

На чертеже представлена схема i-го 2О разряда суммирующего устройства.

Устройство содержит счетный триггер 1, элемент 2И-ЗИЛИ 2, одноразрядный сумматор 3, элемент 4 неравнозначности. 25

В счетном триггере применен триггер типа RST у которого установочные входы используются для парафазного приема исходной цифры операнда А» (А ), а счетный вход используется дважды при сложении с цифрой операнда 8 и при сдвиге результата суммировайия S . Элемент 2И-ЗИЛИ в цепи счетного входа счетного триггера вырабатывает раздельно сигнал дополнения до полной суммы в регистре д я», йли сигналы неравнозначности к предыдущему h.С „ „, или к последующему ,ЬС»»» разрядам в зависимости от сигнала разрешения в одной из шин управления сложением Т, сдвигом влево Е и 40 сдвигом вправо О.

Сложение 1 1

1 1

1, 1

1 . 1

Сдвиг влево 1 О 0

1 О 1

1 1 О

1 1 1

Работа логических дывается следующими в

2И-ЗИЛИ д Т„ = д S

+ ЬС „Е, Ь8„: = б»П» сумматор П1 = А„:8„ элемент неравнозначности A„ A

Операция сложения о для случая Я.» соответс кой "1", 81 — "1" и П» полняются йутем вырабо жения по модулю 2 сигналов В» и П," » результата Я;, равного "1", который через элеМент 2И-3 ËH при наличии разрешающего сигна а Т поступает на счетный вход тригге а А», изменяя его состояние на "О". .ри этом схема логического порога на вырабатывает сигнал переноса П f в последующий разряд А„ +» равный 1" °

Операция сдвига влево операнда А для случая А» — "1" и А; „— "О" вы1 палняется путем выработки элементом неравнозначности сигналов А и А; < результата h;C»», райнаго "I", который через элемент 2 -ЗИЛИ при наличии разрешающего сиги ла Е поступает на счетный вход счетн го триггера А изменяя его состояние на "0".

Операция сдвига вправо операнда А выполняется аналогично сдвигу влево, путем выработки, элементам неравнозначности результата оступающего на триггер А; через элемент 2И-ЗИЛИ при наличий сйгнала D.

Работа суммирующего устройства при других возможных комбинациях внешних сигналов представлена в таблице ,соответствия. (В„П„ -1 S S дС,+1 C„-1 д Г

807276

Формула изобретения

Составитель Е. Федосеев

Редактор н. лаэ аренко ърхред с. мигунова корректор м - шароши

Заказ 292/73. 2ираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгороду ул. Проектная, 4

Иэ таблицы видно, что сигнал ЬТ„, вызывающий изменение состояния счетного триггера А; (S„ ) на обратное, вырабатывается только в случаях несоответствия внешних пар сигналов: при czomeHHH — 8„".и П„ <, при сдвиге ,влево †. А и А„ „, прй сдвиге вправо+ 1.

Введение в полный разряд элемента

2И-ЗИЛИ и элемента неравнозначности отличает предлагаемое устройство от известного быстродействием вычислений, так как появляется возможность выполнения операции сдвига числовой информации одновременно в накапливающем регистре множителя, что особенно эффективно при выполнении операций с 15 многоразрядными числами.

Суммирующее устройство, содержащее Щ в каждом разряде одноразрядный сумматор и счетный триггер, о т л и— ч а ю щ е е а я тем, что, с целью повышения быстродействия, в каждый разряд устройства введен элемент неравнозначности и элемент 2И ЗИЛИ, причем первый вход элемента неравнозначности.соединен с прямым выходом счетного триггера, а второй входс выходом (n + 1) разряда суммирующего устройства (где n — число разрядов суммирующего устройства), выход элемента неравноэначности соединен со входом (n + 1) разряда суммирука его устройства и с первым информационным входом элемента 2И-ЗИЛИ, второй и третий информационные входы которого подключены соответственно к выходу (и-1) разряда суммирующего устройства и к выходу одноразрядного сумматора, вход переноса которого соединен с одноименным входом (n + 1) разряда суммирующего устройства, а вход подклвчен ко входу i ãî разряда первого операнда суммирующего устройства, управляющие входы элемента 2ИЗИЛИ подключены соответственно ко входам управления сложением, сдвигом вправо, сдвигом влево суммирующего .устройства, а выход соединен со счетным входом счетного триггера, установочные входы которого подключены ко входу i-ro разряда второго операнда суммирующего устройства.

Источники информации, принятые во внимание при экспертизе

1. Суббе Ками А. Двоичная техника и обработка инФормации.-"Мир", 1964, tñ. 173-175;

2. Авторское свидетельство СССР

Р 318941, кл. G 06 F 7/50, 1968 (прототип).