Устройство для микропрограммногоуправления

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДИТЕЯЬСТВУ

Союз Соввтских

Социалистических

Реслублим .

<и>807287 (61) Дополнительное к авт, свид-ey— (22) Заявлено 0802.78 (2! ) 2578576/18-24 с присоединением заявки ¹,— (23) Приоритет—

Опубликовано 230281,Бюллетень HQ 7

Дата опубликования описания 25023% (51)М. Кл.з

С 06 F 9/22

Государственный комитет

СССР но делам изобретений н открытий (53) УДК 681. 326 (088.8) 5 If

С. A. Букшин, В. A. Смирнов, Е. A. Каневский и Г. И. Мендерская (f

- Ис""

Р== """

Государственное союзное конструкторско-технологическое Бюро по проектированию: счетных машин и опытный завод (72) Авторы иэббретеимя (71) Заявители (54) УСТРОЙСТВО ДЛЯ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства управления самого различного назначения, в частности, в устройствах управления со страничной организацией постоянных запоминающих устройств.

Известно микропрограммное устройство для управления, использующее постоянное запоминающее устройство со страничной организацией, в котором различают команды передачи управления внутри страницы и команды межстраничной передачи управления (1) 15 Однако это устройство характеризуется значительным объемом оборудования.

Наиболее близким по технической сущности к предлагаемому является 20 микропрограммное устройство для управления, содержащее, первый и второй блоки постоянной памяти, счетчик адреса, регистр страниц, буферный реги стр, блок формирования микрокоманд, 25 элементы И, триггеры, блок ввода-вывода, коммутационное поле, причем адресные входы регистра страниц и установочные входы счетчика адреса являются адресными входами устройства, 30 выходы младших разрядов регистра страниц соединены со входами адреса страниц первого и второго блоков постоянной памяти, выходы счетчика адреса соединены с адресными входами первого и второго блоков постоянной памяти, входы буферного регистра соединены с выходами регистра страниц, а выходы — с адресными входами счетчика адреса 2 .

Недостатком известного устройства является значительный расход оборудования при увеличении объема блока постоянной памяти.

Цель изобретения — уменьшение объема оборудования при увеличении числа блоков постоянной памяти.

Поставленная цель достигается тем, что в устройстве счетный вход триг-гера переключения соединен с выходом блока формирования микроопераций, вход соединен с выходом старшего разряда буферного регистра, а выход соединен с установочным входом старшего разряда регистра страниц, выход старшего разряда регистра страниц соединен со входами страниц первого и второго блоков постоянной памяти.

807287

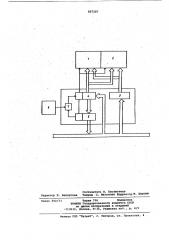

На чертеже представлена блок-сх ма устройства микропрограммного управления.

Устройство содержит блоки 1 и 2 постоянной памяти, счетчик 3 адреса, регистр 4 страниц, буферный регистр

5, блок 6 формирования микрокоманд, триггер 7 переключения.

Устройство работает следующим образом.

Счетчик 3 адреса определяет внутрикристаллический адрес команды, ре . гистр 4 страниц определяет номер вы- бранной страницы блока постоянной памяти, старший разряд регистра страниц определяет конкретно блок 1 или 2 постоянной памяти. При выполнении ко- 15 манд условной и безусловной передачи управления внутри одной страницы блока постоянной памяти код, определяющий адрес перехода, поступает на счетчик адреса 3. 20

При выполнении команд межстраничной передачи управления внутри одного блока 1 или 2 постоянной памяти код номера страницы иэ регистра 4 поступает в буферный регистр 5, код номера страницы перехода поступает в счетчик,3 адреса. При передаче управления из одного блока постоянной памяти в другой по команде "Переключение ПЗУ" (ПП), предшествующей команде "Переход с возвратом" (ПВ), из блока 6 на счетный вход триггера 7 поступает сигнал, изменяющий его состояние. Формат команды ПП вЂ” одно слово. При выполеннии последующей команды ПВ в соответствии с последовательностью управляющих сигналов код, номера страницы из регистра 4 поступает в буферный регистр 5, содержимое счетчика 3 адреса поступает в оперативную память на временное хра- 40 нение, иод номера страницы перехода и внутристраничный адрес перехода поступают в регистр 4 и 3 счетчик адреса, а состояние триггера 7 передается в старший разряд регистра страниц.

Возврат к основной программе цосле выполнения подпрограммы происходит по команде "Возврат" (ВВ), по которой код номера страницы перехода из буферного регистра 5 поступает в регистр 4 страниц, код старшего разряда буферного регистра 5 поступает на установочный вход триггера переключения, с выхода которого - a старший разряд регистра 4 страниц. Внутренний адрес перехода поступает в счетчик 3 адреса.

Если для выполнения подпрограммы необходим переход в другой блок постоянной памяти и затем основная программа должна быть продолжена в этом же блоке постоянной памяти, то вместо команды ВВ должна быть выполнена команда ПВ беэ предшествующей ей команды ПП.

Таким образом, увеличение числа блоков постоянной памяти, не приводит к росту объема оборудования.

Формула изобретения

Устройство для микропрограммного управления, содержащее первый и второй блоки постоянной памяти, счетчик адреса, регистр страниц, буферный регистр, блок формирования микрокоманд, причем адресные входы регистра страниц и установочные входы счетчика адреса являются адресными входами устройства, выходы младших разрядов регистра страниц соединены со входами адреса страниц первого и второго блоков постоянной памяти, выходы счетчика адреса соединены с адресными входами первого и второго блоков постоянной памяти, входы буферного регистра соединены с выходами регистра страниц, а выходы — с адресными входами счетчика адреса, о т л и ч а ю щ е е с я тем, что, с целью уменьшения объема оборудования при увеличении числа блоков постоянной памяти, счетный вход триггера переключения соединен с выходом блока формирования микроопераций, установочный вход соединен с выходом старшего разряда буферного регистра, а выход соединен с установочным входом старшего разряда регистра страниц, выход старшего разряда регистра страниц соединен со входами страниц первого и второго блоков постоянной памяти.

Источники информации, принятые во внимание при экспертизе

1. Патент СИЛ Р 3693162, кл. 340-172 ° 5, опублик. 1970.

2. Авторское свидетельство СССР .Р 486581, кл. G 06 F 15/02, 1975 прототип) °

807287

Составитель В. Евстигнеев

Редактор Л. Белоусова ТехрЕд, С. Мигунова Корректор и. шарош

Заказ 292/73 1ираж 75б Подписное

ВНИИПИ Государственного комитета СССР по делам иивобретений и откритий

-113035, Москва, Ж-.35, Раушская наб., д. 4/5

Филиал IIIIII "Патент" > г. Ужгород, Ул. Проектная, 4