Микропрограммное устройство управ-ления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Сецналистнчесник

Оесеублнк (63) Дополнительное к авт. сеид-ву— (22) Заявлено 110878 (21) 2658913/18-24 с присоединением заявки Йо (23) Приоритет

Опубликовано 2 302.81.бюллетень Но 7 (51) М. Кл.з

G 06 F 9/22

Госуяврствеимый коинтет

СССР яо деави язобретеннй в открытой (53) УДК 681. 325 (088.8) Дата опубликования описания, 230281 (54 ) 4ИКРОПРОГРА МНОЕ УСТРОИСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике, в частности к микропрограммным устройствам управления.

Известно микропрограммное устройство управления,.содержащее блок памяти микрокоманд, регистр микрокомаиды, регистр адреса микрокоманды н дешифратор иикрокоманд (1.).

Недостатком устройства является необходимость большего количества регистров возврата и элементов связи этих регистров с регистром адреса микрокоманд при организации возврата из микропрограмм, что приводит к излишним затратам оборудования.

Наиболее близким по технической суй ности к предлагаемому является микропрограммное устройство управ ления, содержащее память микрокбманд, выхщра которой соединены со входом регистра микрокоманд, регистр адреса микрокоманды, выходы которого чеpe8 дешифратор адреса микрокоманде подключены ко входам памяти микрокоманд, коммутатор, информационные выходы которого соединены с первой группой входов регистра адреса микрокоманды, дешифратор микрокоманды, .входы которого подключены к первой группе выходов регистра микрокоманд, оперативную память, причем, выход регистра микрокоманд соединен с управляющим входом коммутатора, а вторая группа выходов регистра микрокоманд соединена со второй группой входов регистра адреса микрокоманды.

Известное устройство предусматривает использование шифратора, блока реверсивных формирователей тока для организации запоминания и считывания адресов возвратов из микроподпрограмм. При этом.,используется регистр рагенерации, блок усилителей !

5 чтения, дешифратор адреса оперативной памяти, а также часть объема памяти мнкрокоманд для управления укаэанным оборудованием (2 ).

Недостатком устройства является

20 необходимость затрат большого количества оборудования.

Целью изобретения является сокращение оборудования.

Цель достигается тем, что в мик25 ропрограммном устройстве управления, содержащем блок памяти микрокоманд, вход которого соединен с выходом дешифратора адреса мнкрокоманд, а выход — со входом регистра микроко-.

30 манд, выход кода команды которого

807290 соединен с информационным входом дешифратора микрокоманд, выход управления регистра микрокоманд соединен с управляющим входом коммутатора, а выход функциональной выборки — с адресным входом регистра адреса микрокоманд, разрядный выход которого соединен со входом дешифратора адреса микрокоманд, а информационный вход регистра адреса микрокоманд соединен с информационным выходом коммутатора, блок оперативной памяти, выход функциональной выборки регистра иикрокоманд соединен с адресным входом регистра адреса оперативной памяти, управляющий вход которого соединен с первым выходом дешифратора микрокоманд, управляющий вход блока оперативной памяти соединен со вторым выходом дешифратора микрокоманд, третий выход которого соединен с управляющим входом регистра адреса микрокоманд, выход блока памяти микрокоманд соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом блока оперативной памяти, информационный вход которого соединен с информационным выходом коммутатора.

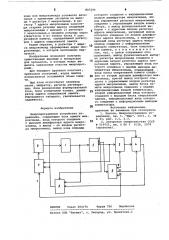

На чертеже представлена блок-.схема устройства.

Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокомаид, регистр 3 адреса оперативной памяти, блок 4 оперативной памяти, дешифратор 5 микрокоманд, дешифратор

6 адреса микрокоманд, регистр 7 адреса микрокоманд, коммутатор 8, выходы 9-11 регистра микрокоманд, вы- хсщы 12-14 дешифратора микрокоманд.

Выход 9 является выходом поля управления, управляющий коммутатором, выход 10 - разряды поля кода команды, выход 11 — выход поля функциональной выборки, использующийся для выбора адреса оперативной памяти и старших разрядов адреса следующей микрокоманды.

Устройство работает следующим образом.

Микрокоманды выбираются из блока

1 памяти микрокоманд через дешифратор 6 адреса микрокоманд по адресу, хранимому в регистре 7 адреса микрокоманды, и засьитается в регистр

2 микрокоманд. Выбранная микрокоманда расшифровывается в дешифраторе 5 микрокоманд и Формирует сигналы, управляющие занесением информации в регистр 3 адреса оперативной памяти, в блок 4 оперативной памяти и в регистр 7 адреса микрокоманд.

Адрес очередной микрокоманды формируется в регистре 7 адреса микрокоманд. Содержимое регистра 7 адреса микрокоманд сигналом с выхода 11 дешифратора 5 микрокоманд увеличивается на единицу при выполнении всех

5 !

О

d0

65 микрокоманд, кроме микрокоманды безусловного перехода и микрокоманды условного ветвления.

Если выполняется микрокоманда безусловного перехода или микрокоманда условного ветвления, то в регистр 7 адреса микрокоманд заносятся старшие разряды адреса следующе1 микрокоманды с выхода 11 регистра 2 микрокоманд, а младшие разряды - через.коммутатор 8 из блока 1 памяти микрокоманд при наличии логического нуля на выходе 9 регистра 2 микрокоманд или из блока 4 оперативной памяти при наличии логической единицы. Причем, младшие разряды, адреса следующей микрокоманды выбираются из блока 4 оперативной памяти, определяемой регистром 3 адреса оперативной памяти, или из ячейки блока

1 памяти микрокоманд, адрес которой увеличен на -единицу относительно адреса микрокоманды безусловного перехода или условного ветвления. В последнем случае не происходит дешифрация кода адреса, занесенного и в регистр микрокоманд.

При построении микропрограмм часто возникает ситуация, когда микропрограмма A включает в качестве микроподпрограммы микропрограмму В, которая в свою очередь содержит микропрограмму С и т.д.

Две микропрограммы С и Д будем считать i-ранга, если они не могут встречаться одна внутри другой и не содержит в себе микропрограмм ранга

i и выше.

Для регистров возврата требуется столько ячеек, сколько рангов в организованных микроподпрограммах. При необходимости обратиться к микроподпрограмме i-го ранга непосредственно перед микроподпрограммой выполняются микрокоманда "Выбор POH", стробирующая занесение информации с выходов 11 регистра 2 микрокоманд в регистр 3 адреса оперативной памяти, и микрокоманда "Загрузка POH, формирующая импульс разрешения записи по информационным входам в ячейку блока 4 оперативной памяти, определяемой регистром 3 адреса оперативной памяти, кода адреса возврата, поступающего из ячейки блока 2 памяти микрокоманд, адрес которой увеличен на единицу относительно адреса микрокоманды "Загрузка POH". В последнем случае не происходит дешифрация кода адреса возврата, занесенного и в регистр микрокоманд.

Для выхода из микроподпрограммы после выполнения последней микрокоманды микроподпрограммы должны выполняться микрокоманда "Выбор РОН", . стробирующая занесение информации с выходов 11 регистра 2 микрокоманд в регистр адреса оперативной памяти

3, и микрокоманда безусловного пере807290

Формула изобретения

ВНИИПИ Заказ 293/74 Тираж 756 Подписное

Филиал ППП "Патент ", г. Ужгород, ул. Проектная,4 хода или микрокоманда условного ветвления с единичным "игналом на выходе 9 регистра 2 микрокоманд. B регистр 7 адреса микрокоманд заносят@я старшие разряды адреса следующей микрокоманды с выходов 11 регистра

2 микрокоманд,а младшие разряды через

«е4мутатор 8 иэ ячейки блока 4 оперативной памяти, определяемой регистром 3 адреса оперативной памяти.

Таким образом, в регистре 7 адреса микрокоманд сформирован адрес микрокоманды, к которой необходимо вернуться.

Изобретение позволяет получить существенный выигрыш в аппаратуре для процессов, в которых можно выделять одинаковые участки микропрогPBMM.

Для текущего хранения констант, признаков состояний, кодов ошибок используется оставшийся объем памяти.

При этом отсутствуют элементы связи, шифратор, регистр регенерации, блок реверсивных. формирователей тока, блок усилителей чтения, дешифратор адреса оперативной памяти.

Уменьшаются габариты, увеличивается надежность.

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, вход которого соединен " с выходом дешифратора адреса микрокоманд, а выход — со входом регистра микрокоманд, выход кода «оманды которого соединен с информационным входом дешифратора микрокоманд, выход управления регистра микрокоманд соединен с управляющим входом коммутатора, а выход функциональной выборки - с адресным входом регистра адреса микрокоманд, разрядный выход которого соединен со входом дешифратора адреса микрокоманд, а информа:ционный вход регистра адреса микрокоманд соединен с информационным выходом коммутатора, блок оперативной памяти, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, выход функциональной- выборки регистра микрокоманд соединен с

15 адресным входом регистра адреса оперативной памяти, управляющий вход ко-. торого соединен с первым выходом дешифратора микрокоманд, управляющий вход блока оперативной памяти соеди2О нен со вторым выходом дешифратора микрокоманд, третий выход которого соединен с управляющим входом регистра адреса микрокоманд, выход блока памяти микрокоманд соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом блока оперативной памяти, информационный вход которого соединен с информационным выходом

3О коммут ат ар а

Источники информации, принятые во внимание при экспертизе

1. Хассон. Микропрограммное управление, кн ° 1. "Мир", 1973, с. 38 и 43, рис. 2.1, 2.3.

2. Авторское свидетельство СССР

Р 519711, кл. G 06 F 9/16, 1974 (прототип).