Микропрограммное устройствоуправления c коррекцией де- фектных микрокоманд

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИТВЛЬСТВУ

Союз Советскик

Социалистических

Рвслублнк

Опубликовано 23.0281. Бюллетень Й9 7 (51)М. Кл.з

G 06 F 9/22

Государственный комитет

СССР оо делам изобретений

H .открытий (53) УДК 681.32 (088.8) Дата опубликования описания 23,0281

1 .ф (72) Авторы изобретения

А.П. Кондратьев, А.Н, Петушков и A,A ° (71) Заявитель

Цель изобретения — упрощение устройства и повышение быстродействия °

Цель достигается тем, что микропрограммное устройство управления, содержащее основную память, дополнительную память, преобразователь адреса,регистр микрокоманды и узел вы-: работки микроопераций, причем разряды микрокоманды адресного входа устройства соединены с адресным входом основной памяти, выход которой соединен с первым информационным входом регистра микрокоманды, второй информационный вход которого соединен с выходом дополнительной памяти, адресный вход которой соединен с выходом преобразователя адреса, выход. регистра микрокоманды соединен с информационным входом узла выработки микроопераций, выход которого соединен с информационным выходом устройства, дополнительно содержит узел задания режимов и узел анализа адреса, причем группа относительных

Разрядов адресного входа устройства соединена с первой группой адресных входов преобразователя адреса, вторая группа адресных входов которого соединена с группой разрядов номера модуля адресного входа устройства, ИзобРетение относится к электронной вычислительной технике и может, использоваться в электронных вычислительных машинах и в системах цифровой автоматики для цифровой обработки данных.

Известны микропрограммные устройства управления (МУУ), элементами управляющей памяти которых является память, допускающая только считывание информации (1).

Недостатком их является невозможность корректировки микрокоманд в памяти без дорогостоящей физической переделки самой управляющей памяти. 15

Наиболее близким к предлагаемому по технической сущности является микропрограммное устройство управления с коррекцией дефектных микрокоманд, содержащее основную память, дополни- 20 тельную память, преобразователь адреса, состоящий иэ и накопительных элементов, регистр микрокоманды и узел выработки микроопераций (2) °

Недостатком устройства является 25 большой объем оборудования схемы коррекции управляющей памяти, а также снижение быстродействия устройства иэ-за применения этой схемы коррекции. 30 (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

С КОРРЕКЦИЕЙ ДЕФЕКТНЫХ МИКРОКОМАНЦ

807291 разряды номера разряда которого соединены с первым входом узла анализа адреса, второй и третий входы которого соединены соответственно с разрядами номера сегмента и разрядами адреса ячейки адресного входа ус-тройства, выход узла анализа адреса соединен с управляющим входом регистра микрокоманд и с входом узла задания режимов, выход которого соеди нен с управляющим входом узла выработки микроопераций. Кроме того, узел 1О анализа адреса содержит m накопительных элементов, дешифратор и коммутатор, причем управляющий вход коммутатора соединен- с первым входом узла анализа адреса, второй вход которого соединен с входом дешифратора, груп— па выходов которого соединена с управляющим входом соответствующего накопительного элемеHTB, адресные входы . которых соединены с третьим входом узла анализа адреса, выходы накопительных элементов соединены с соответствующим входом коммутатора,. выход которого соединен с выходом узла анализа адреса."

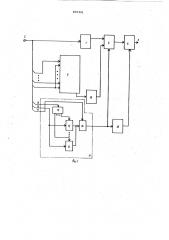

На Фиг. 1 изображена структурная схема устройства; на фиг, 2 — пример конкретной реализации отдельных узлов, .

Устройство микропрограммного уп- 30 равления содержит основную память 1, К-разрядный адресный вход 2,- устройства, регистр 3 микрокоманд, узел 4 выработки микроопераций, информационный выход 5 устройства, преобразователь б адреса, состоящий из п накопительных элементов 7. Совокупность . К разрядов адресного входа 2 устройства скомпаиованы в разрядные группы двояким образом. В(п+1)-кратное разбиение Разрядов адресного входа 2 устройства включена общая группа разрядов номера модуля 8 и и отдельных разрядных групп - групп относительных РазРядов 9 . Кроме того, устройство содержит дополнительную память 10, 45 узел 11 анализа адреса, состоящий иэ

m накопительных элементов 12, дешифРатора 13 и коммутатора 14, при этом использовано трехкратное разбиение разрядов адресного входа 2 устройст- 5Î ва, включающее младшую разрядную группу " Разряды 15 адреса ячейки, промежуточную разрядную группу - разряды

16 номера сегмента и старшую разрядную группу — разряды 17 номера раэ- щ ряда, узел 18 Задания режимов.

Основная память 1 служит для хранения рабочих микрокома"д, Дополнительная память 10, которая по объему значительно меньше основной памяти 1 „60 служит для оперативной записи и хранения скорректированных микрокоманд, которые в основной памяти 1 оказались дефектными, например, из-за ошибок микропрограммирования. 65 преобразователь 6 адреса служит для преобразования адресов дефектных микрокоманд в адреса меньшей разрядности дополнительной гамяти 10. На преобразозаrеля 6 адреса

HHëЯВтсЯ преобразОваннь1е еадреса ка1< дефе1<тных, так и кОрректных микрОкОма нд, 1lpH зт Оъi п реОб ра зОв атель 6 p-реса запрограммирован так. что разным адресам дефектных микрокоманд на его входе соответствуют разные адреса на

eãо выходе, адрес- корректных микрокоманд преобразуются в случайные адреса/ которые совпадают как друг с друго.":,. так и с преобразованными адресами дефектных микрокоманд.

Например, при К=12, п=2 и при использовании накопительных элементов

7 с организацией 256 слов х 4 бита преобразователь 6 адреса с выходом на 8 разрядов реализуется следующим

ОбразОм (фиг. 2). ОбщаЯ группа pc!3= рядов 8 номера модуля адресного входа 2 устройства сод гжит 4 старших разряда адреса и подключена к первой группе адресных входов (к четырем старшим адресным входам) обоих накопительных элементов 7. Две отдельные разрядные группы относительных разрядов 9 содержат также по 4 разряда, причем первая группа — 4 младших, а вторая — 4 промежуточных разряда адреса устройства. Каждая от-. дельная разрядная группа относительных разрядов 9 подключена к второй группе адресных входов (к четырем младшим адресным входам) соответствующих накопительных элементов 7, Такая органиэация преобразователя адреса позволяет адресовать в дополнительной памяти от 10 до 256 дефектных микрокоманд,. причем реализуется однозначное распределение адресов этих

Микрокоманд в накопительных элементах 7.

Узел 11 анализа адрЕса (Фиг. 1) служит для анализа адресов„ поступающих на адресный вход устройства 2, на необходимость коррекций. Каждому адресу основной памяти 1 в накопительных элементах 12 соответствует опноразрядная ячейка памяти, в которой записано 0 или 1 в зависимости от того, является микрокоманда по этому адресу корректной или дефектной соответственно.

Узел 18 задания режимов задает режим рабочего или холостого такта для узла 4 выработки микроопераций в за— висимости or сигнала 0 или 1 на выходе узла 11 анализа адреса.

Устройство работает следующим обра зом.

В каждом рабочем такте иэ основной памяти 1 по адресу, поступающему на адресный вход 2 устройства в регистр

3 микрокоманды считывается рабочая микрокоманда . Узел 4 выработки микроопераций на основе этой микрокоманды формирует управляющие коды микроопе80729 раций, которые поступают на информационный выход 5 устройства.

В каждом так те адрес, пос тупивший на адресный вход 2 устройства, анализируется узлом 11 анализа адреса на наличие адреса дефектной микрокоманды. При обнаружении этого адреса на выходе. узла 11 анализа адреса появляется сигнал, по которому запрещается прием рабочей микрокоманды в регистр 3 микрокоманды из основной памяти 1 и разрешается прием из дополнительной памяти 10. Узел 18 задания режимов по этому сигналу задает режим холостого такта, запрещая выработку микроопераций узлом 4 выраI ботки микроопераций.

В каждом такте адрес, поступивший .на адресный вход 2 устройства, преобразуется преобразователем 6 адреса в адрес дополнительной памяти 10. По каждому преобразованному адресу де- Щ фектной микрокоманды в дополнительной памяти 10 хранится скорректированная микрокоманда.

8 холостом так те скоррек тированная микрокоманда считывается из дополнительной памяти 10 и заносится в регистр 3 микрокоманды. Б следующем такте узлом 18 задания режимов задается обычный режим рабочего такта.

Изобретение обеспечивает повышение быстродействия устройства и уменьшение обьема оборудования.

Быстродействие устройства повышается за счет того, что длительность рабочего такта устройства определяется только быстродействием основной памяти и другими причинами, не связанными со схемами коррекций дефектных микрокоманд.

Только при необходимости коррек- 40 ции дефектной микрокоманды вводится холостой такт на время, требуемое для считывания скорректированной микрокоманды из дополнительной памяти 10.

Я

Формула изобретения

l. Микропрограммное устройство управления с коррекцией дефектных . 50 микрокоманд, содержащее основную память, дополнительную память, преобразователь адреса, регистр микроко» манды и узел выработки .микроопераций, причем разряды микрокоманды адресного входа устройства соединены с адресным входом основной памяти, выход которой соединен с первым информационным входом регистра микрокоманды, второй информационный вход которого соединен с выходом дополнительной памяти, адресный вход которой соединен с выходом преобразователя адреса, выход регистра микрокоманды соединен r информационным входом узла выработки микроопераций, выход которого соединен с информационным выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и повыаения быстродействия, оно дополнительно содержит узел задания режимов и узел анализа адреса, причем группа относительных разрядов адресного входа устройства соединена с первой группой. адресных входов преобразователя адреса, вторая группа адресных входов которого сбединена с группой, разрядов номера, модуля адресного входа устройства, разряды номера разряда которого соединены с первым входом узла анализа адреса, второй и третий входы которого соединены соответственно с разрядами номера сегмента и разрядами адреса ячейки адресного входа устройства, выход узла анализа адреса соединен с управляющим входом регистра микрокоманд и с входом узла задания режимов, выход которого соединен с управляющим входом узла выработки микРоопераций, 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что узел анали" за адреса содержит m накопительных элементов, дешифратор и коммутатор, причем управляющий вход коммутатора соединен с первым входом узла анализа адреса, второй вход которого соединен с входом дешифратора, группа выходов которого соединена с управляющим входом соответствукщего накопительного элемента, адресные входы кото1 ых.соединены с третьим входом узла .анализа адреса, выходы накопительных элементов соединены с соответствующим входом коммутатора, выход которого соединен с выходом узла анализа адреса.

Источники информации, принятые во внимание при экспертизе

1. Хассон С. Микропрограммное устройство управления ° Вып. 1 ° М.,1974.

2. Патент, Франции Р 2328263, кл, 6 11 С 29/ОО, опублик. 1977(пРототип).

807291

Фй2. g

Составитель Г. Пономарева

Техред A.Áàáèíåö корректор О. Билак

Редактор Л. Кеви 1 ираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Заказ 1512

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4