Устройство для решения дифферен-циальных уравнений b частных произ-водных

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических.Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (щ 807319 (61) Дополнительное к авт. свид-ву (51) рА. Кл.з (22) Заявлено 2&0379 (2!) 2743468/18-24

G 06 F 15/328 с присоединением заявки ¹â€” (23) Приоритет

Государственный комитет

СССР по делам изобретений н открытий

{53) УДК 681. 323 (088. 8) Опубликовано 23.0281; Бюллетень № 7

Дата опубликования описания 230281 (72) Авторы изобретения

Б.Г. Фрадкин, И.A. Николаев, В.Е. Проэрров и П.П. Бнбяев

>-" >-НВЯ1С.":.;

Таганрогский радиотехнический институт им. В.Д. Калмыкова (73) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ

УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ

20

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке и конструировании специализированных устройств, предназначенных для решения дифференциальных уравнений в частных производных.

Известно устройство, содержащее для и пространственных координат и резисторов, один иэ выводов которых подключен к общей точке, а другой служит информационным входом для поступления потенциалов соседних элов 1 ()

Недостатком данного устройства является ограниченная точность рещения, определяемая точностью сопротивлений и емкостей.

Наиболее близким по технической сущности к предлагаемому является устройство для моделирования задач теплопроводности, содержащее дварегистра и блок ввода, подключенные 25 выходами к блоку умножения, соединенному выходом через сумматор с входом одного из регистров, подключенного выходом к входу другого регистра и к входу блока коммутацииГ21. 30

Указанное устройство содержит блоки, позволяющие решать линейное уравнение теплопроводности

dUd0 (1) а ах по линейной разностной схеме где А - разностный оператор, соответствующий исходному дифференциальному оператору а () а0 . дх

- шаги сетки по пространственной х и временной t координате)

i n - номера узла стенки по пространственной х и временной t координате, методом простой итерации

u = u + eAu (3)

8 — итерационный параметр; к — номер итерации.

Недостатком устройства является невозможность решения нелинейного уравнения теплопроводности (4)

dt дх dX по нелинейной разностной схеме

807319 ()И+1 ц +." (). ()и х "+" " " " (5)

Ь П

dU в которой для применена аппроксимация вида

2 41+1 г- 1 ) (Ц 01 .г )

Это обуславливает узкий класс решаемых задач, ограниченный только линейными уравнениями теплопроводности.

Цель изобретения — расширение класса решаемых задач.

Поставленная цель достигается тем,что в устройство, содержащее первый блок умножения, два регистра, блок ввода и сумматор, выход .которого соединен с первым входом пер- вого регистра, выход которого соединен с первыми входами первого блока умножения, второго регистра и информационным выходом устройства, тактовый вход устройства соединен с вторыми входами первого и второго регистров, первый информационный вход устройства соединен через блок ввода с вторым входом перного блока .умножения, выход которого соединен с входом сумматора, второй информационный вход устройства соединен с третьими входами первого и второго

1 регистров, выход второго регистра соединен с третьим входом первого блока умножения, введены второй блок умножения, блок деления и блок вычитания, причем первый, второй и третий выходы блока вычитания соединены соответственно с первым и вторым входами второго блока умножения и первым входом блока деления, второй и третий входы которого соединены соответственно с выходом второго блока умножения и тактовым входом устройства, выход блока деления соединен с четвертым входом первого блока умножения, первый и второй входы блока вычитания соединены соответственно с выходами первого регистра и блока ввода.

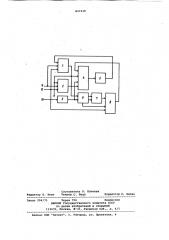

На чертеже представлена структурная схема устройства. устройство содержит перный регистр 1, второй регистр 2, блок 3 ввода, первый блок 4 умножения, сумматор 5, блок б вычитания, второй блок 7 умножения, блок 8 деления.

Выход 9 является выходом устройства, входы 10-12 являются первыми и вторыми информационными и тактовым входами устройства.

Первый .регистр 1 предназначен для хранения на к-ой итерации текущего решения U и записи полученк ного решения U " (3), 5

f0

ЗО

ЯО

60 б5

Второй регистр 2 предназначен для хранения и выдачи начального условия U при итериронании íà и-ом временном слое записи полученного решения по окончании итераций н качестве начального условия для (n+1) -го временного слоя.

Блок 3 ввода служит для ввода в устройство информации о решении в соседних, подключенных к данному устройствах.

Первый блок 4 умножения предназначен.для образования произведений, входящих в итерационную формулу (3) с использонанием разностной схемы (5) .

Сумматор 5 служит для обраэонания решения U"+" путем суммирования произведений, поступающих иэ блока 4 в соответствии с видом формулы (3) и (5), Блок б вычитания предназначен для вычисления разностей, входящих в формулу (6).

Второй блок 7 умножения служит для образования числителя формулы (6) .

Блок 8 деления предназначен для вычисления выражения (6).

Первый информационный вход 10 устройства служит для подключения к устройству выходов 9 соседних устройств при образовании цифровой сетки, Второй информационный вход 11 устройства предназначен для подачи начальных условий, Управляющий вход 12 устройства служит для подачи управляющего сигнала.

Работа устройства происходит следующим образом.

В регистры 1 и 2 по управляющему сигналу на входе 12 с входа 11 записываются начальные условия (U- нулевая итерация решения на первом временном слое и Uo — решение на нулевом временном слое, известное из постановки задачи) . С выхода первого регистра 1 U поступает на

1,О первый вход блока б вычитания, на . второй вход которого приходят передаваемые блоком 3 ввода

1,о с первого информационного входа 10, соединенного с выходом 9 соседних устройств, На выходах блока б вычитания образуются разности (U -U )

1,О 1,О

q,О 1,О 1+1 1 и (U„. -U„- 1), поступающие на входы второго блока 7 умножения и разность (О„-+ 1-()1. 1), поступающая на первый вход блока 8 деления в качестве делителя, на второй вход которого приходит в качестве делимого произведение . (Ua+„-0ф г ) (Uq -U1o ) выхода второго блока 7 умножения.

Таким образом, с выхода блока 8 деления значение выражения (б) поступает на четвертый вход первого блока 4 умножения, где последователь807319 но умножается на величины U U

1 Р.1

U„-, поступающие íà его первый, второй, третий, входы С выходов. регистров 1 и 2 и блока 3 ввода, на коэффициенты разностной схемы (5) и итерационной формулы (3), являющиеся известными функциями от %, Т, Ю и хранимые н самом блоке 4. Сумматор 5 суммирует полученные в первом блоке 4 умножения произведения, образующие согласно (5) и (3), первую итерацию решения на первом временном слое U„. êîòoðàÿ записы- вается по первому входу в первый регистр 1, При решении линейных уравнений (1) по разностной схеме (2) методом итерации (3) блок 8 деления настраивается по управляющему сигналу, поступающему на его третий вход с входа 12 устройства, на генерацию (1) и вместо схемы (5) ре ализуется схема (2). Аналогично происходит работа .устройства На второй и т.д.к-ой итерации, при этом определяются значения U; и т.д, U." . По окончании итерационного про1 цесса при поступлении соответствую-. щего управляющего сигнала на вход

12 информация иэ первого регистра 1 переписывается по первому входу во второй регистр ?, являясь величиной т,е, начальным условием для второго временного слоя, на котором „„

2> I 2,2 1 определяется U„, U;, и т.д. U„

На последующих временных слоях работа устройства происходит аналогичным образом.

Реализацию предлагаемого изобретения осуществляют на микросхемах серии К 155.

Использование н устройстве блока вычитания,. соединенного входами с выходами первого регистра и блока ввода, а выходами с входами введенных второго блока умножения и блока деления, подключенного выходом к первому блоку умножения, выгодно отличает данное устройство от известного, так как позволяет решать важный класс нелинейных уравнений (4), характеризующих, например, актуальные задачи моделирования йриборов с зарядовой связью, что существенно расширяет класс решаемых задач, ограниченных только линейными уравнениями.

Формула изобретения

Устройство для решения дифференциальных уравнений в частных производных, содержащее первый блок умножения, два регистра, блок ввода и .сумматор, выход которого соединен с первым входом первого регистра, выход которого соединен с первыми входами первого блока умножения, второго регистра и информационным выходом устройства, тактовый вход устройства соединен с вторыми нходами первого и второго регистров,.первый информационный вход устройства соединен через блок ввода с вторым- входом пер20 ного блока умножения, выход которого соединен с входом сумматора, второй информационный вход устройства соединен с третьими входами первого и второго регистров, выход второго регистра соединен с третьим входом первого блока умножения, о т л. ич а ю щ е е с я тем, что, с целью расширения класса решаемых задач, в него введены второй блок умножения, блок деления и блок вычитания, причем первый, второй и третий выходы блока вычитания соединены соответственно с первым и вторым входами второго блока умножения и первым . входом блока деления, второй и третий входы которого соединены соответственно с ныходом второго блока умножения и тактовым входом устройстна, выход блока деления соединен с четвертым входом перного блока

40 умножения, первый и второй входы блока вычитания соединены соответстненно с выходами первого регистра и блока ввода.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 583455 кл. G 06 F 15/32 1977.

2. Авторское свидетельство СССР

9 373735, кл. G 06 F 15/32, 1973 (прототип).

807319

Составитель Н. Палеева

Редактор Л. Кеви Техред С. Беца Корректор О. Билак

Заказ 294/75 Тираж 756 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4