Аналоговый интегратор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<щ 807326

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву— (22) Заявлено 050379 (21) 2733417/18-24 (51)М. Кл. с присоединением заявки ¹

06 G 7/186 осударствеииый комитет

СССР ио делам изобретеиий и открытий (23) Приоритет (53) УДК 681. 335 (088. 8) Опубликовано 230281. Бюллетень И9 7

Дата опубликования описания 23.0281

А .. Хайтйй " о% Я

Pg ) i,7, òм »

1 " . (72) Авторы изобретения

A.E,Âîëûíñêèé, С.A.Ðà÷èí, A.A.Ñìèðíîâ и (71) Заявитель (54) АНАЛОГОВЫЙ ИНТЕГРАТОР

15

30

Изобретение относится к аналоговой вычислительной технике и может быть использовано в аналоговых моделирующих устройствах, а также в электронных устройствах различного назначения.

Известны аналоговые интеграторы на операционных усилителях, снабжен .ные электромеханическим ключом разряда интегрирующего конденсатора, в которых инвертирующий вход операционного усилителя через параллельно включенные интегрирующий конденсатор и ключ разряда связан с выходом данного усилитеЛя (1), Недостаток подобных интеграторов обусловлен низким быстродействием электромеханического ключа разряда интегрирующего конденсатора, может быть устранен путем замены данного электромеханического ключа электрон ным элементом, Известен аналоговый интегратор, содержащий операционный усилитель, в цепь обратной связи которого вклю чен конденсатор с электронным ключом разряда (2).

Однако электронные ключи, по сра нению с электромеханическими ключами, обладают меньшим сопротивлением в разомкнутом состоянии и поэтому использование в цепи, параллельной интегрирующему конденсатору, электронных ключей вызывает погрешность из-за паразитного тока, протекающего через разомкнутый ключ, Цель изобретения — повышение точности аналогового интегратора.

Поставленная цель достигается тем, что в аналоговый интегратор, содержащий операционный усилитель,. между входом и выходом которого включен интегрирующий конденсатор,первый ключ, вход которого является входом аналогового интегратора, .а выход подключен к входу операционного

1 усилителя и входу второго ключа, и блок управления, соединенный с управляющими входами первого и второго ключей, введены запоминающий конденсатор и дополнительный ключ, включенный между выходом второго ключа и выходом операционного усилителя, между общим выводом второго и дополнительного ключей и шиной нулевого потенциала включен запоминающий конденсатор, а управляющий вход дополнительного ключа соединен с управляющим входом второго ключа. При этом дополнительный ключ:содержит

807326

5 !

О

Фсрмула изобретения

d0

65 три коммутирующих элемента, например, МДП-транзисторы и инвертор, при- чем первый и второй коммутирующ:е элементы соединены последовательно и включены мужду входом и выходом дополнительного ключа, общий вывод первого и второго коммутирующих .элементов через третий коммутирующий элемент соединен с шиной нулевого потенциала, управляющий вход третьего коммутирующего элемента через инвертор подключен к управляющим входам первого и второго коммутирующих элементов, являющимся управляющим входом дополнительного ключа.

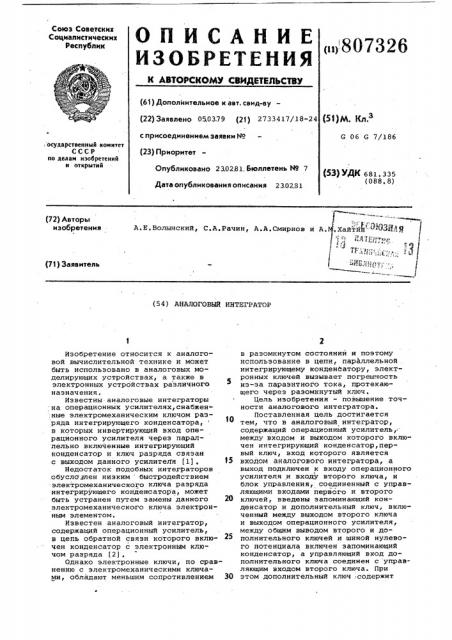

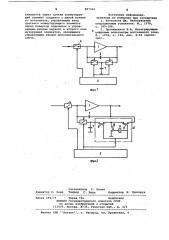

На фиг. 1 приведена структурная схема предлагаемого интегратора; на фиг. 2 — ее вариант, отличающийся выполнением дополнительного клю. ча.

Аналоговый интегратор содержит операционный усилитель 1, интегрирующий конденсатор 2, блок 3 управления, первый 4 и второй 5 ключи, дополнительный ключ 6 и запоминающий конденсатор 7.

Интегратор работает следующим образом.

По командам блока 3 управления в режиме сброса размыкается ключ 4 и замыкаются ключи 5 и 6, обеспечивая быстрый разряд конденсатора 2,при этом на выходе операционного усилителя 1 присутствует напряжение, равное напряжению смещения, которое запоминается конденсатором 7 до следующего сброса интегратора. По окончании команды "Сброс" блок 3 разрешает интегрирование входного сигнала: по сигналам управления ключи 5 и 6 размыкаются и замыкается ключ 4, при этом на обоих выводах разомкнутого ключа 5 присутствуют одинаковые потенциалы, обеспечивая в режиме интегрирования отсутствие паразитного тока через этот ключ.

Ключ 6 может быть выполнен в виде совместного включения трех коммутирующих элементов, например

МДП-транзисторов, причем первый 8 и второй 9 коммутирующие элементы включены последовательно, общий вывод элементов 8 и 9 через третий коммутирующий элемент 10 связан с шиной нулевого потенциала, свободные. выводы элементов 8 и 9 служат входом и выходом ключа 6 управляющий вход данного ключа соединен с управляющими входами элементов 8 и 9, а через вспомогательный инвертор 11 связан с управляющим входом элемента

10.

В этом варианте интегратора в режиме интегрирования ослабляется влияние выходного напряжения усилителя

1 на напряжение конденсатора 7 в . К р 9 Раэ i где Rgp о кр и R9 рр» сО противления элементов 10 и 9 соответственно в проводящем и разомкнутом состояниях. Это связано с тем, что если ключ 6 выполняется на одиночном МДП-транзисторе, то заряд паразитным током конденсатора 7 через разомкнутый ключ 6 выходным напряжением усилителя 1 приводит к появлению разности потенциалов На выводах ключа 5, что в свою очередь, приводит к увеличению паразитного тока через упомянутый ключ.

В режиме интегрирования блок 3 выключает элементы 8 и 9 и с помощью инвертора 11 включает элемент 10, а в режиме "Сброс" состояния данных коммутирующих элементов изменяются на противоположные и дальнейшая работа аналогична работе основного интегратора.

Таким образом, предлагаемый интегратор позволяет сохранить присущее известному высокое быстродействие, однако, в отличие от него обладает повышенной точностью, обусловленной отсутствием паразитных токов разрядов интегрирующего конденсатора через сопротивление закрытого ключа сброса. Последнее обстоятельство выгодно отличает предлагаемый аналоговый интегратор от известных, поскольку позволяет расширить сферу его возможного применения..

1. Аналоговый интегратор, содержащий операционный усилитель, между входом и выходом которого включен интегрирующий конденсатор, первый ключ, вход которого является входом аналогового интегратора, а выход подключен к.входу операционного усилителя и входу второго ключа, и блок управления, соединенный с управляющими входами первого и второго ключей,отличающийся тем, что, с целью повышения точности интегрирования, в него введены запоминающий конденсатор и дополнительный ключ, включенный между выходом второго ключа и выходом операционного усилителя, между общим выводом второго и дополнительного ключей и шиной нулевого потенциала включен запоминающий конденсатор, а управляющий вход дополнительного ключа соединен с управляющим входом второго ключа.

2. Аналоговый интегратор -по п.1, отличающийся тем, что,дополнительный ключ содержит три коммутирующих элемента, например, МДП вЂ” транзисторы и инвертор, причем первый и второй коммутирующие элементы соединены последовательно и включены между входом и выходом дополнительного ключа, общий вывод первого и второго коммутирующих

807326

Фиа 1 фиа2

Составитель С. Белан

Редактор Л, Кеви Техред С. Беца

Корректор Н. Григорук

Заказ 294/75 Тираж 756 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 элементов через третий коммутирующий элемент соединен с шиной нулево го потенциала, управляющий вход третьего коммутирующего элемента через инвертор подключен к управляющим входам первого и второго коммутирующих элементов, являющимся управляющим входом дополнительного ключа.

Источники информации, принятые во внимание при экспертизе

1. Рутковски Дж. Интегральные операционные усилители, М., 1978, с. 185-186.

2. Прянишников В.A. Интегрирующие цифровые вольтметры постоянного тока..

Л., 1976., с. 192, рис. 4-33 (прототип).